# High Frequency Thin Film Magnetics-on-Silicon with Improved Inductance and Resistance

Martin Sittner, Mahmoud Shousha, Martin Haug

MagI³C PU, Würth Elektronik eiSos Group, Munich, Germany

martin.sittner@we-online.de, mahmoud.shousha@we-online.de, and martin.haug@we-online.de

## 1. Background

In the electronics industry there is a significant trend towards miniaturization of electronic devices. At the same time, system functionality should continue to be guaranteed or improved. To support the increasing level of integration, magnetics-on-silicon is introduced [1]. The main goal of this paper is to show improvement compared to previous works [1] by increasing the magnetic core and copper thicknesses.

#### 2. Method

The approach is to use magnetics on silicon technology based on a thin-film fabrication process known from CMOS technology. The fabrication is done by a basic lithography process combining plasma deposition and electroplating processes. To improve the performance of the magnetics the existing 15µm copper layers as well as the 4.5µm magnetic core are increased to 25µm copper and 6µm core. By using a special CZT magnetic core material the BH loop is optimized to make it compatible with high-frequency applications. With the narrow BH loop, the core AC losses can be kept low at high frequencies enabling this technology to operate in applications with hundreds of megahertz.

## 3. Results

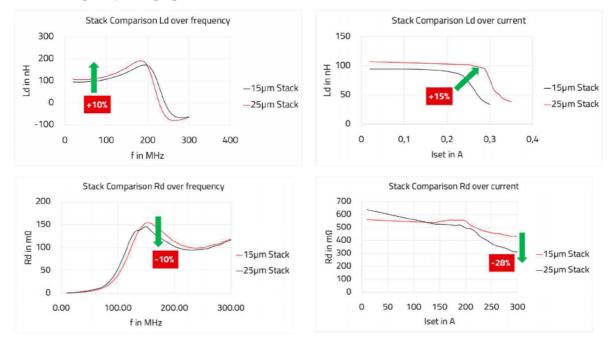

The increased thicknesses result in improved inductance. Comparing the same design with both stacks, the final test on the wafer level shows a maximum improvement in inductance of 15% for the biased test and single frequency (f=30MHz; DC bias = 0-340mA) improvement up to 10% for an unbiased frequency sweep up to 300MHz.

Figure 1: Comparison 15 µm stack vs. 25 µm stack: Unbiased frequency sweep (left), current sweep (right).

The overall resistance is decreased with high frequency (up to -10% at f > 150MHz) as well as for biased situation. At 300mA the resistance is decreased by 28%. Major differences can be found looking at the RDC. For the shown test structure measurements the RDC value of the 15 $\mu$ m stack sample is 310m $\Omega$  whereas the 25 $\mu$ m stack achieved an RDC value of 203m $\Omega$ . This RDC reduction of

000351

34.5% matches to the 40% Cu thickness difference of both stacks. Figure 1 shows the stack comparison.

The flexible design and packaging approaches allows for usage in power applications such as common DC/DC converters or gate drive supplies as well as signal applications like high speed signal lines (i.e. USB 3.1). Contrary to the broad range of possible applications, technology limitations can be seen as listed in table 1:

Table1: Technology limitations.

| Parameter         | Microinductor                                      | Microtransformer                      |

|-------------------|----------------------------------------------------|---------------------------------------|

| Inductance        | nH range (no economic use case with L in μH range) |                                       |

| Operation current | < 3A (due to RDC)                                  |                                       |

| Frequency         | Below 1GHz (high power los                         | sses in silicon substrate above 1GHz) |

Frequency limitation for the current technology comes from the use of undoped silicon as the substrate. In the GHz range, the power loss within the substrate material needs to be taken into account. Several challenges for changing to different substrate material become apparant. One possible option is to use

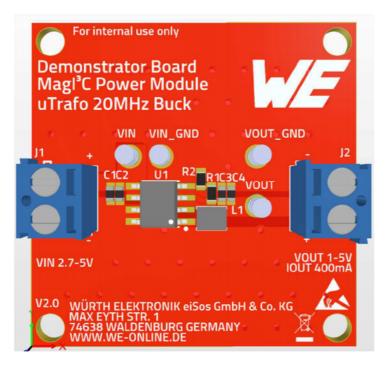

Figure 2: 20MHz prototype using a thin film magnetic-on-silicon device

glass as a substrate material since the resistivity is higher than undoped silicon. The downside of using glass is the higher complexity in production processing such as optical issues during packaging. Additionally, wafers with glass substrate are commonly 7" wafer whereas the production process for the introduced technology is based on a 12" wafer. Another option is to change to doped silicon with high resistivity. The disadvantage of the specially high resistive material is the higher production cost leading to an uneconomical wafer cost and therefore to a non-competitive pricing of the final component. The technology's major advantage comes to play operating in high frequency applications. The described core material is able to efficiently operate in the range of up to several hundreds of megahertz. This enables the component values and sizes in power applications to be significantly miniaturized while preserving signal integrity in signal applications since the core material isn't running

## 24th European Microelectronics Packaging Conference

in saturation. A prototype was built and tested to prove the effectiveness of the presented thin-film silicon-based magnetic technology by implementing the magnetic device in a high switching frequency non-isolated DC/DC converter meant to be used as an auxiliary supply for power SIP and power SOC applications. The prototype consists of the SC220 synchronous step-down regulator IC which implements an internal 20MHz oscillator block, external input and output capacitors from the Würth Elektronik portfolio ( $2x\ 1\mu F\ 885012206002$  for both input and output capacitors), the resistive feedback divider (set to 2.5V) as well as the silicon-based magnetic device. The converter can operate from  $2.7V\ -5.5V$  with an adjustable output voltage from  $1V\ -5V$ . Maximum load current is 400mA which fits for auxiliary supply applications. Figure 2 shows the build prototype PCB. The regulator IC requires a minimum external inductance of 220nH. Table 2 shows the magnetic device specifications:

Table2: Microtransformer specifications.

| Parameters | Values                                             |  |

|------------|----------------------------------------------------|--|

| L          | 360nH                                              |  |

| Rdc        | 1.65 Ω                                             |  |

| Q-factor   | 21.4 at 20MHz                                      |  |

| Isat       | 450 mA                                             |  |

| Chip Size  | 3.2 x 2.5 (corresponding to 1210 SMD package size) |  |

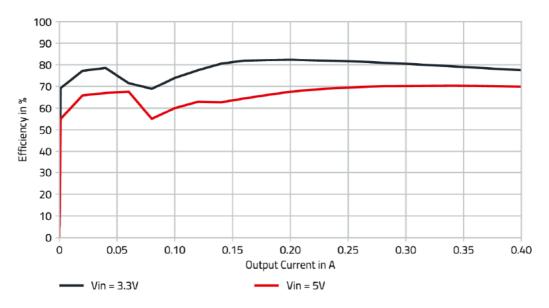

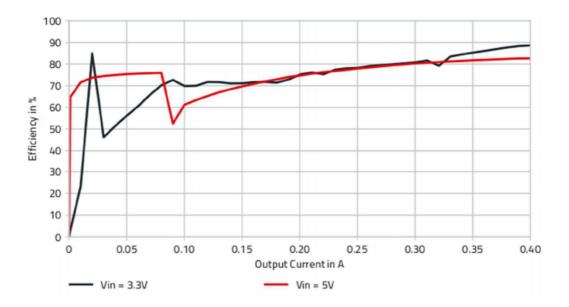

At room temperature the converter can achieve an efficiency of up to 82.3% converting 3.3V to 2.5V.

Figure 3: Efficiency at  $T_A = 25$ °C

While converting 5V to 2.5V a peak efficiency of 70% is achieved. These results can be seen in figure 3 The thin film magnetic technology is already qualified according to AEC-Q 200 grade 1 which ensures operation for a wide temperature range from -40°C to 125°C. Since the IC is only specified

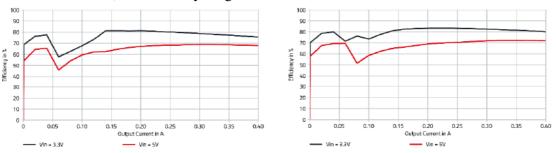

from -40°C to 85°C, the efficiency is again measured at these borders. The attained

Figure 4a: Efficiency at  $T_A = 85^{\circ}C$

Figure 4b: Efficiency at  $T_A = -40$ °C

efficiency can be seen in Figures 4a and 4b. The lack of significant deviation in efficiency shows the temperature robustness of the magnetic component. To validate these results, the shown prototype in Figure 2 was adjusted by replacing the microinductor with a power molded chip inductor from Würth Elektronik WE-PMCI series. The inductor is also packaged in a 1210 SMD package. Figure 5 shows the measured efficiency at room temperature.

Figure 5: Efficiency at  $T_A = 25$ °C

It can be noted from Figure 5 that despite the fact that these inductors have higher inductance and better DCR, the efficiencies of both prototypes are very similar with even higher overall efficiency of the prototype with the thin-film magnetic working with 3.3Vin. For the discussed targe application space is the biggest constrain. Therefore, a magnetic component with little space consumption by keeping decent efficiency to avoid the need for external heat sinking as well as additional cooling cost. The implemented thin-film magnetic chip size reflects the standard SMD 1210 package size but with a reduced height of 200µm height. In comparison, an inductor with a 1210 package typically has a height of 1mm. Therefore, with the shown thin-film magnetic device a chip volume reduction of 80% can be achieved.

#### 4. Discussion

As the packaging approach for this magnetics type is highly flexible, there are myriad possibilities for integration such as WLCSP for PCB soldering and bare dies for wire bonding or embedding.

# 24th European Microelectronics Packaging Conference

Experimental experience shows that as of today WLCSP integration with a given solder ball diameter of 230µm is more suitable for the prototyping phase since handling within production processes turns out to be difficult resulting in a low assembly yield. Therefore, for mass volume production, bonding or embedding is recommended.

## 5. Conclusion

This paper shows improvement to the already achieved results. Improving inductance and resistance is a key enabler for the adoption of this technology within a wider range of applications. Further, a fully functioning DC/DC converter prototype operating with very high frequency (20MHz) is described and measured proving the technology's high frequency capability. It's proven that the magnetic component is able to handle a broad temperature range. The converter can operate with efficiency over 82% range with a magnetic component volume reduction of 80%.

## 6. References

[1] S. L. Selvaraj *et al.*, "On-Chip Thin Film Inductor for High Frequency DC-DC Power Conversion Applications," *2020 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2020, pp. 176-180, doi: 10.1109/APEC39645.2020.9124544.