# Impact of Cu Protrusion on Connection Resistance in Hybrid Bonding of Via-middle TSV Wafer

Naoya Watanabe<sup>1\*</sup>, Hiroshi Yamamoto<sup>2</sup>, and Takahiko Mitsui<sup>2</sup>

Device Technology Research Institute, National Institute of Advanced Industrial Science and Technology, AIST Tsukuba Central 1, 1-1-1 Umezono, Tsukuba-shi, Ibaraki 305-8560, Japan

<sup>2</sup>Okamoto Machine Tool Works, Ltd.,

2993 Gobara, Annaka-shi, Gunma 379-0135, Japan

\*Phone: +81-29-849-1463; Fax: +81-29-862-6511

Email: naoya-watanabe@aist.go.jp

#### **Abstract**

In this study, we investigated the impact of Cu protrusion on the connection resistance as detailed data regarding the hybrid bonding of the via-middle through-silicon-via (TSV) wafer. After several Cu TSV wafers and Cu electrode wafers with different amounts of Cu protrusion were prepared and bonded via a surface-activated bonding method using ultrathin Si films, the connection resistance of bonded wafers (that is, the sum of the TSV, Cu electrode, and interface resistances) was evaluated via four-terminal measurements. The results demonstrate that the amount of Cu protrusion is a crucial parameter for the hybrid bonding of via-middle TSV wafers with ultrathin Si films, and an electrical connection between the TSV and Cu electrode can be achieved without heat treatment by adjusting the Cu protrusion.

## **Key words**

via-middle, through-silicon via (TSV), direct Si/Cu grinding, hybrid bonding

### I. Introduction

With the slowing of Moore's law, three-dimensional integrated circuits (3D-ICs) with through-silicon vias (TSVs) [1-6] have emerged as viable solutions for realizing high-speed, extremely compact, and highly functional electronic systems. 3D-ICs are being increasing accepted in some electronic systems. However, further reduction of TSV formation costs, TSV miniaturization, and TSV yield improvement are required to apply 3D-IC technology to many electronic systems. Among the various TSV formation processes, the via-middle Cu-TSV process can effectively reduce the TSV size and increase the TSV yield owing to the ease of forming (1) small TSVs, and (2) electrical contact between the TSVs and multilevel interconnects. However, TSV breakage or contact failure may occur if the height variation of the TSV, revealed on the rear side of the wafer, is large.

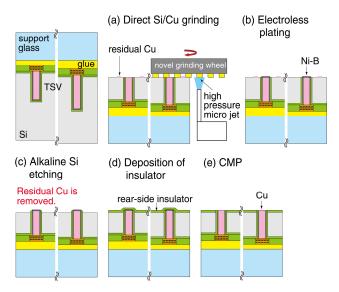

In a previous work, we proposed a Cu-TSV reveal process comprising direct Si/Cu grinding and residual metal removal [7-9] (Fig. 1), to overcome this problem. First, direct Si/Cu grinding was performed using a novel vitrified grinding wheel and in-situ cleaning of the grinding wheel using a high-pressure microjet (HPMJ). Owing to the inelastic

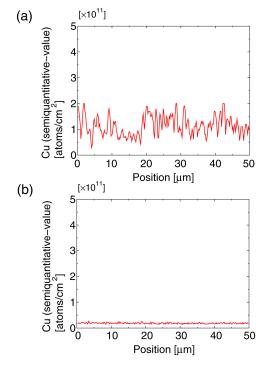

porous structure and in-situ cleaning of the grinding wheel, the burning and smearing of Cu were suppressed during grinding, and the leveling and revealing of TSVs were realized. Subsequently, the residual metal (Cu) on the Si surface was removed via electroless Ni-B plating and alkaline Si etching. Low-temperature chemical vapor deposition (CVD) was performed to create the rear-side insulator. Finally, the top-surface insulator of the TSV was removed through chemical-mechanical polishing (CMP). Through this process, we successfully revealed a via-middle Cu-TSV without TSV breakage or contact failures. Time-offlight secondary ion mass spectrometry (TOF-SIMS) showed that the Cu contaminant concentration in the Si region near the revealed TSV was below 5 × 10<sup>10</sup> atoms/cm<sup>2</sup> (see Fig. 2). In addition, by introducing surface-activated bonding method using Si ultrathin films [10], we realized hybrid bonding of the via-middle Cu-TSV wafer (fabricated using this Cu-TSV reveal process) [11,12].

In this study, we investigate the impact of the Cu protrusion on the connection resistance for performing a detailed analysis of the hybrid bonding of via-middle Cu-TSV wafers. We show that the amount of Cu protrusion is a crucial parameter that affects the hybrid bonding of via-

middle TSV wafers with ultrathin Si films, and that an electrical connection between the TSV and Cu electrode can be achieved without heat treatment by adjusting the Cu protrusion.

Figure 1: Cu-TSV reveal process comprising direct Si/Cu grinding and residual metal removal.

Figure 2: Example of the measurement result of the Cu contaminant concentration in the Si region near the revealed TSV: (a) after direct Si/Cu griding step, (b) after residual metal removal step.

## II. Experiment

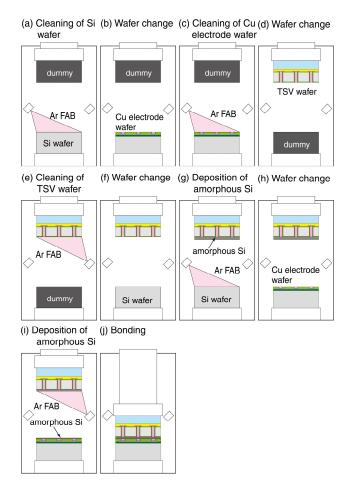

Figure 3 shows the experimental procedure for investigating the impact of the Cu protrusion on the connection resistance. First, TSV wafers of diameter 200 mm were fabricated via deep Si etching using SF<sub>6</sub>, O<sub>2</sub>, and Ar gases. This was followed by CVD using tetraethyl orthosilicate and O2 gases, barrier seed layer (Ti-Cu layer) deposition, bottom-up Cu electroplating, CMP, and Ti-Al wiring formation. The diameter and depth of the TSVs were 5.5 and 33 µm, respectively. Subsequently, the edges of the TSV wafer were trimmed. The width and depth of the trimmed Si were 1.5 and 0.15 mm, respectively. After the support glass was bonded with glue, direct Si/Cu grinding was performed. To avoid the burning and smearing of Cu after direct Si/Cu grinding, we used a novel vitrified bond grinding wheel and performed in-situ cleaning of the grinding wheel using a HPMJ. The grit numbers of the prepared grinding wheels were #6,000 and #30,000. Thus, TSVs of diameter 5.5 μm were revealed on the rear side of TSV wafer. The wafer thickness after direct Si/Cu grinding was approximately 22 um. The slight Cu contamination in the Si region between the TSVs was reduced through electroless Ni-B plating and alkaline etching of Si. Electroless Ni-B plating was performed using an NiSO<sub>4</sub>-based solution, at a plating temperature of 65 °C. Alkaline etching was performed using a tetramethylammonium-hydroxide-based solution at a temperature of approximately 70 °C, and the thickness of the etched Si was approximately 800 nm. Subsequently, a rearside insulator was deposited via low-temperature CVD (stage temperature: 80 °C). Precise CMP of the TSV and Cu electrode wafers was then performed. To investigate the impact of the Cu protrusion on the connection resistance. TSV and Cu electrode wafers, each with different Cu protrusions (TSV wafers 1 and 2 and Cu electrode wafers 1 and 2), were used. The Cu protrusions of TSV wafers 1 and 2 were 4.0 and 7.7 nm, respectively, while those of Cu electrode wafers 1 and 2 were 4.8 and 29 nm, respectively. Then, hybrid bonding was performed via surface-activated bonding with ultrathin Si films, and two bonded samples were fabricated. Bonded sample 1 was fabricated by bonding TSV wafer 1 with Cu electrode wafer 1, and bonded sample 2 was fabricated by bonding TSV wafer 2 with Cu electrode wafer 2. The hybrid bonding conditions were as follows: temperature: 25 °C, pressing load: 100 kN. vacuum degree: less than 10<sup>-5</sup> Pa, and bonding machine: Bond Meister MWB-12-ST (Mitsubishi Heavy Industries Machine Tool Co., Ltd.). The detailed sequence of hybrid bonding is presented in Fig. 4. Subsequently, the support glass was debonded. Finally, four-terminal measurements were performed, in which the sum of the TSV, Cu-electrode, and interface resistances was obtained as the connection resistance between the two wafers.

Figure 3: Experimental procedure. By bonding and comparing two types of TSV wafers and Cu electrode wafers with different Cu protrusions, the impact of the Cu protrusions on the connection resistance after hybrid bonding was investigated.

Figure 4: Hybrid bonding sequence. After the surface of the Si wafer was cleaned, the Si wafer was transferred to another chamber. The surface of the Cu electrode wafer was also cleaned, and the wafer transferred to another chamber. The rear surface of the TSV wafer was also cleaned. Subsequently, amorphous Si was deposited on the TSV wafer by irradiating Ar-fast atom beam (FAB) onto the Si wafer, and amorphous Si was deposited on the Cu electrode wafer by irradiating Ar-FAB onto the TSV wafer. Finally, the two wafers were bonded.

## III. Results and Discussion

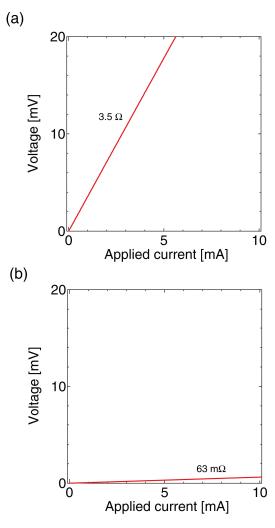

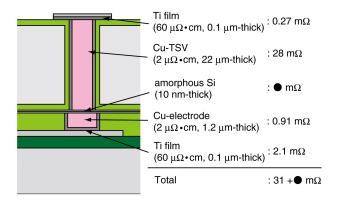

Figure 5 shows the four-terminal measurement results of the two bonded samples. In bonded sample 1, the connection resistance (i.e., the sum of the TSV, Cu electrode, and interface resistances) is approximately 3.5  $\Omega$ . Meanwhile, the connection resistance is less than 100 m $\Omega$  and close to the calculated resistance of the four-terminal measurement pattern (Fig. 6) in bonded sample 2. This result demonstrates that the amount of Cu protrusion is a crucial parameter that affects the hybrid bonding of via-middle TSV wafers.

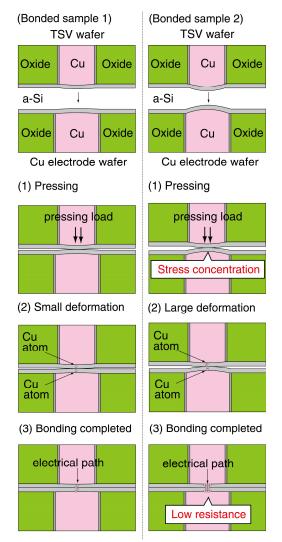

Based on the results illustrated in Fig. 5, we estimated the reason for the difference between the connection resistance

values of bonded samples 1 and 2. Figure 7 presents an estimated diagram of the bonding behavior in bonded samples 1 and 2. In the case of bonded sample 1, as the protrusion of amorphous Si (protrusion of Cu) is small, large deformation does not occur. Consequently, the number of Cu atoms forming electrical paths decreases, and the connection resistance is high. On the other hand, for bonded sample 2, large deformation occurs because the pressing load is concentratedly applied to the protrusion of amorphous Si (protrusion of Cu). Resultantly, more Cu atoms form electrical paths in the amorphous Si, and their bond becomes stronger. As a result, the connection resistance becomes low, even without performing post-bonding annealing.

Figure 5: Results of four-terminal measurements: (a) bonded sample 1. (b) bonded sample 2. In the bonded sample 1, the connection resistance was about 3.5  $\Omega$ . On the other hand, the connection resistance was less than 100 m $\Omega$  in the bonded sample 2.

Figure 6: Resistance calculation result for the four-terminal measurement pattern.

Figure 7: Schematic of the estimated bonding behavior in bonded samples 1 and 2.

## IV. Conclusion

In this study, we investigated the impact of Cu protrusion on the connection resistance as detailed data regarding the hybrid bonding of the via-middle Cu-TSV wafer. Several Cu TSV wafers and Cu electrode wafers with different amounts of Cu protrusion were prepared and bonded via surfaceactivated bonding using ultrathin Si films, and the connection resistance of boned wafers was measured. When the Cu protrusion of the TSV wafer was 4.0 nm and that of the Cu electrode wafer was 4.8 nm, the connection resistance was several  $\Omega$ . On the other hand, when the Cu protrusion of the TSV wafer was 7.7 nm and that of the Cu electrode wafer was 29 nm, the connection resistance was less than 100 m $\Omega$ . The results demonstrate that the amount of Cu protrusion is a crucial parameter for the hybrid bonding of via-middle TSV wafers with ultrathin Si films, and an electrical connection between the TSV and Cu electrode can be achieved without heat treatment by adjusting the Cu protrusion.

## References

- M. Koyanagi, Y. Nakagawa, K. W. Lee, T. Nakamura, Y. Yamada, K. Inamura, K. T. Park, and H. Kurino, "Neuromorphic Vision Chip Fabricated Using Three-Dimensional Integration Technology," ISSCC Dig. Tech. Papers, 2001, pp. 270–271.

- [2] N. Watanabe, I. Tsunoda, T. Takao, K. Tanaka, and T. Asano, "Fabrication of Back-Side Illuminated Complementary Metal Oxide Semiconductor Image Sensor Using Compliant Bump," Jpn. J. Appl. Phys., vol.49 (2010) 04DB01.

- [3] D. H. Kim, K. Athikulwongse, M. Healy, M. Hossain, M. Jung, I. Khorosh, G. Kumar, Y. J. Lee, D. Lewis, T. W. Lin, C. Liu, S. Panth, M. Pathak, M. Ren, G. Shen, T. Song, D. H. Woo, X. Zhao, J. Kim, H. Choi, G. Loh, H. H. Lee, and S. K. Lim, "3D-MAPS: 3D Massively Parallel Processor with Stacked Memory," ISSCC Dig. Tech. Papers, 2012, pp.188–189.

- [4] T. Haruta, T. Nakajima, J. Hashizume, T. Umebayashi, H. Takahashi, K. Taniguchi, M. Kuroda, H. Sumihiro, K. Enoki, T. Yamasaki, K. Ikezawa, A. Kitahara, M. Zen, M. Oyama, H. Koga, H. Tsugawa, T. Ogita, T. Nagano, S. Takano, and T. Nomoto, "A 1/2.3inch 20Mpixel 3-Layer Stacked CMOS Image Sensor with DRAM," ISSCC Dig. Tech. Papers, 2017, pp.76–78.

- [5] D. U. Lee, H. S. Cho, J. Kim, Y. J. Ku, S. Oh, C. D. Kim, H. W. Kim, W. Y. Lee, T. K. Kim, T. S. Yun, M. J. Kim, S. Lim, S. H. Lee, B. K. Yun, J. I. Moon, J. H. Park, S. Choi, Y. J. Park, C. K. Lee, C. Jeong, J. S. Lee, S. H. Lee, W. S. We, J. C. Yun, D. Lee, J. Shin, S. Kim, J. Lee, J. Choi, Y. Ju, M. J. Park, K. S. Lee, Y. Hur, D. Shim, S. Lee, J. Chun, and K. W. Jin, "A 128Gb 8-High 512GB/s HBM2E DRAM with a Pseudo Quarter Bank Structure, Power Dispersion and an Instruction-Based At-Speed PMBIST," ISSCC Dig. Tech. Papers, 2020, pp.334–336.

- [6] M. J. Park, H. S. Cho, T. S. Yun, S. Byeon, Y. J. Koo, S. Yoon, D. U. Lee, S. Choi, J. Park, J. Lee, K. Cho, J. Moon, B. K. Yoon, Y. J. Park, S. Muk Oh, C. K. Lee, T. K. Kim, S. H. Lee, H. W. Kim, Y. Ju, S. K. Lim, S. G. Back, K. Y. Lee, S. H. Lee, W. S. We, S. Kim, Y. Choi, S. H. Lee, S. M. Yang, G. Lee, I. K. Kim, Y. Jeon, J. H. Park, J. C. Yun, C. Park, S. Y. Kim, S. Kim, D. Y. Lee, S. H. Oh, T. Hwang, J. Shin, Y. Lee, H. Kim, J. Lee, Y. Hur, S. Lee, J. Jang, J. Chun, and J. Cho, "A 192-Gb 12-High 896-GB/s HBM3 DRAM with a TSV Auto-Calibration Scheme and Machine-Learning-Based Layout Optimization," ISSCC Dig. Tech. Papers, 2022, p. 444.

- [7] N. Watanabe, M. Aoyagi, D. Katagawa, T. Bandoh, and E. Yamamoto, "Novel Through Silicon Via Exposure Process Comprising Si/Cu

- Grinding, Electroless Ni-B Plating, and Wet Etching of Si," Jpn. J. Appl. Phys., vol. 53 (2014) 05GE02.

- [8] N. Watanabe, M. Aoyagi, D. Katagawa, T. Bandoh, T. Mitsui, and E. Yamamoto, "Small-Diameter TSV Reveal Process Using Direct Si/Cu Grinding and Metal Contamination Removal," Proceedings of 3D Systems Integration Conference (3DIC), 2014, pp. 03-1–5.

- [9] N. Watanabe, M. Aoyagi, D. Katagawa, T. Bandoh, T. Mitsui, and E. Yamamoto, "Investigation of Metal Contamination Induced by a Through Silicon Via Reveal Process Using Direct Si/Cu Grinding and Residual Metal Removal," Jpn. J. Appl. Phys., vol. 55 (2016) 06GP06.

[10] J. Utsumi, K. Ide, and Y. Ichiyanagi, "Cu/SiO2 hybrid bonding

- [10] J. Utsumi, K. Ide, and Y. Ichiyanagi, "Cu/SiO2 hybrid bonding obtained by surface-activated bonding method at room temperature using Si ultrathin films," Micro Nano Eng., vol. 2 (2019) 1.

- [11] N. Watanabe, H. Yamamoto, T. Mitsui, and E. Yamamoto, "Hybrid Bonding of Via-middle TSV Wafer Fabricated using Direct Si/Cu Grinding, Residual Metal Removal, CVD, and CMP," Proc. International Symposium on Microelectronics, 2020, pp.135–139.

[12] N. Watanabe, H. Yamamoto, T. Mitsui, and E. Yamamoto, "Impact of

- [12] N. Watanabe, H. Yamamoto, T. Mitsui, and E. Yamamoto, "Impact of Bonding Sequence on Contact Resistance in Hybrid Bonding of Viamiddle TSV Wafer," Proc. International Symposium on Microelectronics, 2021, pp.244–248.