# IMAPS 18th International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA Technologies to Markets

Market & Technology Trends for the Fanout and 2.5D/3D Packaging **Technology**

00655

**DEVICE PACKAGING**

Santosh KUMAR

**Senior Director**

santosh.kumar@yole.fr

© 2022

### NEW TRENDS & DRIVERS: OPPORTUNITY FOR SEMICONDUCTOR PACKAGING

◆ More computing power

◆ System integration

High speed

Low latency

◆Low power

More bandwidth

More functionality

More sensors

More memory

Low cost

Hardware-software compatibility

Opportunity for

various devices

Opportunity for

Megatrends create business for variety of ICs from high end xPUs to low end discretes

CPUs, GPUs, SoCs, APUs, FPGAs

← ASICS, DSPs, MCUs

MEMS/Sensors

Power ICs/discretes

Memories

Optoelectronics

Opportunity for fab/front end

Front end scaling slowdown but continues: Moore's Law keep going but at smaller pace => high end fab business keep growing (5nm & below)

More & more heterogeneous integration to support functionality, faster time to market and low cost: More than Moore's => Resurgence of legacy fabs => Increasing business

8" wafer fabs and related tools demand to remain strong

Require new technology / innovations: Front end design / manufacturing innovations: from von Neuman to neuromorphic computing architecture; new processes: beyond FinFet, nanowires FET, vertical NAND etc; require EUV and new deposition/etching technologies; new interconnect materials, dielectrics etc.

Create business opportunity for both advanced and traditional packaging platforms

Advanced packaging (WLPs, flip-chip, TSV) business opportunity supported by Al/ML, Mobile, AR/VR, 5G, smart automotive

Traditional packaging (wire-bond lead frame based) business opportunity created by IoTs, Industry 4.0, smart automotive

Mega trends like mobile, automotive, IoTs, industry 4.0, require variety of MEMS sensors that create opportunity for both traditional & advanced packaging

Require Back end and assembly innovations: panel level packaging, high accuracy bonders, TCB, CtW/WtW bonding, photonics integration in package. As for materials, there is a desire to develop new dielectric materials, mold compounds, underfill, solder interconnects, and TIMs for fulfilling the stringent performance and reliability requirements demanded by next-generation hardware.

0065

# PACKAGING TECHNOLOGIES OVERVIEW 17-10, 2022 | Fountain Hills, AZ USA

| ARCHITECTURE    |                      | WIRE BOND                                  | FLIPPED DIE                             | EMBEDDED DIE                                                   | 2.5D                                                    | 3D                                                       | EMERGING                                                                           |

|-----------------|----------------------|--------------------------------------------|-----------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------|

|                 |                      | Traditional Packaging                      | Advanced Packaging                      | Advanced Packaging                                             | Advanced Packaging                                      | Advanced Packaging                                       | Advanced Packaging                                                                 |

| SUBSTRATE TYPES | (Organic)            |                                            | FC BGA  Die  IG Substrate  PCB          | Embedded Si Bridge  Die Si Bridge Die CSubstrate  PCB          | Si Interposers  Die HBM HBM INTERPOSER IC Substrate PCB | 3DS TSV  Stacked  DRAMs  A IC Substrate way w.           | Hybrid Bonding - SoC on interposer  HBM SoC SO |

|                 |                      |                                            | FC CSP  Die  IC Substrate  PCB          | IC Substrate                                                   | Die Die PCB                                             | HBM TSV Stacked DRAMs Die INTERPOSER R.C. Substrate v.s. |                                                                                    |

|                 |                      | WB CSP<br>WB BGA  Die  1 (C Substrate  PCB | FC SiP Metal Shielding                  | Embedded Die / Passives  Embedded Active Die iC Substrate  PCB |                                                         | NAND TSV  Stacked NANDs  PCB                             | Embedded Multi-Die / Passives  SOURCE: JCET PCB                                    |

|                 |                      | DRAM IC Substrate PCB                      | Fan-Out on Substrate  IC Substrate  PCB | FOPLP  IC Substrate Die PCB                                    |                                                         |                                                          |                                                                                    |

|                 | No Substrate         | COB Die PCB                                | P                                       | Die Die PCB                                                    |                                                         | Cu-Cu Hybrid Bonding – WoW                               | Hybrid Bonding - SoC in Fan-Out  DRAM  SOURCE: TSMC  PCB                           |

|                 |                      |                                            | Fan-In (WLCSP)                          |                                                                |                                                         | TSV, after bonding – WoW                                 |                                                                                    |

|                 | Ceramic Substrate    | PCB                                        | Die CPGA CPGA                           |                                                                |                                                         |                                                          |                                                                                    |

|                 | Lead frame Substrate | QFP, LCC etc.                              | FC QFN                                  |                                                                |                                                         |                                                          |                                                                                    |

### ADVANCED PACKAGING OVERVIEW DE PICKAGING MARCO DE PICKAGING LIMARO DE PICKAGINA DE PICKAGING LIMARO DE PICKAGINA DE PICKAGING LIMARO DE PICKAGINA DE PICKAGINA DE PICKAGINA DE PICKAGINA DE PICKAGINA DE PICKA

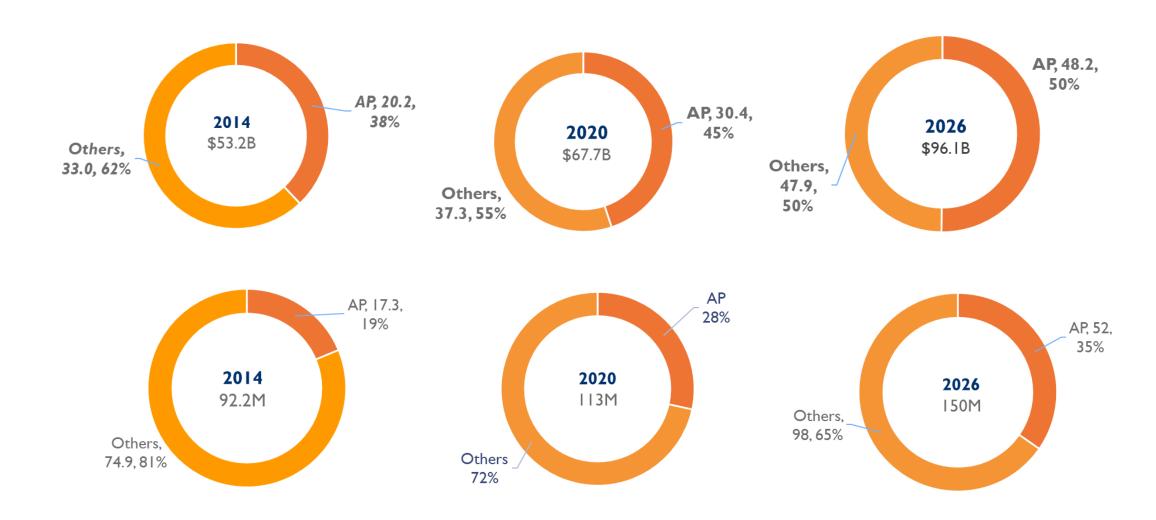

## Revenue Split (\$B) and wafer starts (300mm eq.) split

### A RECORD YEAR FOR PACK & GING PLAYERS (PACKAGING REVENUE)

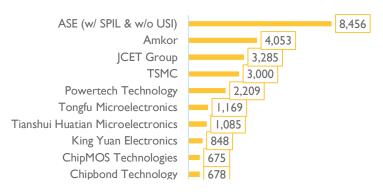

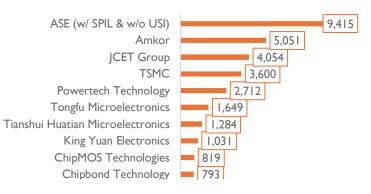

# Top Packaging Players Ranking by 2019 Revenue [\$M]

# Top Packaging Players Ranking by 2020 Revenue [\$M]

### YoY Growth [%]

15-20% increase in 2020 revenue compared to 2019, and 2021 is expected to shape up as a "Banner Year" for Packaging Players

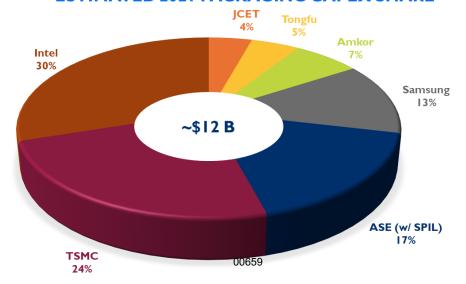

### **ESTIMATED 2021 PACKAGING CAPEX SHARE**

### ADVANCED PACKAGING IS NOW AN ESSENTIAL TECHNOLOGY

Big players are committing extensively to 3D/2.5D Packaging

At Intel's Architecture Day 2020, Intel introduced "Process and Packaging" as one of the 6 Technology Pillars

**Samsung Foundry** is positioning packaging as a **one-stop total solution**; covering design, memory, logic and package.

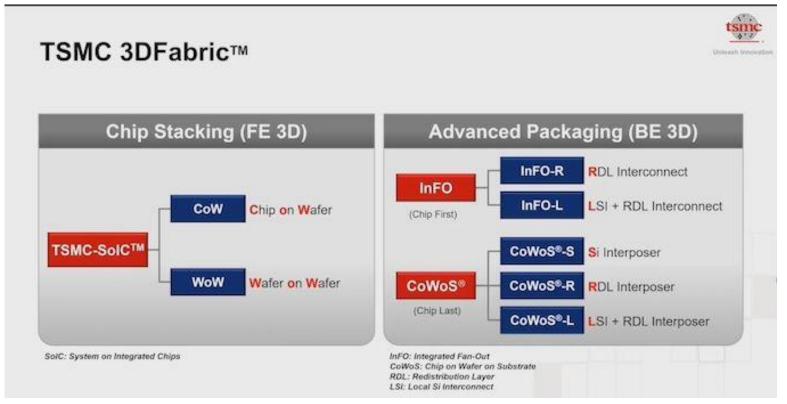

In 2020, **TSMC** announced a new 3D/2.5D Packaging family called **3DFabric™**, ready to capture high-end performance computing business

00660

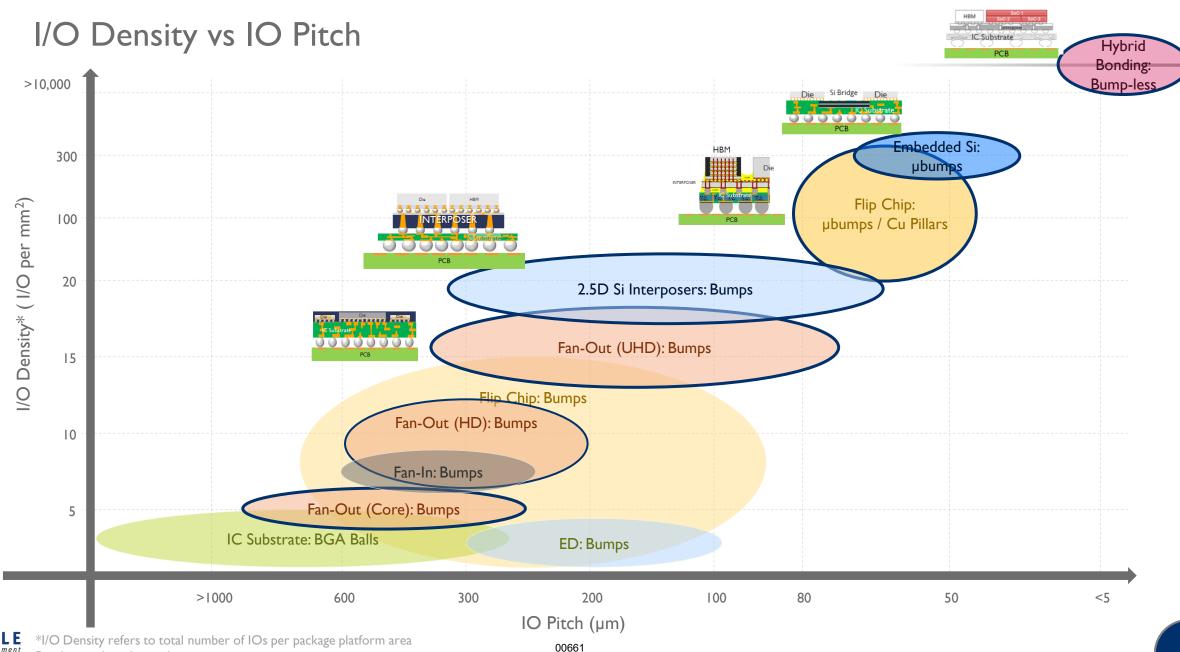

### ADVANCED PACKAGING TECHNOLOGY ROADMAP

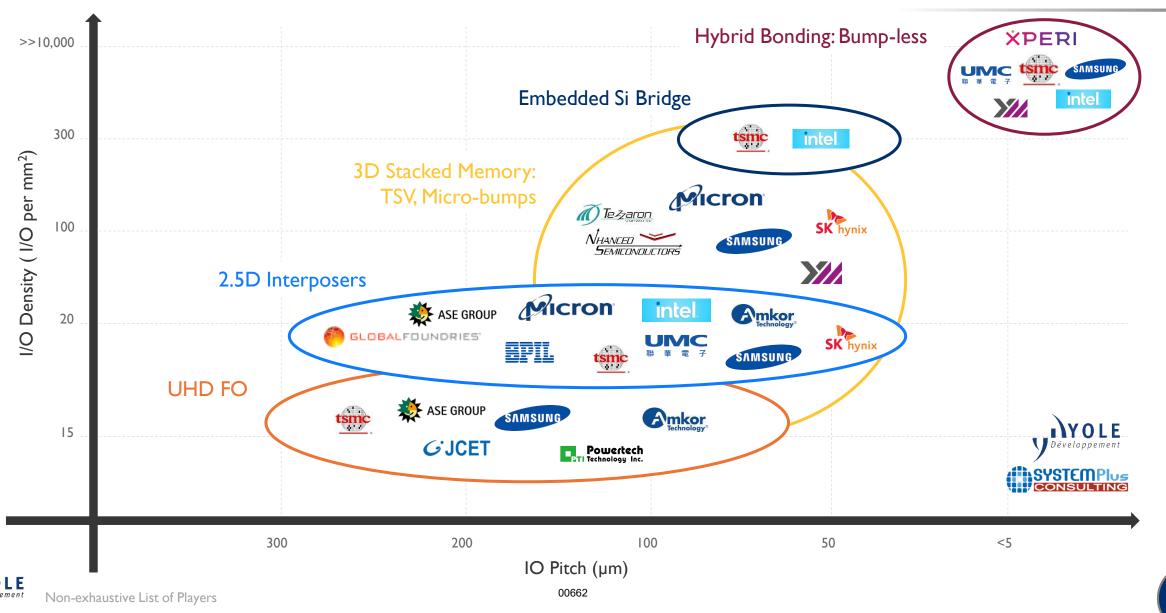

# HIGH-END PACKAGING: SUPPLY CHAIN March 7-10, 2022 | Fountain Hills, AZ USA

## Mapping of Players based on Technology

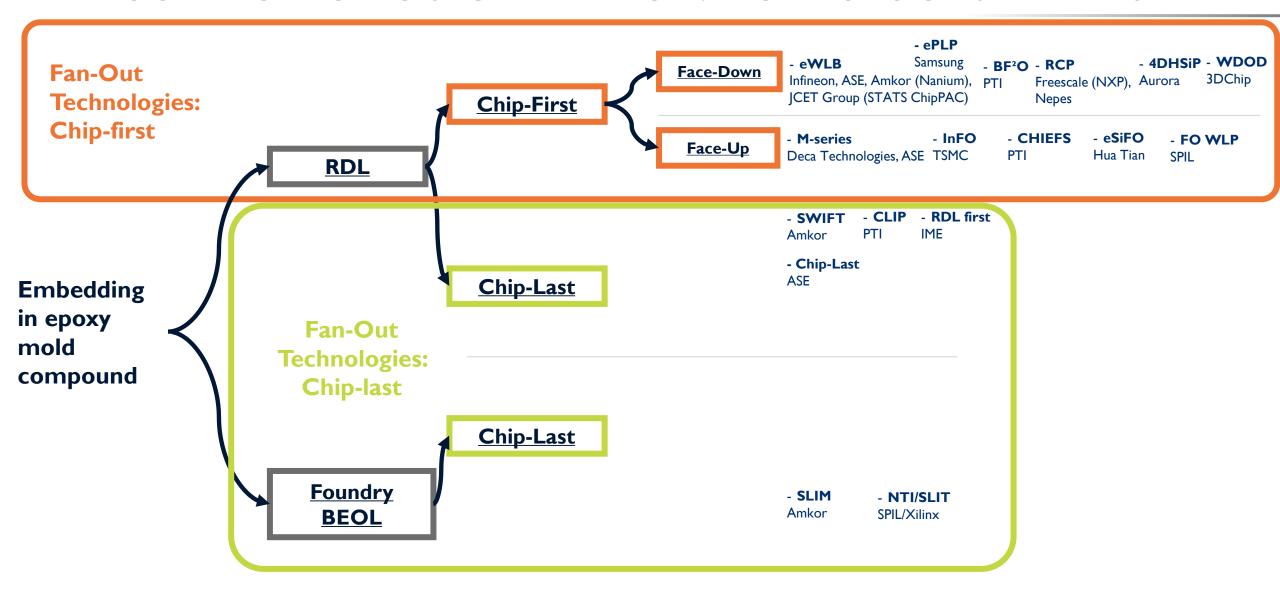

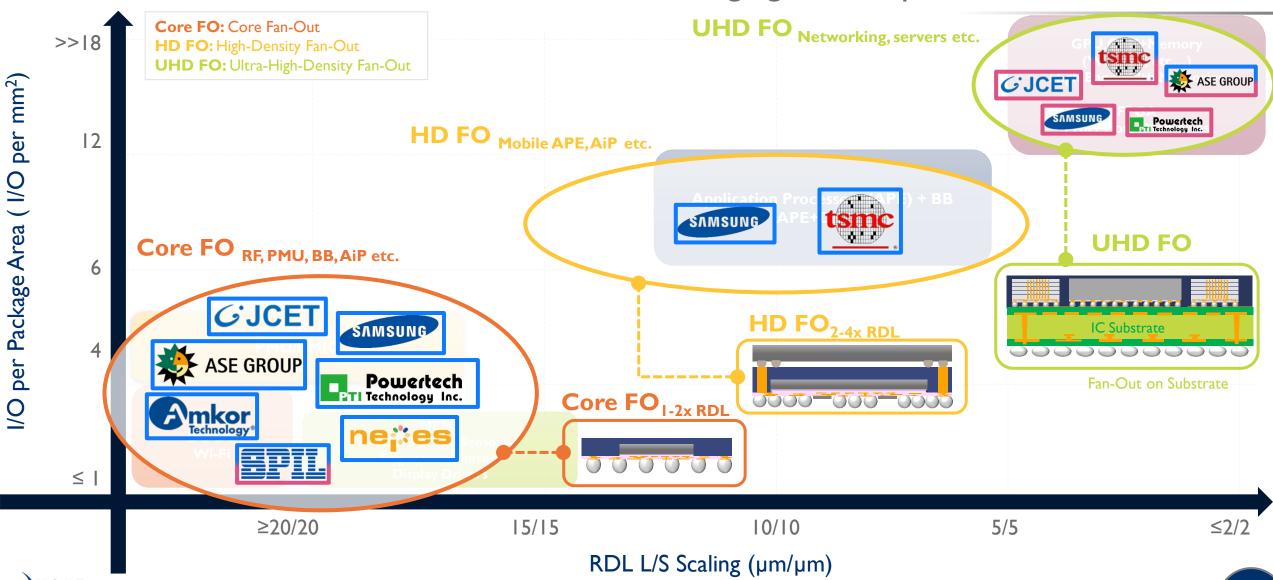

### FAN-OUT PACKAGING SEGMENTATION: TECHNOLOGY & PLAYERS

\*Non-exhaustive list of technologies

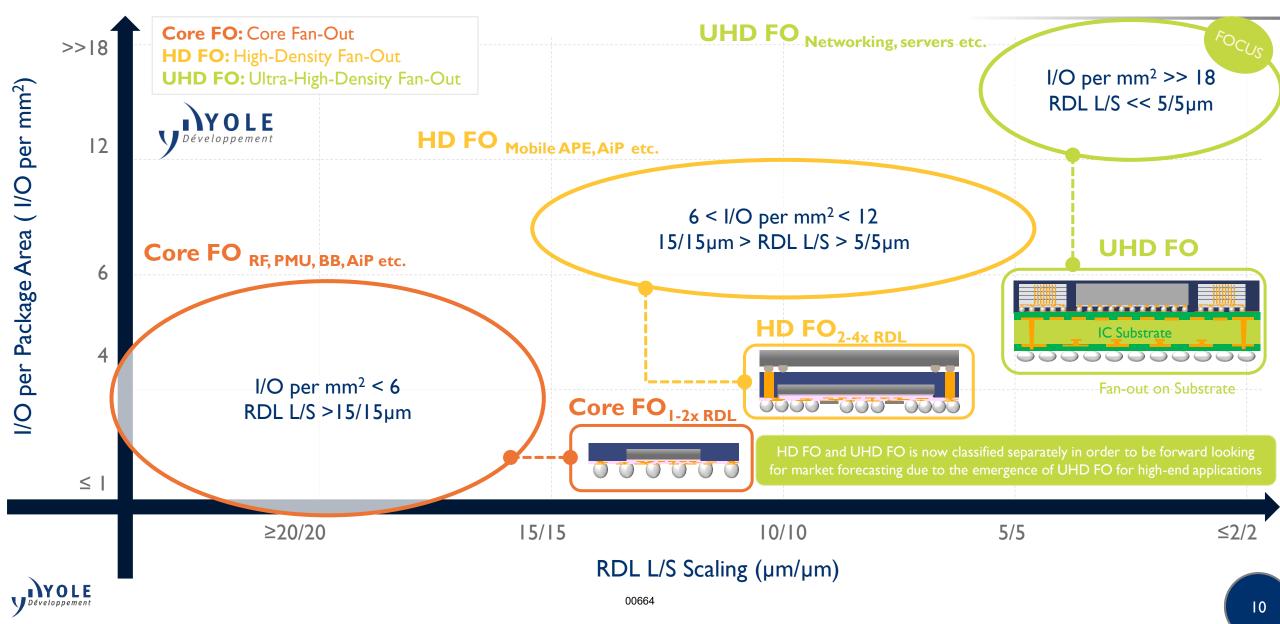

## FAN-OUT PACKAGING DEFINITION BY MARKET CLASS

### Core FO vs HD FO vs UHD FO

# FAN-OUT PACKAGING SEGMENTATION: MARKET AZ USA

Production

Development

Manufacturers' Status in 2020 Fan-Out Packaging Landscape

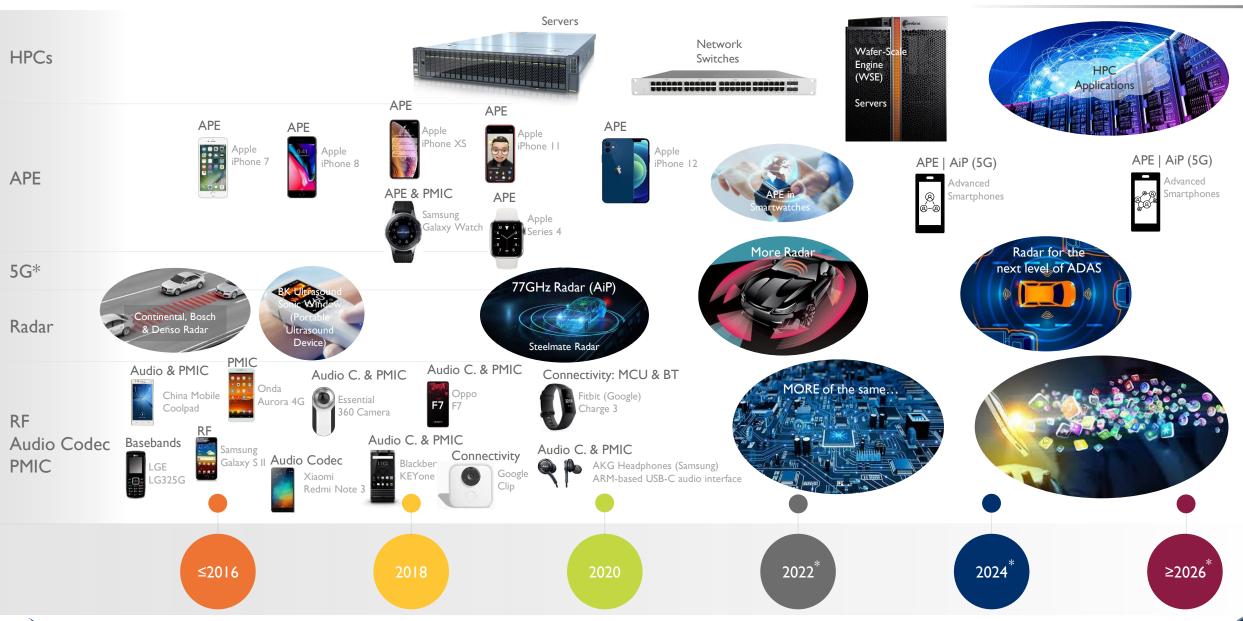

### FAN-OUT PACKAGING MARKET DRIVER'S ROAD MAP

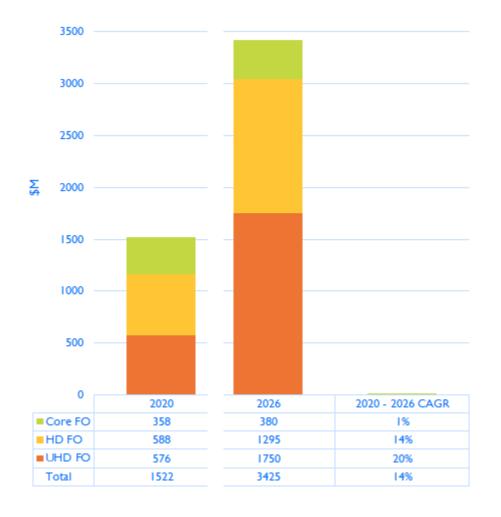

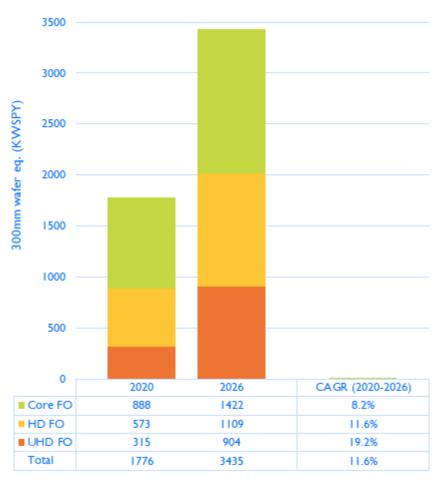

## FO PACKAGE MARKET DYNAMICS: UHD, HD, AND CORE FAN-OUT

Avg. ASP per package area (\$/mm2)

Revenue (\$B)

Wafer (KWSPY, 300mm eq.)

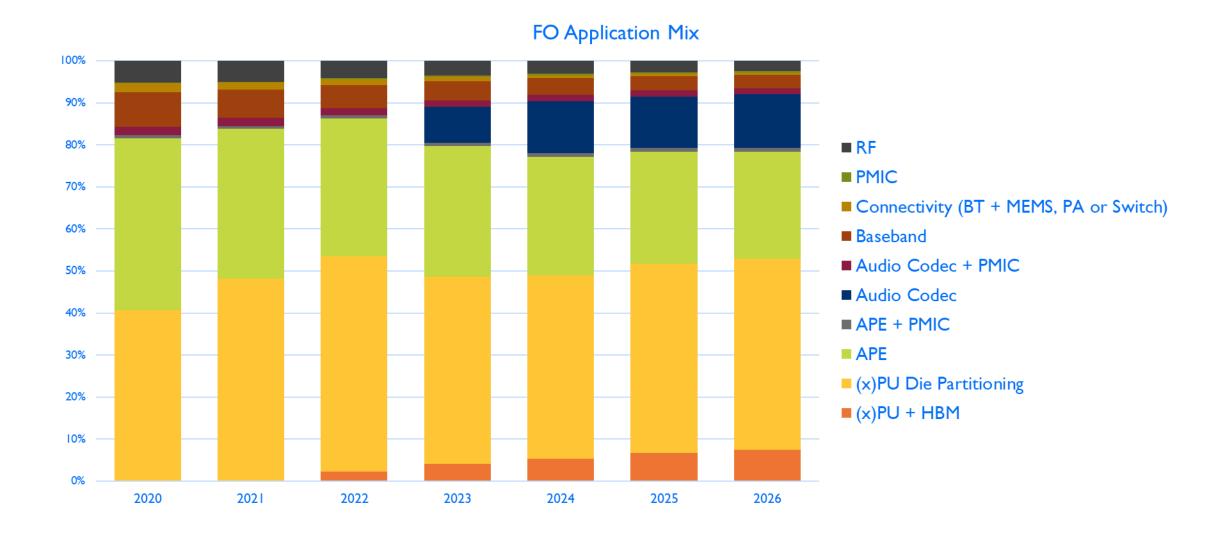

### FO PACKAGE APPLICATION 18th International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA

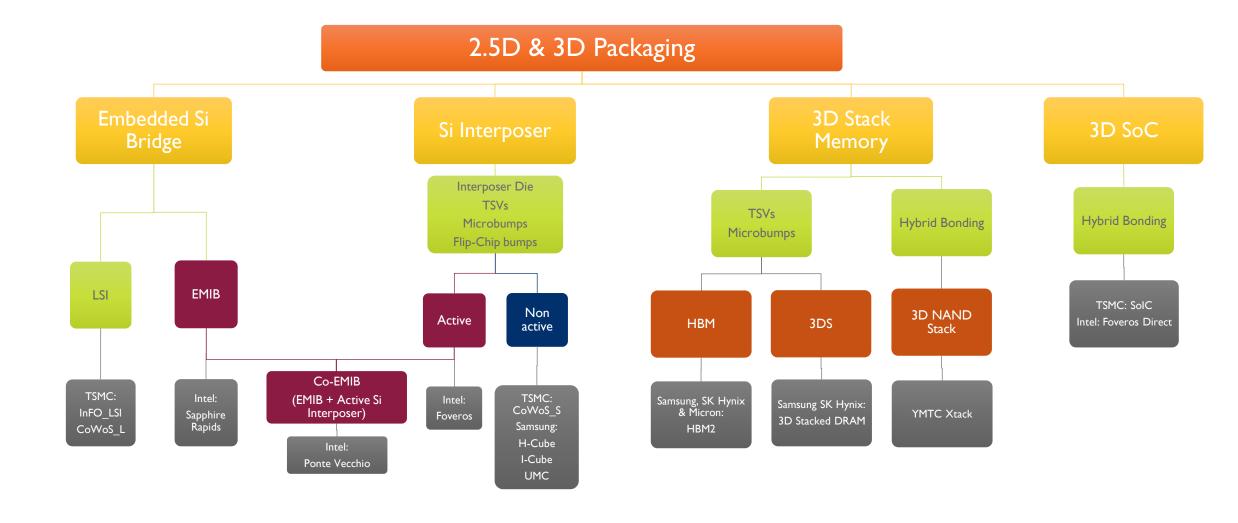

# 2.5D/3D

### HIGH-END PERFORMANCE PACKAGING—ALL PLANTON PINIS AT THE PACKAGING ACTOR OF THE PLANTON PINIS AT THE PACKAGING ACTOR OF THE PACKAGING ACTO

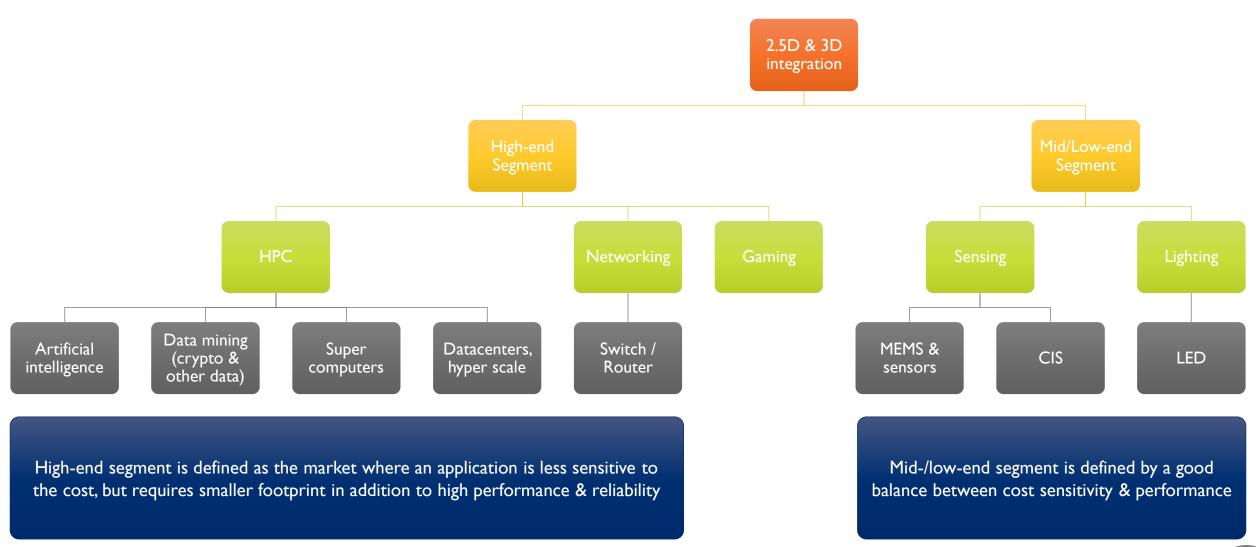

### HIGH-END PERFORMANCE PACKAGING — MARKET SEGMENTATION

The market is divided into high-end & mid- / low-end segments

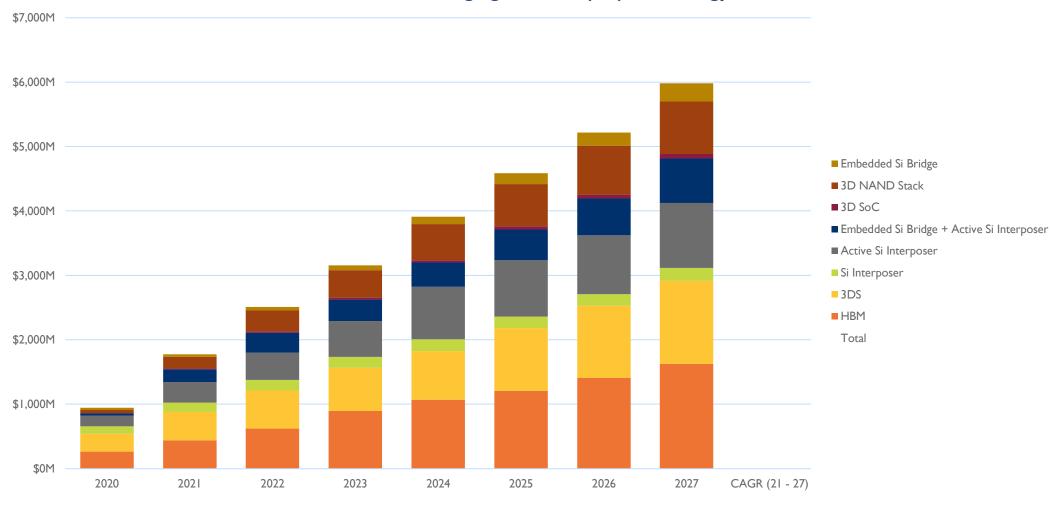

### 2.5D/3D PACKAGING REVENUE-SPLIT BY TECHNOLOGY

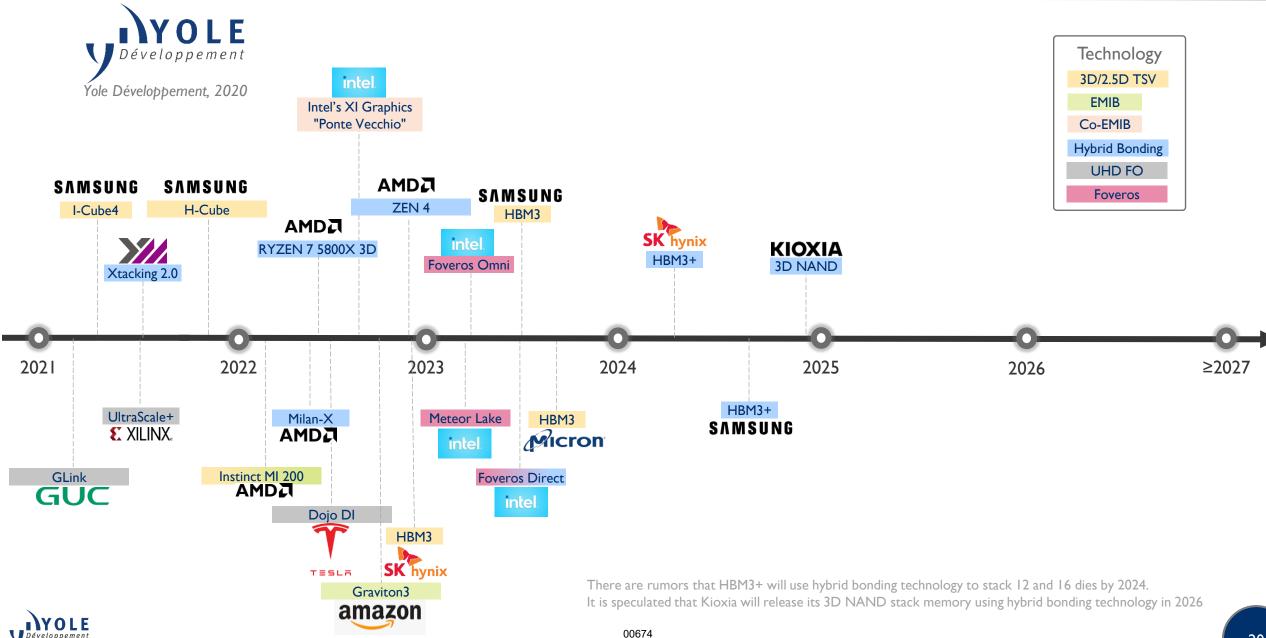

### 2.5D/3D PACKAGING ROAD MAP: APPLICATION OF THE CHNOLOGY

TIMELINE

YMTC Periphery + Array X-Stacking

Intel HBM+GPU

Kaby Lake-G

**≤2019** — **2020\*** — **2021** — **2022** — **2023** — **2024** — **2025** →

HPC (x)PU in Servers TSMC & Intel - 3D SoC

**TYPE OF TECHNOLOGY**

**Hybrid Bonding**

**Embedded Si bridge**

**TSV**, Micro-bumps

**2.5D** Interposers

Intel FPGA Stratix 10

NVidia GPU Interposer HBM2E

Intel Exascale GPU - HPC Ponte Vecchio: Co-EMIB

Stacked DRAM Samsung HBM Flarebolt

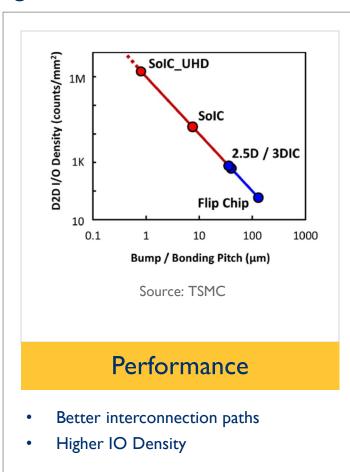

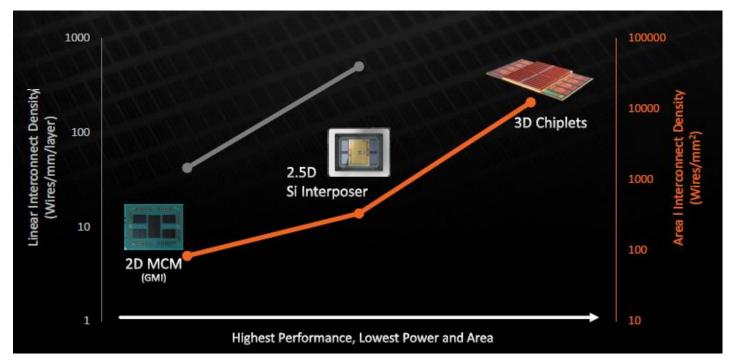

I/O DENSITY

AMD GPU

Google (x)PU TPU V3

Samsung HBM2E Flashbolt

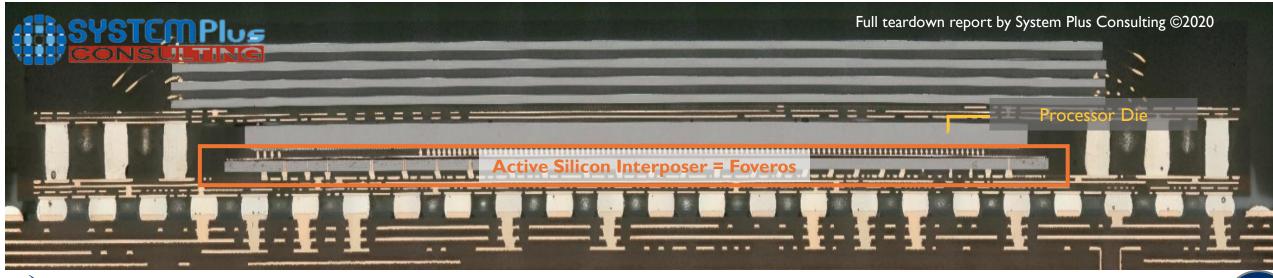

Intel CPU + Active Interposer Intel Lakefield Foveros Core i5-L16G7

Broadcom (x)PU + HBM lericho2

Intel (x)PU Ethernet Switch Tofino2

HiSilicon CPU (Storage) Hil610 (Now known as Kunpeng)

Pascal 100

### HIGH-END COMMERCIAL PRODUCT LAUNCHIES - STACKAGING HILLS - STACKAGING

# 3D SYSTEM ON CHIP (3D SOC) March 7-10, 2022 | Fountain Hills, AZ USA

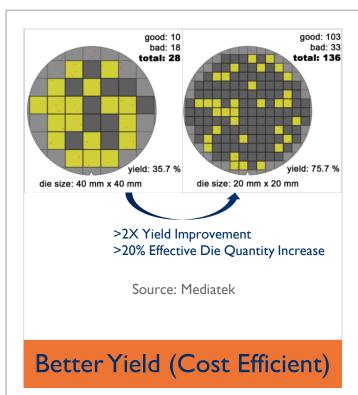

## Advantages of Die Partitioning

### Die partitioning consists of splitting a die's functions and redistributing them across two or more dies.

- Footprint reduction enables saving board surface

- Gain yield due to smaller die size

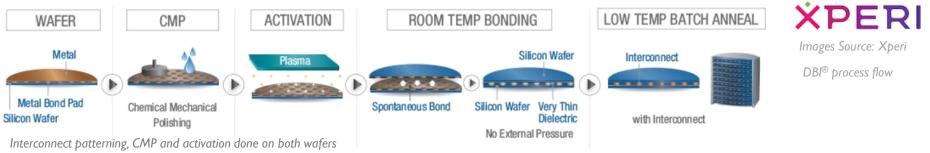

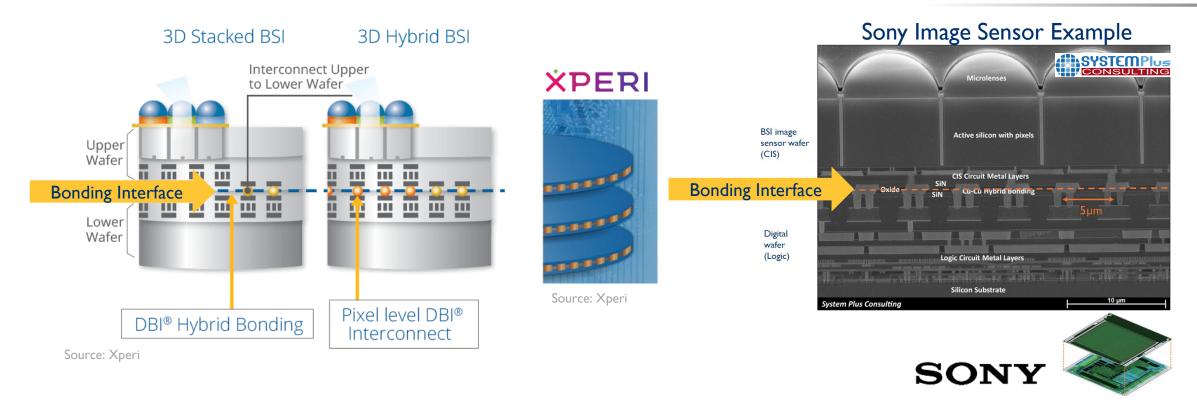

## HYBRID BONDING PROCESS FLOW PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA

Note: Showed is process flow established by XPERI, but other process developments have been also done in parallel, e.g. Leti, Imec, TSMC.

### W2W process flow

- Used for CIS, F2F logic, 3D NAND

- IN HVM from 2015/2016

- Specialized CMP tools and W2W bonders are used

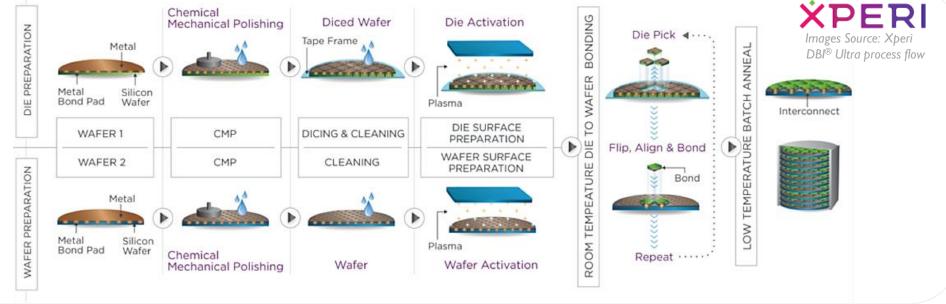

### D2W process flow

- Used for heterogenous integration

- LVM expected in 2022

- Specialized CMP tools, singulation tools, and D2W flip chip bonders are used

- Singulated dies from source wafer are cleaned and activated collectively on tape frame (special plasma reactors or atmospheric plasma) are transferred one-by-one to destination wafer

# 3D SOC/SOIC PACKAGING (USING HYBRID BONDIND APPROACH)

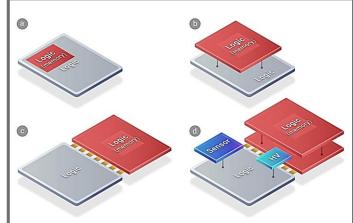

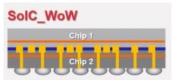

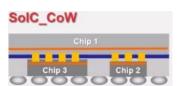

### Key features of 3D SoIC technology: Heterogeneous integration, scalability & 3D system integration

Heterogeneous integration of KGDs with different chip sizes, functionalities and wafer node technologies

(a) SoC before chip partition; (b), (c), (d) Variant partitioned chiplets and re-integrated schemes enabled by SoIC

### **Exceptional scalability**

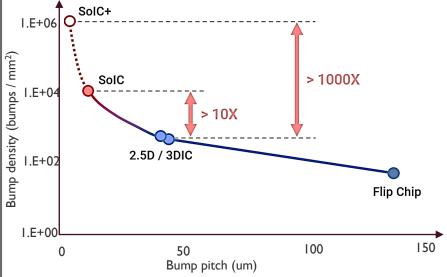

With the innovative bonding scheme, SoIC enables strong bonding pitch scalability for chip I/O to realize high-density die-to-die interconnects. The bond pitch starts from sub-10  $\mu$ m. Short die-to-die connection of SoIC has the merits of smaller form-factor, higher bandwidth, better power integrity (PI), signal integrity (SI), and lower power consumption compared to the current industry state-of-the-art packaging solutions.

### Holistic 3D system integration

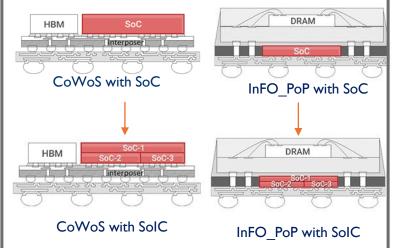

SolC integrates both homogeneous and heterogeneous chiplets into a single SoC-like chip with a smaller footprint and thinner profile, which can be holistically integrated into advanced WLSI (aka CoWoS and InFO). From external appearance, the SolC is just like a general SoC chip yet embedded with desired and heterogeneously integrated functionalities.

### TSMC'S NEW ADVANCED PACKAGING BRANDING STANDING

## TSMC has introduced 3D Fabric Technology Segmentation in 2020

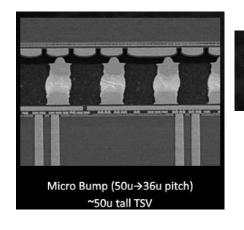

| F2F Technology                    | 3D-IC     | SoIC      | SoIC_UHD  |  |

|-----------------------------------|-----------|-----------|-----------|--|

| Structure                         | 85ibump38 | SolC Bond | SolC Bond |  |

| Bump pitch                        | 36 μm     | 9 μm      | 0.9 μm    |  |

| Bump Density                      | 1.0X      | 16.0X     | 1600.0X   |  |

| Speed*                            | 1.0X      | 11.9X     | 11.9X     |  |

| Bandwidth Density**               | 1.0X      | 191.0X    | 19100.0x  |  |

| Power Consumption<br>(Energy/bit) | 1.0X      | 0.05X     | 0.05x     |  |

TSMC's InFO integration with an LSI is called InFO-L or InFO-LSI, and follows a similar structure with the new addition of it integrating this new local silicon interconnect intermediary chip for communication between two chips.

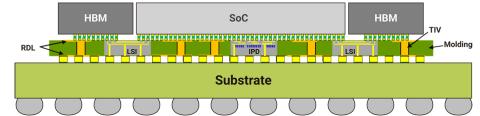

CoWoS-L is the new variant of TSMC's chip-last packaging technology. It adds in the Local Si Interconnect in combination with a RDL to achieve higher bandwidth than just an RDL packaging implementation (CoWoS-R) and will be more cost-effective than a full silicon interposer implementation (CoWoS-S).

24

6veloppement Source: TSMC

# 3D SOC/SOIC PACKAGING (USING HYBRID BONDIND APPROACH)

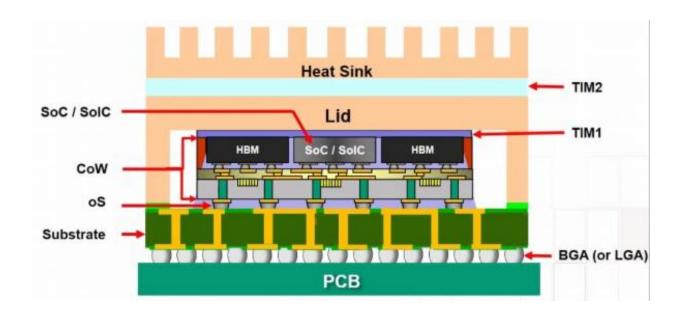

### 3DFabric building blocks

- SoC/TSV

- SoIC hybrid bond

- Si, RDL, embedded Si/RDL interposers

- Integrated IPDs/DTC

- Mass reflow/LAB/TCB

- Substrate

- TIM & Thermal

- PCB (BGA/LGA)

Path to SoIC: technical requirement

- From Bump to SolC

- Bonding alignment accuracy: 5-20um (bump) to <0.5um (bumpless)

- Bonding interface defect: I 0um to < I um</li>

- Topography: um to nm

- Die warpage: 60-100um to 10-20um

- Stringent equipment capability & process control critical for high yield

## HYBRID BONDING STATUS International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA

| Types   | Application                                                                                | Production Status              | Key players                                            |

|---------|--------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------|

| W2W     | CIS, 3D NAND                                                                               | HVM                            | Sony, YMTC, Samsung, TSMC, Global Foundries            |

| D2W/D2D | Heterogeneous integration (logic to logic, logic to memory, logic to active Si interposer) | Qualified, HVM in 2022         | TSMC, AMD, Intel,<br>Samsung, UMC, Global<br>Foundries |

|         | 3D memory (HBM, 3DS), logic to logic                                                       | Development, HVM in 2023/ 2024 | Samsung, SKHynix, Micron, TSMC                         |

### Hybrid bonding for D2W and D2D, nevertheless, comes with severe technological challenges:

- Unprecedented placement accuracy below 200 nm at each point of the chip

- ISO 3 cleanroom class at the processing area to ensure void-free bond interfaces

- High productivity of > 3000 units per hour (UPH)

- CMP: Recess between Cu and dielectric

- Dicing method to ensure minimum particle generation

### HETEROGENOUS INTEGRATION: INTEGRATION

During Intel Architecture Day 2021, Intel announces Foveros Direct using hybrid bonding. Planned to entry the market in 2023, enlarging Intel'a advanced packaging toolbox. As such, EMIB and Foveros will be be Mix and Match -ed for High Performance Computing Applications..

# Continued leadership in advanced packaging

bump pitch 50-40 microns

- leads industry

- first 2.5D embedded bridge solution

- products shipping since 2017

### Foveros Technology

bump pitch 50-36 microns

- wafer-level packaging capabilities

- first-of-its-kind 3D stacking solution

### Foveros Omni

bump pitch ~25 microns

- next gen Foveros technology

- unbounded flexibility with performance 3D stacking technology for die-to-die interconnect and modular designs

### **Foveros Direct**

bump pitch < 10 microns

- direct copper-to-copper bonding for low resistance interconnects

- blurs the boundary between where the wafer ends and the package begins

Source: Intel Accelerated 202 | Event

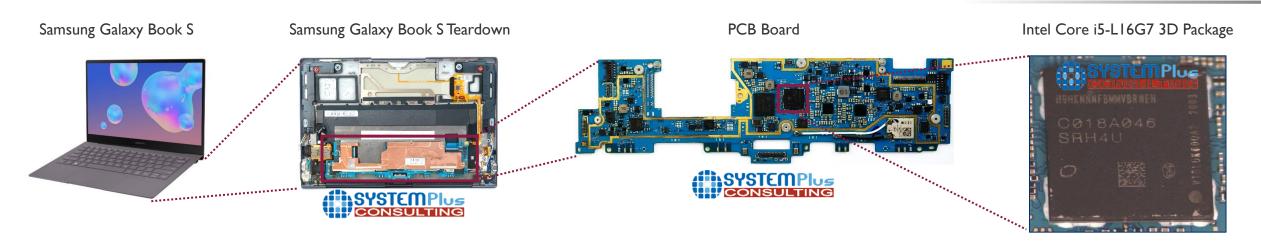

### INTEL PROCESSOR WITH 2.5D STACKAGING Merch 7-10, 6022-1-Fountain Hills, 2004 OGY

Intel's Foveros in the Samsung Galaxy Book S (1/2)

Cross-Section (Optical View) of Intel Core i5-L16G7 3D Package

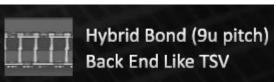

# AMD ADOPTION OF SOIL BONDING FOR HPC APPLICATION

### AMD package roadmap

Migration from micro bump to hybrid bond: >15X interconnect density compared to microbump

- >200X Connection Density Compared to On-Package 2D Chiplet

- > 3X Interconnect Energy Efficiency Compared to micro bump 3D

Source: AMD

Last year, AMD demonstrated the 3D chiplet stacking called 3D V-Cache. The Ryzen 5000-series microprocessors incorporate one or two Core Complex Dies (CCDs) along with an I/O Die (IOD). The V-Cache is a 64 MiB SRAM die that is said to be fabricated on TSMC's 7-nanometer process. The V-Cache die is thinned and is then stacked directly on top of each CCD directly above the existing L3 cache area using hybrid bonding.

Two AMD products are planned to be launched in 2022 using hybrid bonding:

- AMD Ryzen processor with incorporated 3D V-CacheTM technology dedicated to gaming applications.

- Milan-X CPU with 3D V-CacheTM technology allowing SRAM Cu-Cu interconnection with CPU based on Zen 3 architecture (TSMC 7nm+) dedicated to server applictaions. 00683

## FOCUS ON CIS: XPERIAND SOME PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA

# Applications of DBI®: W2W Hybrid Bonding

DBI wafer fabrication has been in volume production since 2015 (Sony CIS implemented in Samsung Galaxy S7) on **W2W** level, for **CMOS** image sensor (CIS) solutions in high-end smartphones. Next big applications are expected for Industrial (barcode reader, surveillance camera, and machine vision) and Automotive (ADAS)

### STACKED MEMORY WITH HYBRID BONDING

## YMTC'S 3D NAND X-STACKING in GLOWAY SSD

Gloway 512GB SSD

Opening of Gloway 512GB SSD

YMTC 128GB 3D NAND X-Stacking Total 4x 125GB found in top/bottom PCB

Cross Section of 3D NAND X-Stacking

3D Hybrid Bonding

Gloway 512 GB SSD is targeted to enable faster boot-up, shutdown, application load and response, due to YMTC's new 3D Hybrid Bonding X-Stacking technology from YMTC. There is a shorter communication path between CMOS and NAND cells as compared to 3D NAND, hence, Gloway is expected to read/write 20 times faster (Sequential Read Speed: 540 MB/s and Sequential Write Speed: 450MB/s) as compared to a normal hard drive. More reliable, stable and durable than a hard drive by using 3D NAND technology.

The bonding interface is done by chemical bonding between the two wafers, NAND Array and Periphery CMOS. The physical interaction between the dielectric material and the metal material in the two wafers forms the bond – Hybrid Bonding.

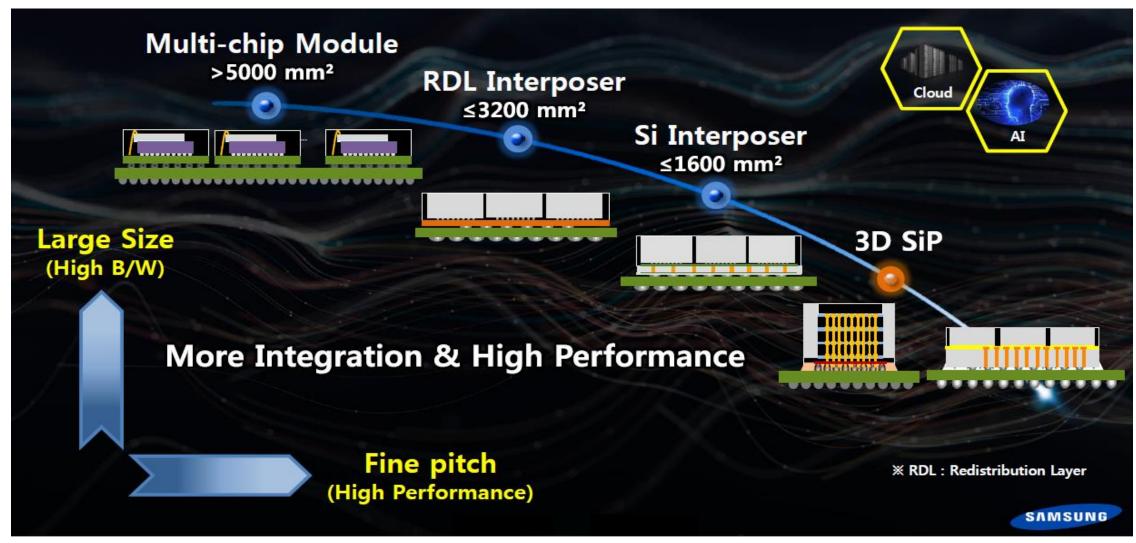

### SAMSUNG'S ADVANCED PACKAGING TECHNOLIS CONTROL PROBLEM ROADMAP

Al/HPC/Server Platform revolves around High-end Packaging

Source: Samsung Foundry

## SAMSUNG LATEST DEVELOPMENT OF PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA

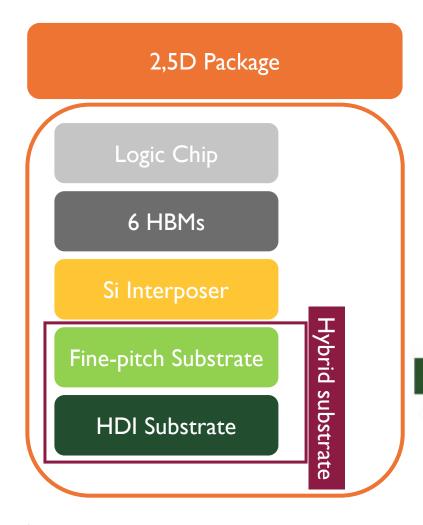

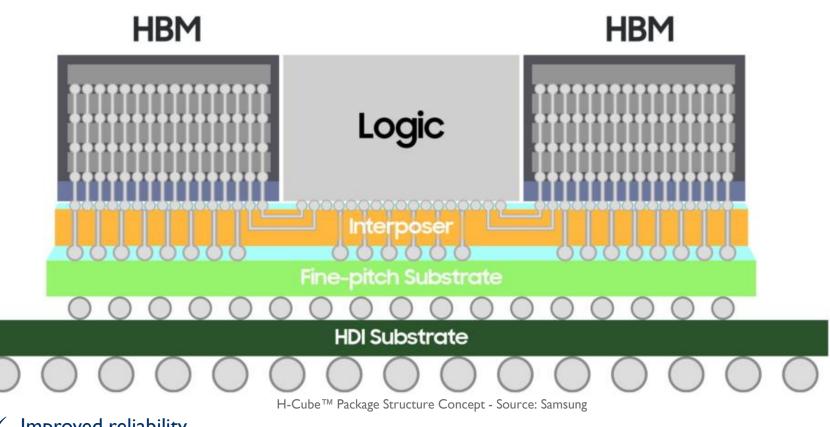

## Samsung's H-Cube

### **H-Cube Structure & Features**

- ✓ Minimized signal loss or distortion

- Lower cost

# Thanks!

# ACKNOWLEDGEMEN 18th International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA