# Heterogeneous integration of chiplets Lego-like IP for more than Moore

Keith Felton

Product Marketing Manager

Siemens EDA

#### Gordon E. Moore Observations

the number of transistors on a microchip doubles every two years, though the cost of computers is halved. This so called "Moore's Law" states that we can expect the speed and capability of our computers to increase every couple of years, and we will pay less for them. Another tenet of "Moore's Law" asserts that this growth is exponential

Expert opinions see these observations ending in the 2020's driven by:

- 1. Reticle limits

- 2. NRE costs

- 3. Availability of required IP

- 4. Yield

- 5. Die cost

- 6. Device scaling

- 7. Function aggregation

- 8. I/O scaling

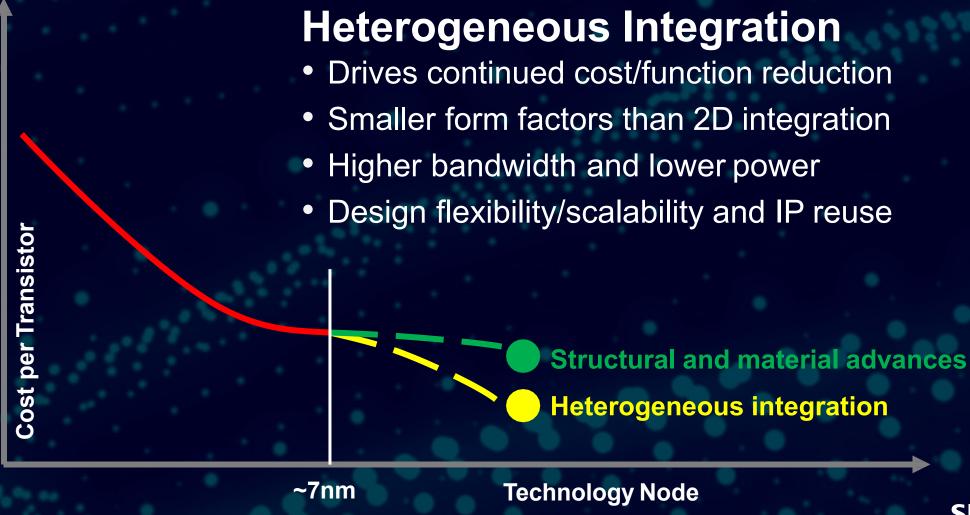

#### **Transistor Costs**

\$1.64

3nm (P)

At Introduction of Technology After Depreciation \$3.81 \$3.03 \$2.29 \$1.66 \$1.60 \$1.00 10nm 5nm (P)

7nm the pivot point?

Monolithic forces all functions to be at same node

Memory and I/O not ideal

### Technology inflection point

# SOCIAL MANOELEC.

#### Cost and yield driving alternatives to monolithic solutions

- SOC disaggregation into hard IP or "chiplets"

- Multi-die implementation to avoid reticle limitations (vs. single die)

#### Data movement - low latency, high-bandwidth

- Use of High Bandwidth Memory (HBM)

- 3D memory directly stacked on logic

- High-speed IO for chip-to-chip interfaces

#### Heterogeneous integration provides path forward

- Supports multiple micro-architecture scenarios

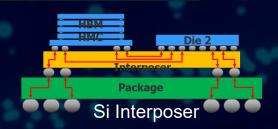

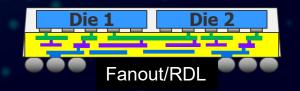

- Leveraging 2.5 and 3D assembly platforms

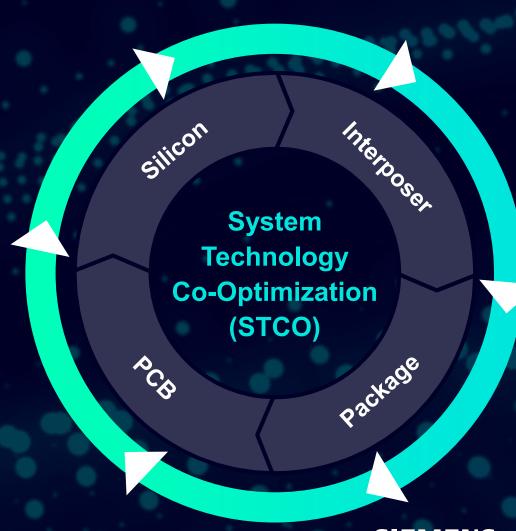

- Utilizes System Technology Co-optimization (STCO)

# Frends

### Extending "Moore's Law"

# Trends

#### Heterogenous Integration path forward

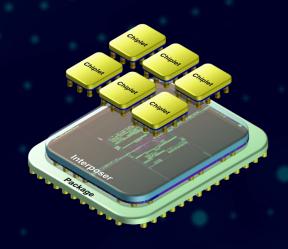

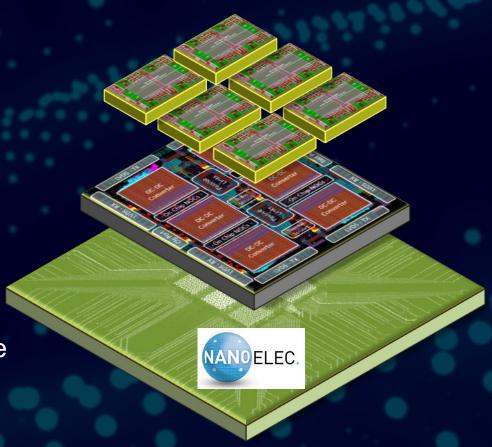

# Enabling alternative Micro-architectures High Bandwidth Memory (HBM)

**ASIC** Die Disaggregation

ASIC IP Disaggregation

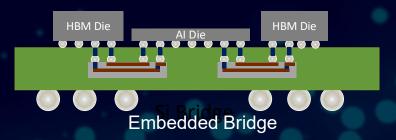

2.5D Silicon Interposers, Fanout/RDL, Silicon Bridge

3D IC Stacked Die

#### Key Benefits

**Increased Performance**

Reduced Power

Lower unit cost/NRE

**Product Configurability**

#### Case study results

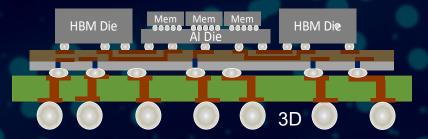

#### AMD Cost comparison of chiplets vs. monolithic

- 41% reduction in die cost and higher yield

- Maximize platform value product configurability from single tape-out

#### **Developing eco-system**

- Standards for chiplet marketplace and exchange

- Turn-key design/build resources

- Materials suppliers

Presented at 2021 International Solid State Circuits Conference

|                                    | Monolithic | Diff  | Chiplet |

|------------------------------------|------------|-------|---------|

| Wafer Cost (7nm)                   | \$9,350    | 1x    | \$9,350 |

| Total Die Size                     | 600mm2     | 1.1x  | 660mm2  |

| Single Die Size                    | 600mm2     |       | 165mm2  |

| Gross Die per Wafer                | 96         |       | 387     |

| Defect Rate (per cm <sup>2</sup> ) | 0.2        | 1x    | 0.2     |

| Effective Area                     | 80%        | 1x    | 80%     |

| Estimated Yield (Dingwall)         | 43%        |       | 78%     |

| Net Die per Wafer                  | 42         |       | 300     |

| Single Die Cost                    | \$224      |       | \$31    |

| Total Die Cost                     | \$224      |       | \$124   |

| Total Test Cost                    | \$10       | 1.2x  | \$12    |

| Package and Packaging              | \$160      | 1.25x | \$200   |

| Packaging Loss                     | 1%         | 4x    | 4%      |

| Total Manufacturing Cost           | \$398      |       | \$347   |

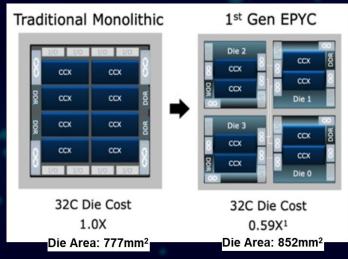

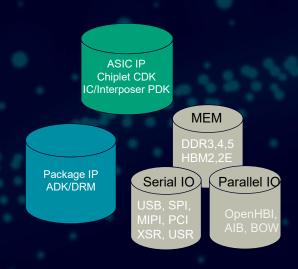

#### Chiplets

#### Enabling modular function design

- No need to own/design full stack

- Aggregated with custom ASIC(s)

Fabricated using ideal nodes

Integrated through standardized interfaces and CDK's

Commercially available

Low NRE and fast TTM

# Needs

#### **Success with Chiplets**

**Chiplet design kits**

Heterogeneous planning and co-optimization

Physical verification at every level of 3D assembly

**Multi-domain testing**

**Ecosystem interoperability**

### Standardized chiplet design kit

**Machine readable** models

**Standards**

**Documentation**

**Security and Traceability Assurance**

**Chiplet Design** Kit (CDK)

**SIEMENS**

## Chiplet ecosystem enablers

Needs

**Technology**

Intellectual property

Workflows/ design kits

Business models

#### Heterogeneous Planning & Prototyping

Needs

Single digital twin and system logi netlist

System Technology Co-Optimization

Predictive modeling to prototype and qualify design scenarios

Replacement of spreadsheet-based flows as communication mechanism of design intent

### Planning and prototyping workflow

Die Design

IO & bump info Interface info Floorplan/keep-outs

**PCB** Design

Critical comps Interface info Optimized pkg

Predictive modeling with high-level design abstractions

#### **STCO Planning & Prototyping**

- Data aggregation & design setup

- Device placement & stacking definition

- Net list definition & connectivity optimization

- Data path planning & route feasibility

- Trade-off and scenario exploration

- Predictive modeling to qualify scenarios

- · Export of qualified implementation data

Qualified design ready for implementation

# Needs

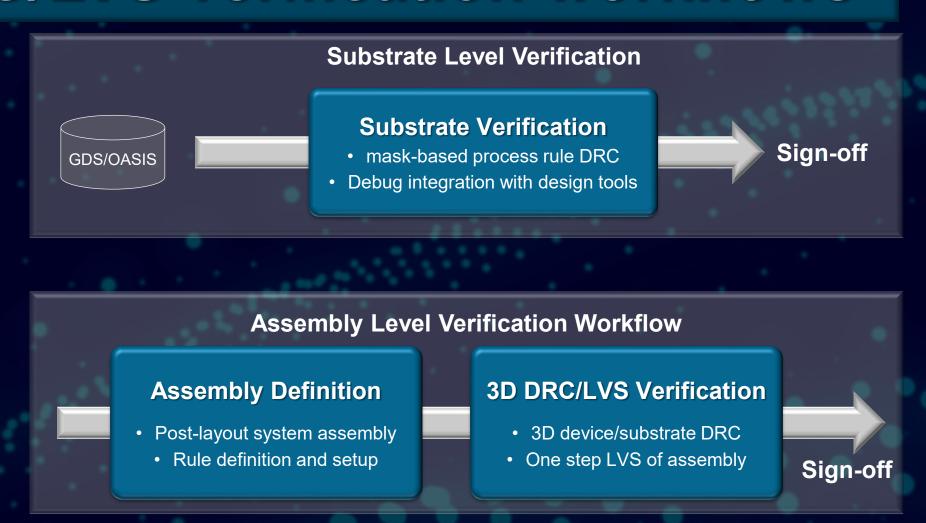

## Verification at every level

Subst

3D ass

Prodice

**Substrate level fabrication DRC**

3D assembly level LVS

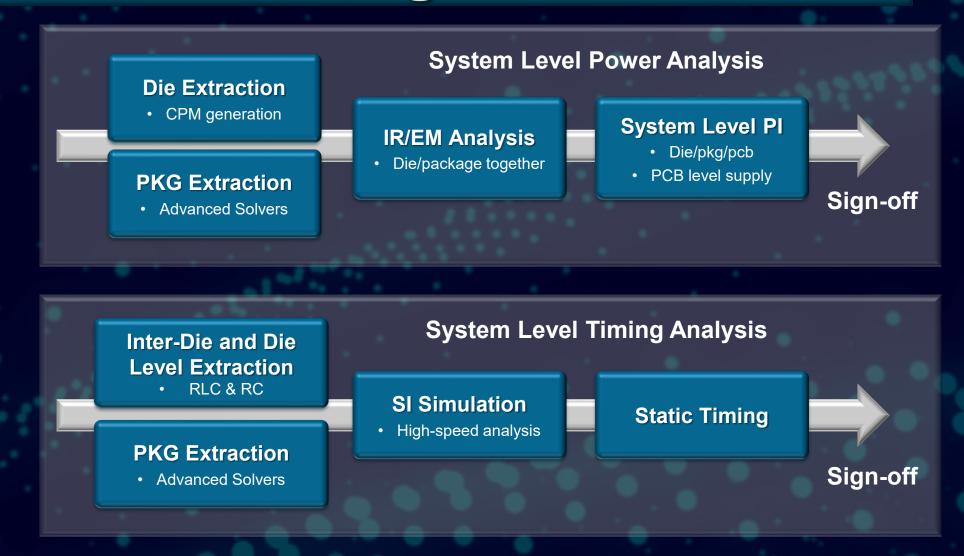

Predictive thermal, stress and reliability

Timing, signal and power integrity

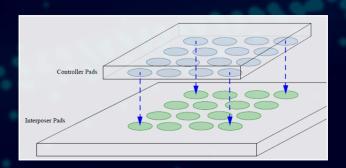

#### DRC/LVS verification workflows

Completed Die

Completed Interposer

Completed Package

PCB Data (optional)

### SI/PI Modeling workflows

Completed Die

Completed Interposer

Completed Package

PCB Data (optional)

#### Thermal / stress workflow

Completed Die

Completed Interposer

Completed Package

PCB Data (optional)

#### **Die Level Thermal**

Detailed thermal modeling

#### Package & System Level Thermal

Substrate and system modeling

#### Thermal / Mechanical Stress Analysis

- Thermal Mechanical stress co-simulation

- Model the entire system from die-level to full system including enclosure

Sign-off

# Needs

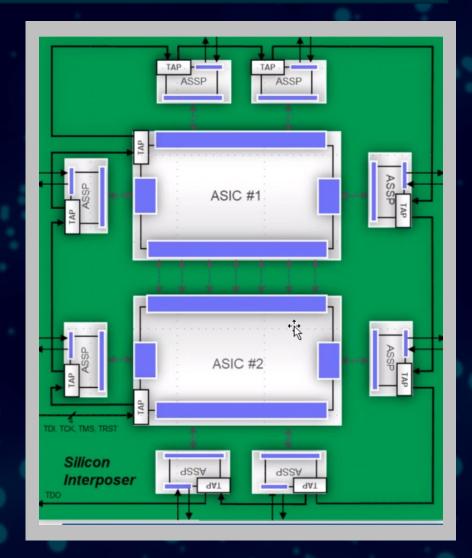

#### **DFT/Test**

**ASIC DFT Planning**

**Interposer DFT Planning**

2.5/3D Level Testing

2.5/3D DFT Verification

### Summary

# HI of chiplets using STCO enables compelling product benefits

- Increased Performance

- Reduced Power

- Lower unit cost/NRE

- Product configurability & hyper-scalability

#### **General Comments & Observations**

- Emerging chiplet Ecoysytem

- Assess HI scenarios early in the product design cycle

- Advanced HI package/ASIC STCO Flow

- Multi Domain Design Planning, Analysis & Signoff

- Predictive multi-domain analysis

Design images courtesy of CEA-Leti

# Thank You