#### Vivek Raghunathan

Senior Principal Engineer & Product Architect, Silicon Photonics Optical Systems Division

#### **Sukeshwar Kannan**

Principal Engineer, Silicon Photonics Packaging Optical Systems Division

#### Han Peng Goh

Director, Platform Development, Silicon Photonics Opticals Systems Division

#### Reza Sharifi

Sr. Manager , Packaging Global Operations

#### **Datacenters: Powering Everyday Cloud Applications**

\$100B Annual Capex Spend by Cloud with 15% CAGR<sup>1</sup>

19.5 Zettabytes of Cloud Data Movement<sup>2</sup>

Per hyperscale datacenter

- > 100k Servers

- > 10k Switches

- > 1M Optical Interconnects

#### Source:

- 1. 650 Group, Cloud Total Market and Forecast Report

- 2. Cisco Global Cloud Index, https://blogs.cisco.com/news/acceleration-of-multicloud-era

- 3. Left: Digital Realty's Loudoun Three campus in Ashburn, Virginia. Photo courtesy of Digital Realty

- 4. Right: Google's Council Bluffs, Iowa Data Center. Photo courtesy of Google

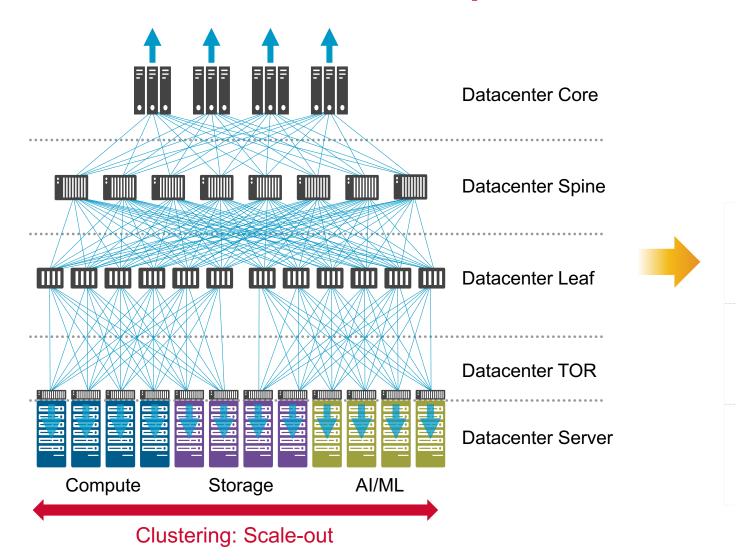

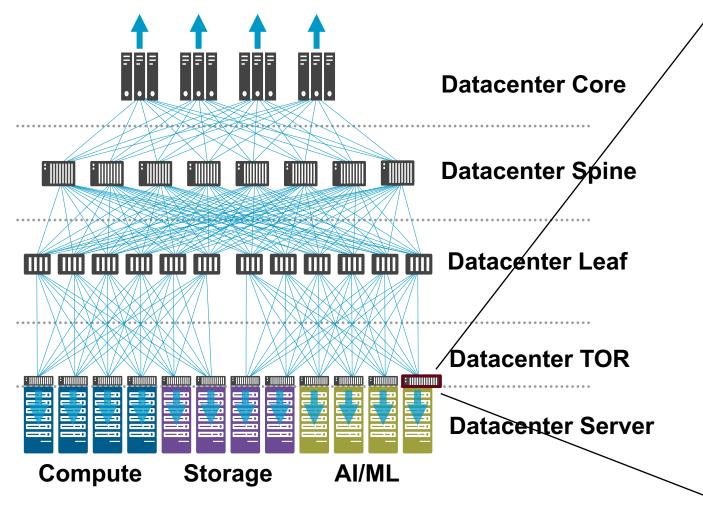

#### **Datacenter Scale-out Requires Massive Fabric Connectivity**

>25%

annual growth for intra-datacenter traffic\*

Compute and storage resources pooled within datacenter and across regional zones

Requires long-reach, low-latency interconnects

Fabric increasing as % spend and power consumption of infrastructure

<sup>\*</sup> Source: CRN, https://www.crn.com/news/data-center/why-public-cloud-data-center-spending-is-at-an-all-time-high

**<sup>₽</sup>** BROADCOM°

#### **Datacenter Scale-out Requires Massive Fabric Connectivity**

<sup>\*</sup> Source: CRN, https://www.crn.com/news/data-center/why-public-cloud-data-center-spending-is-at-an-all-time-high

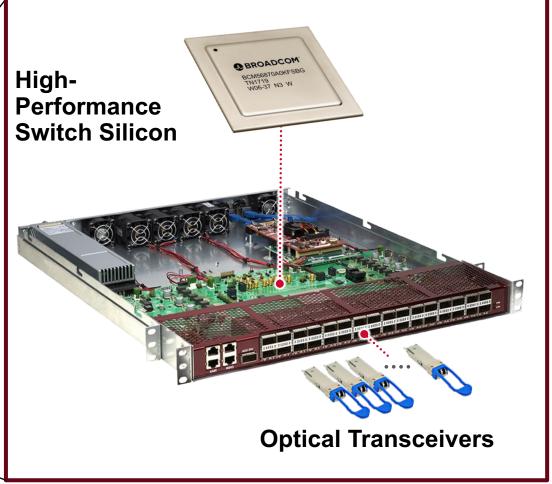

#### Complexity of Each Rack Unit Box in the Datacenter

#### 600M Ports Shipped in 2020<sup>1</sup>

1. E16A\_Ethernet\_Switch\_Layer\_2&3\_WW\_Tables\_1Q21

#### 150M Units Shipped in 2020<sup>2</sup>

2. LightCounting 2Q21 Quarterly Market Update, 17 June, 2021

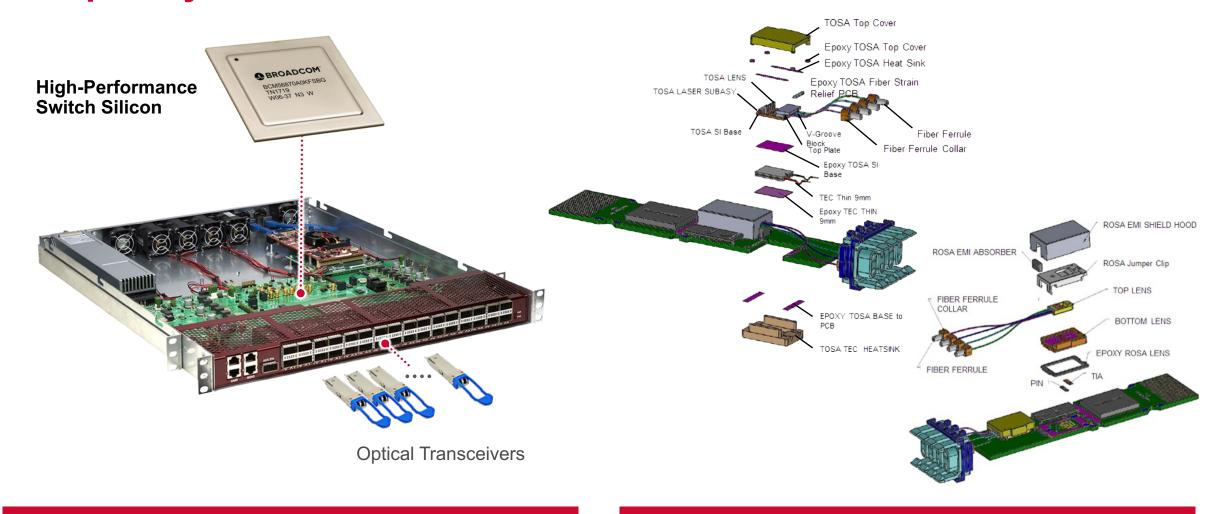

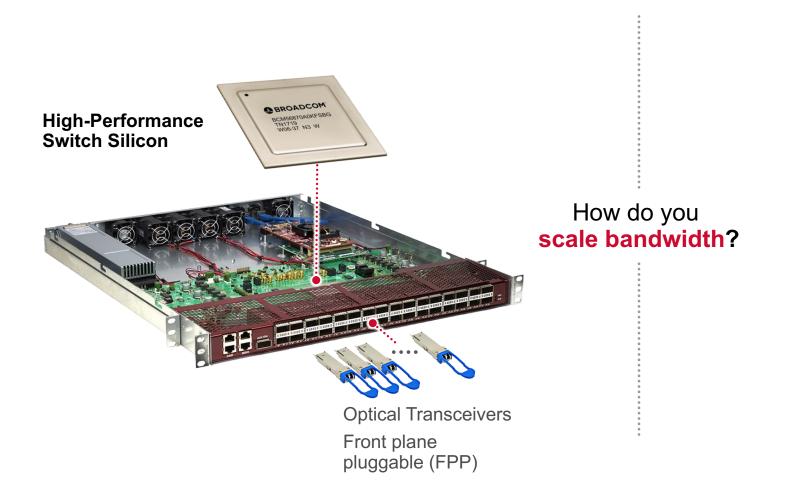

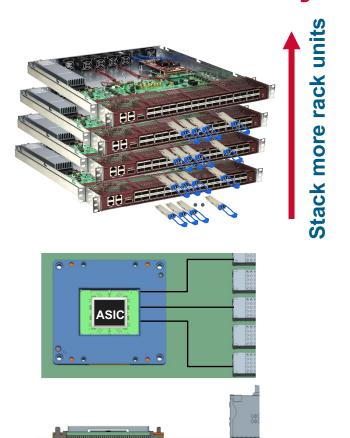

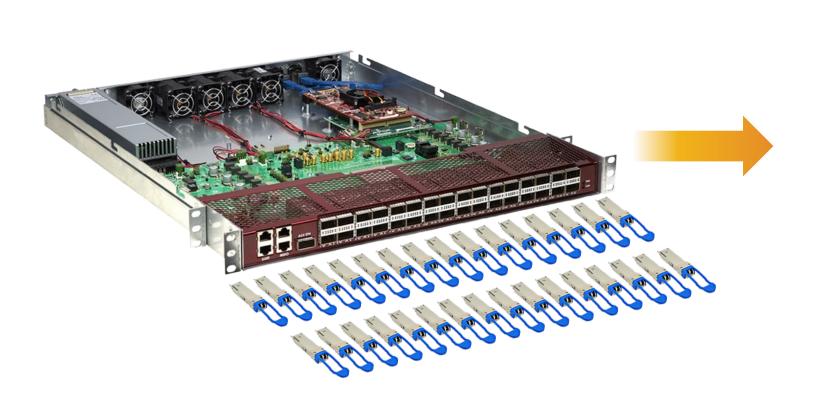

#### **Traditional Rack Unit System Design Does Not Scale Efficiently**

Increase Cu channel speed

Traditional Scaling Approaches Introduces Undesirable Inefficiencies in Power, Size and Cost

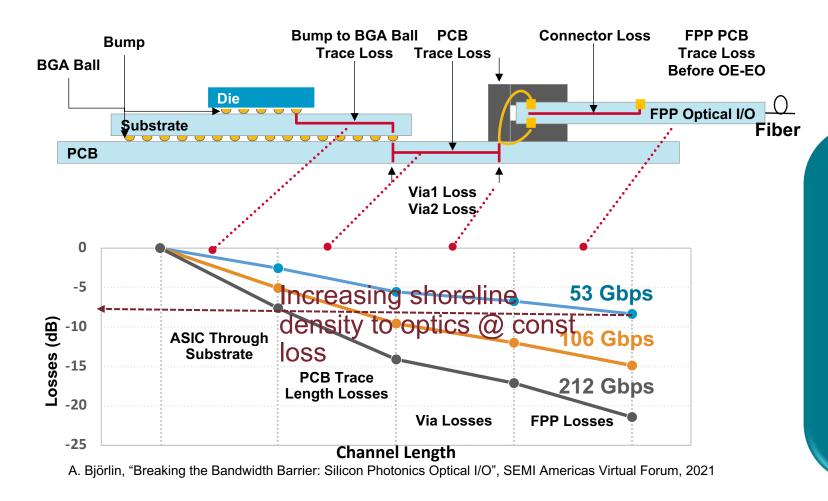

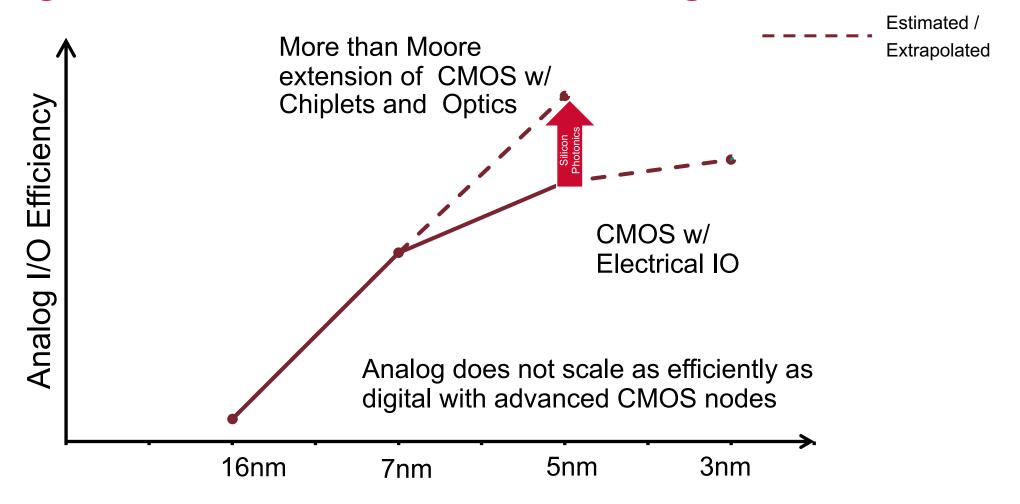

## **Copper I/O Approaching a Limit**

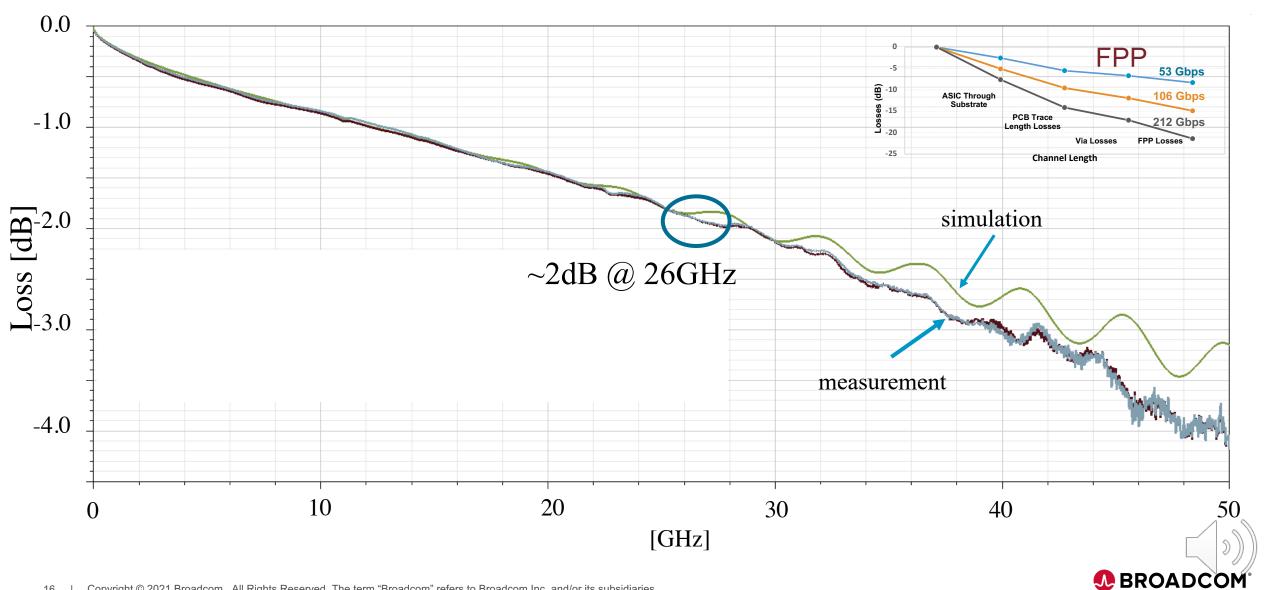

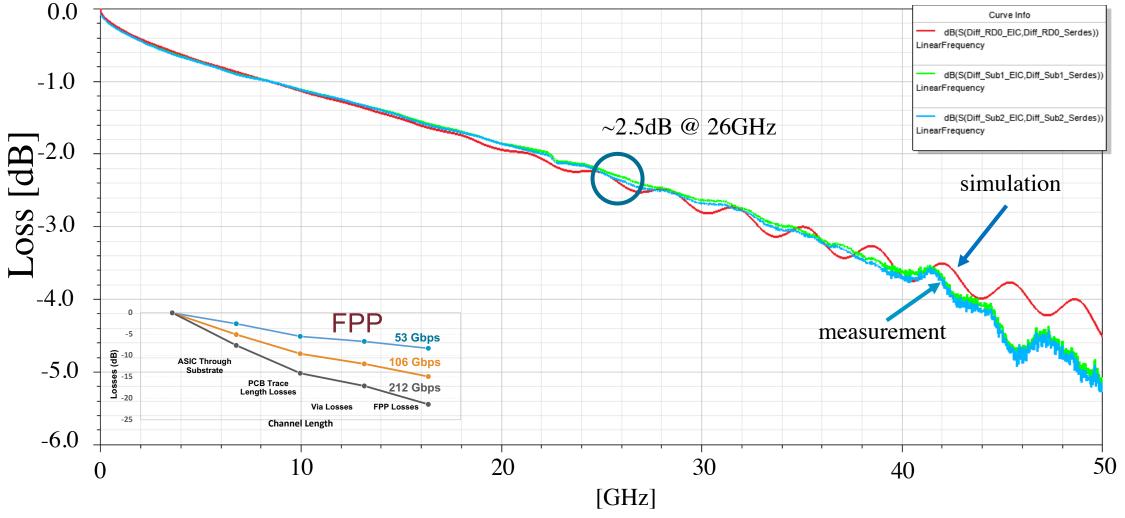

Each interface in the link between ASIC and Optics adds *analog* loss, requiring additional SerDes Power

The losses grow with each generation of interface speed, but analog efficiency is quickly falling behind Moore's Law.

Most importantly, the system doesn't scale efficiently with channel count and BW

Highly Dense, Short RF Channel Connection between ASIC and Optics is more Power Efficient

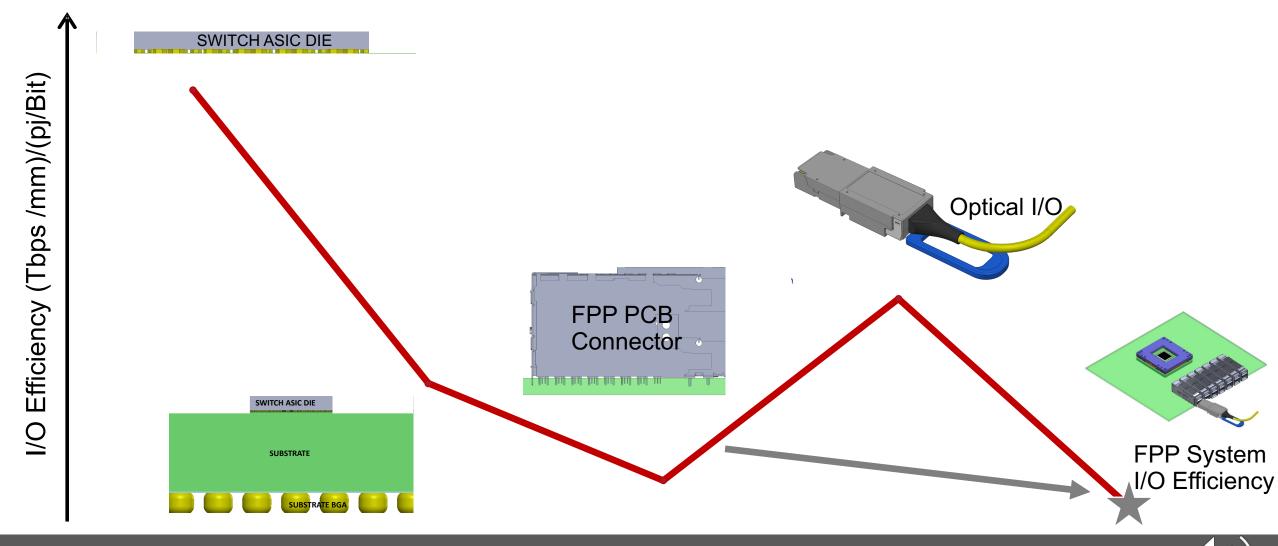

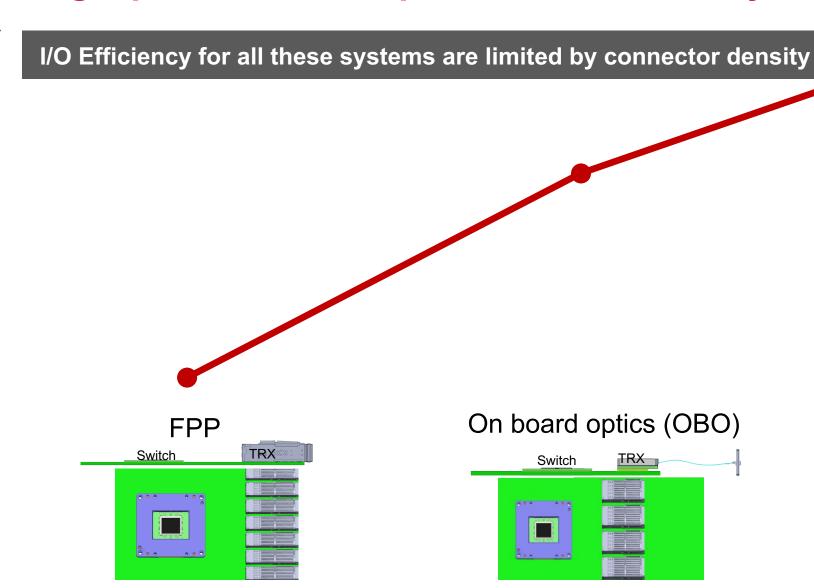

## Analog I/O Efficiency of the Front Plate Pluggable (FPP) System

I/O Efficiency for the FPP System is limited by the FPP PCB Connector

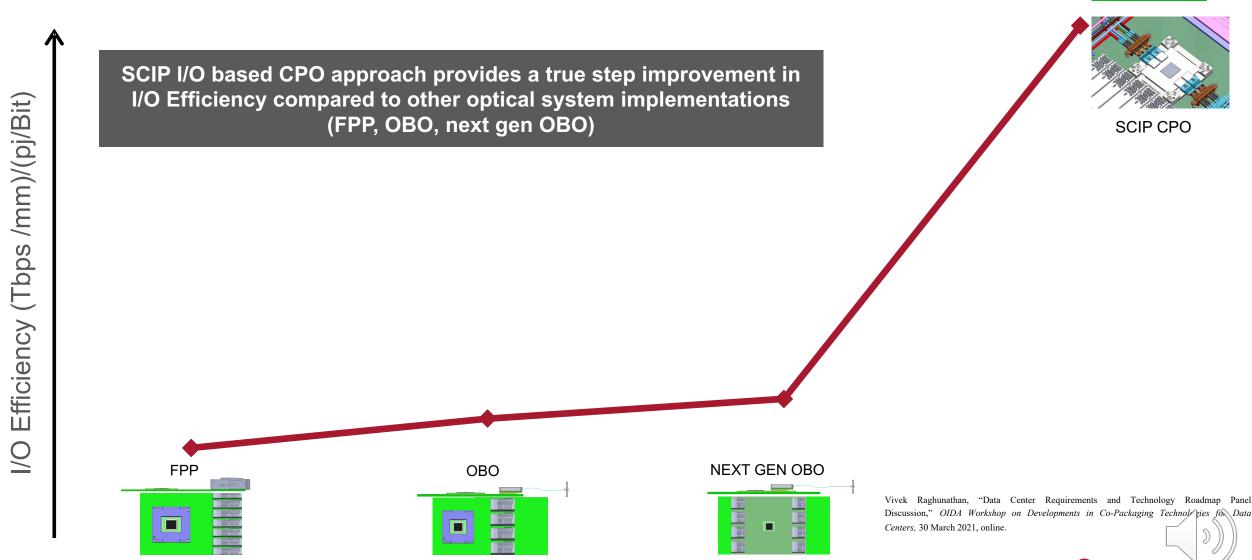

## **Moving Optics Closer Improves I/O Efficiency**

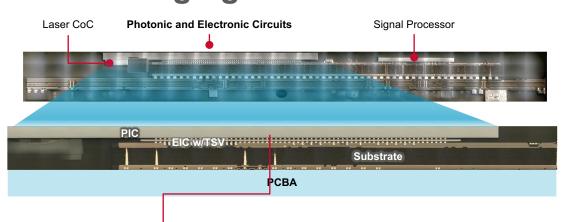

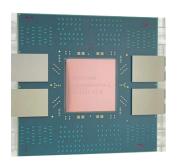

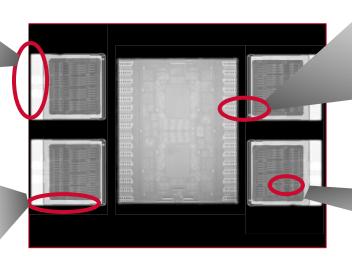

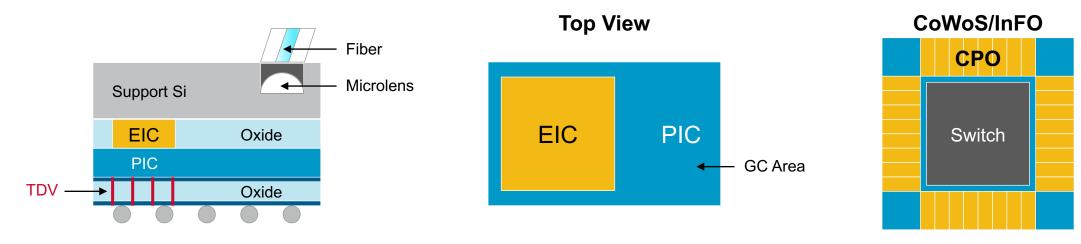

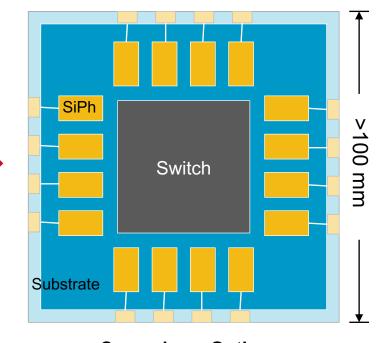

#### Co-packaged Optics (CPO) with Silicon Photonics Chiplets

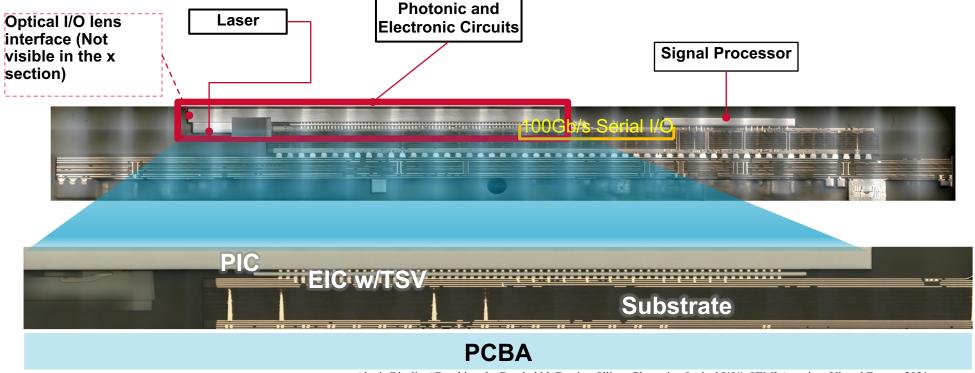

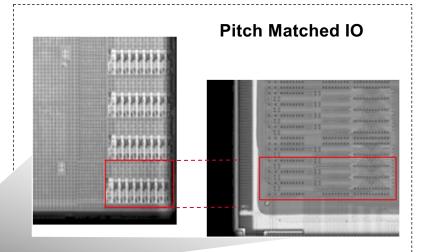

Top View: Multi-Chip Package with ASIC die and Silicon Photonics Chiplets in Package (SCIP) providing optical I/O

Integrated Silicon Photonics Switch Chiplets

Cross-section View: CPO with SCIP I/O

#### **SCIP** based CPO for I/O Efficiency Improvement

## **SCIP Integration Enables High Density System Design**

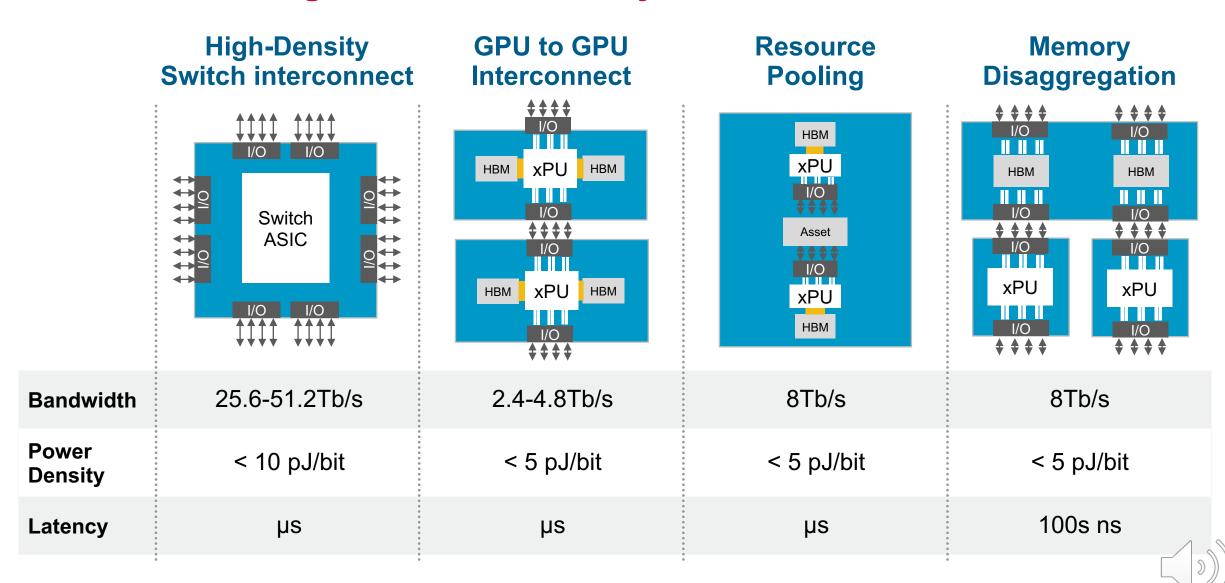

#### **Architectural Migrations Enabled by SCIP I/O**

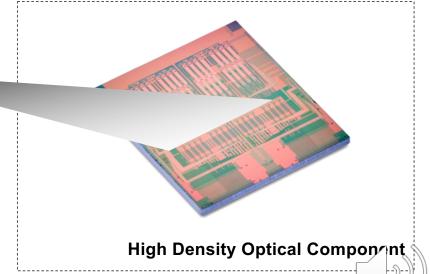

#### **SCIP I/O Platform Building Blocks**

# ASIC Silicon

- Core switch,

SerDes and DSP in leading node

- Sustained generational differentiation

# Mixed Signal IC

Power and performance optimized in both SiGe and CMOS

# Optical Devices & Fabs

- 50M lasers/year from internal fabs

- High-volume optical manufacturing

- High-power, multi-wavelength sources

# Advanced Packaging & Test

- TSV/2.5D/3D integration

- CoW/CoC Assy

- MCM Packaging

- Reflow compatible optics assembly

- Wafer-level test

- Fiber Connector

# Silicon Photonics

- High-density

Photonics

Integrated Circuit

(PIC) design

- Modulators and PDs in silicon

- Low-loss SOI waveguides

Key Technology Integration needs to maximize I/O efficiency

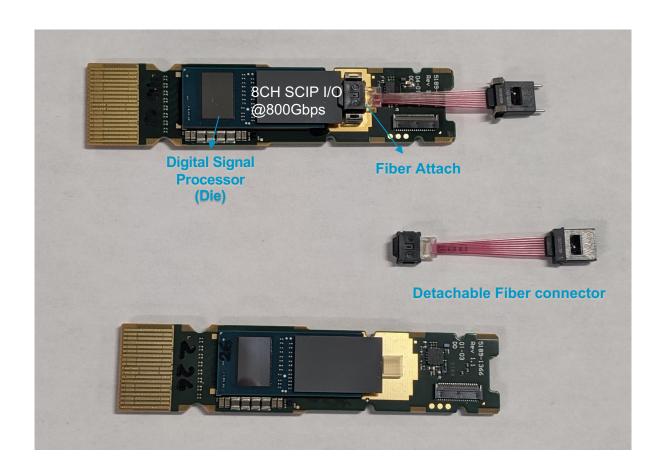

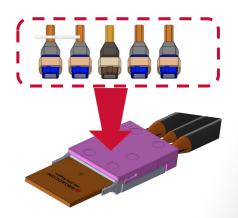

#### 8CH SCIP I/O in a traditional transceiver form factor

- 8CH SCIP CPO in a Transceiver Module

- Silicon Photonics engine is co-packaged with a Digital Signal Processor die

- 100Gb/s Serial Interface between DSP and Silicon Photonics Engine Chiplet

- ~12mm x 26mm MCM Package

- Integrated laser with custom detachable optical connector interface

- 8CH SCIP based CPO is solder reflowed to the PCB demonstrating the reflow capability of Broadcom's optical I/O.

#### Channel Tx – Diff IL: 2dB for SCIP vs 16dB for an FPP

#### Channel Rx – Diff IL: 2.5dB for SCIP vs 16dB for an FPP

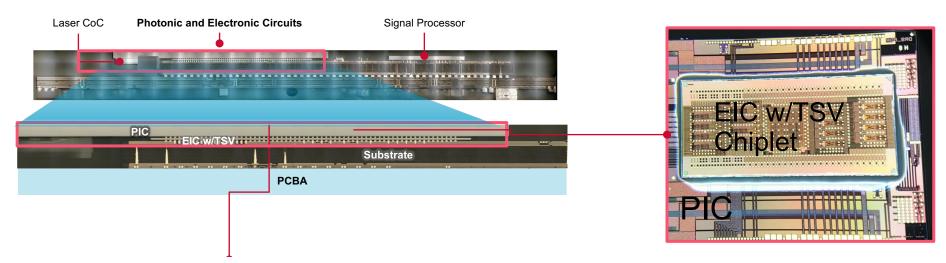

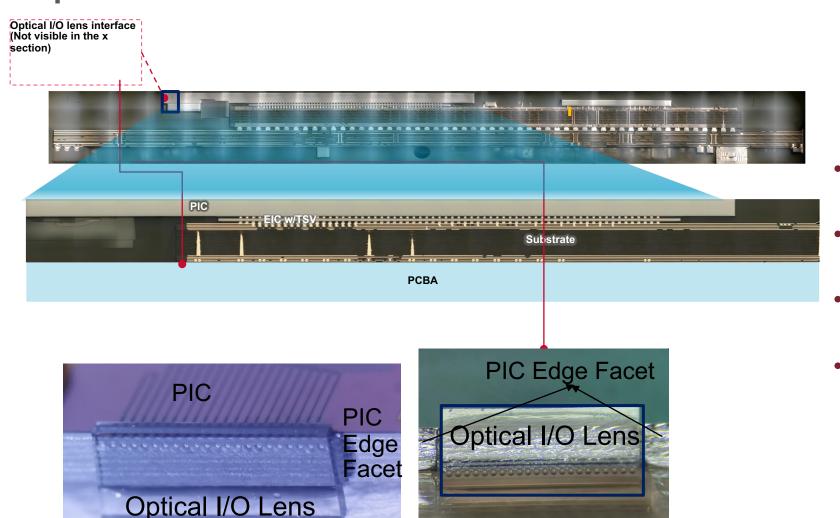

## The Anatomy of a Fully Integrated 8CH Silicon Photonics Engine

Alexis Björlin, "Breaking the Bandwidth Barrier: Silicon Photonics Optical I/O", SEMI Americas Virtual Forum, 2021

- Digital Signal Processor with 8 x 100Gbps Analog Serial I/O to SCIP

- Silicon Photonics Chiplets in Package (SCIP) Include

- Photonic Integrated Circuits (PIC) for optical light modulation and light detection

- EIC w/TSV Chiplet for Electrical to Optical Conversion and Optical to Electrical Conversion

- Laser for Optical power supply

- Optical I/O lens interface for light coupling in and out of the detachable fiber connector

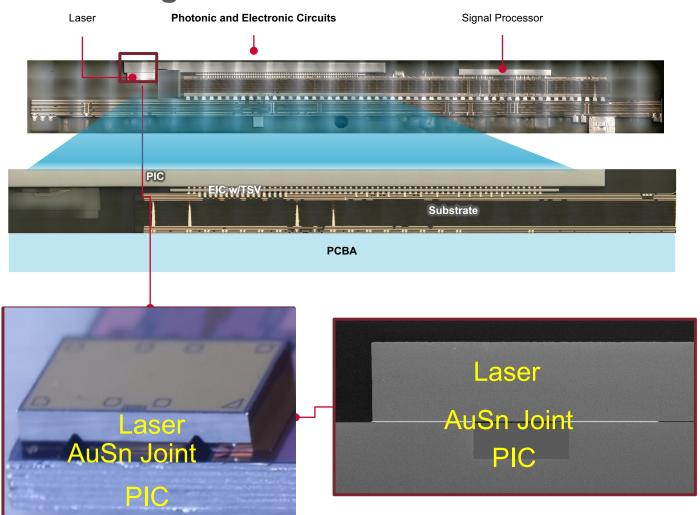

#### **Laser Integration**

- Hybrid Integration of III-V Laser on a PIC wafer

- Chip on Wafer of Laser to PIC wafer

- AuSn Eutectic bonding process

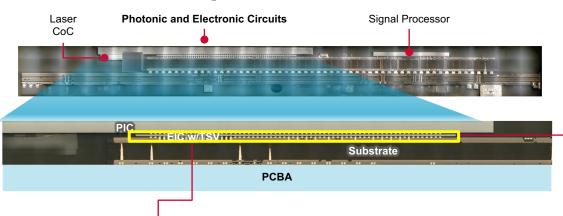

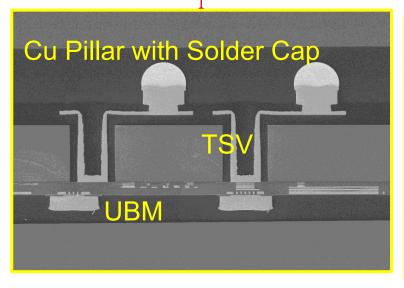

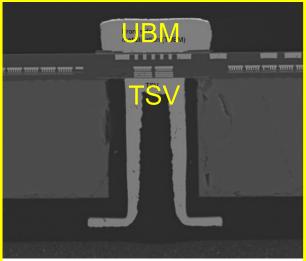

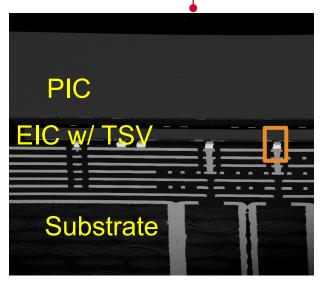

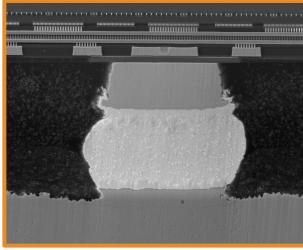

#### **EIC w/ TSV Chiplet**

- TSV Last Integration on BiCMOS wafer for 3D integration

- ~75 um thin wafer

- 1L RDL and Cu pillar w/ Solder Cap on one side and UBM on the other side

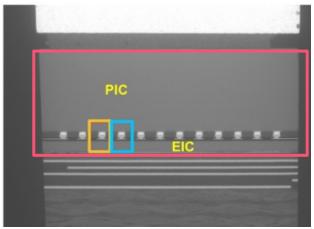

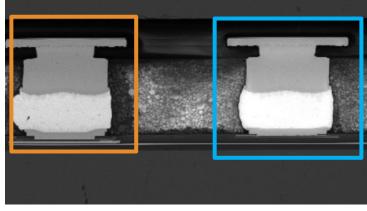

#### PIC-EIC CoC

- CoC bonding of EIC-PIC using TC-CUF Process to form a Silicon Photonics Engine Chiplet (SCIP I/O)

- 130um min bump pitch

#### **Optical I/O Lens**

- Optical I/O lens assembled to PIC edge facet using Epoxy

- Light Coupling interface for fiber connector

- 127 um I/O Lens/ Fiber Channel pitch

- Reflow compatible optical lens assembly

# SCIP I/O: Advanced Packaging Technology Building Block: MCM Packaging MCM Packaging

- Co-packaging 8CH Silicon Photonics Engine Chiplets with Digital Signal Processing (DSP) Chiplet

- 8 x 100Gbps Serial Interface between the DSP and SCIP

- 2 Die MCM Assembly using standard reflow process

- 150um min bump pitch

#### Scaling Core Technologies for 32CH SCIP in a 5 Die MCM

**High Density Optical Connector**

High Density Integration (reduced Interconnect length)

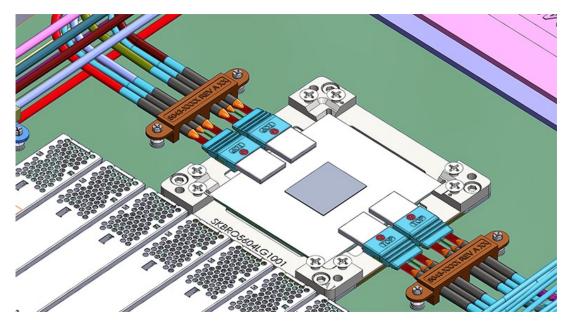

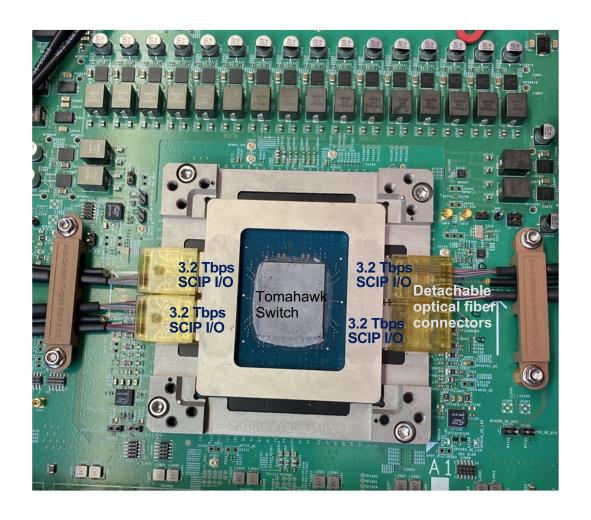

#### Platform Scaling to 128 CH using 4 x 32 CH SCIP I/O

- CPO Switch with 256 Channels of 100G Serial I/O in "Half Electrical I/O" and "Half Optical I/O" configuration with 128 Channels each

- 4 x 32CH Silicon Photonics engine is copackaged with a Tomahawk4 Switch ASIC to provide optical I/O

- 67.5 mm x 75mm MCM Package

- External Laser Providing Optical Power to Silicon Photonic chiplets

- Detachable Fiber connectors with 3 different fiber types for Tx, Rx and Laser

## Scaling SCIP I/O based CPO

XPUs w/ Optical SCIP CPO with integrated SiPh offers 3 independent vectors for scaling: Integrated  $\lambda$  mux/demux **Electrical I/O density scaling with advanced packaging** Power-Performance-Area scaling w/ CMOS node Electrical IO scaling with CMOS node and CMOS w/ Electrical I/O Advanced Packaging SWITCH ASIC DIE CMOS w/ Optical IOs (CPO Gen 2) **NEXT GEN OBO** OBO Humboldt Vivek Raghunathan, "Data Center Requirements and Technology Roadmap Panel Discussion," OIDA Workshop on Developments in Co-Packaging Technol vies for Data 25.6T Centers, 30 March 2021, online

CMOS w/ Optical IOs (CPO Gen 1)

BROADCOM

#### SCIP Leading 'More than Moore' CMOS IO Scaling

Silicon Photonics platform provides "More than Moore" approach to improve Analog I/O efficiency

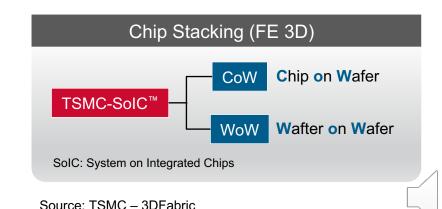

## Silicon Photonics Packaging-Foundry Investment Trends

- Low insertion loss SoIC interface (hybrid bonding) between EIC/PIC & TDV (through dielectric via) in PIC

- Exciting development and investment in chip stacking wafer to wafer and chip to wafer bonding

Source: TSMC - Hotchips 2021

GlobalFoundries, Arm Close in on 3D Chip Integration > 3D interconnects could shorten delays within processor cores

Source: GF - Face-to-face Hybrid Wafer Bonding

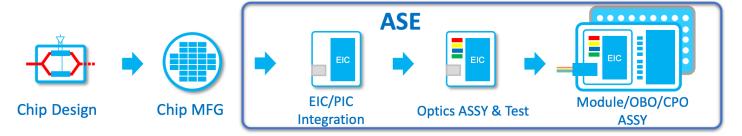

## Packaging is King – Silicon Photonics OSAT Investment Trends

- OSATs increasing investments in processes specific to optical chiplet packaging

- Examples: KOH V-groove, fan-outs, fiber attach

#### **Post-CMOS Process**

- Cu-pillar bumping

- UBM metallization

- WL dam process

- Oxide etching & DRIE

- Au mirror process

- AuSn process

- ARC film process

- KOH V-groove

- Via last process

- Fanout process

#### **Wafer Level Assembly**

- CoW process

- Wafer level WB assembly

- High accuracy laser attachment

- Optical components placement

#### **Wafer Level Test**

- Wafer sorting

- Probe card design

- Test program service

- WL optical test

#### oEngine Assembly

- SMT process

- Substrate level FC/WB

- Encapsulation

- Fiber attachment

- Housing assembly

- Module test

#### **Lab Service**

- · Electrical/Optical

- Thermal/Stress

- Material/Chemical/FA

#### **Integrated on Substrate**

**Co-package Optics**

Blue = Specific for optical packaging

#### **Summary and Ecosystem Call-to-Action**

- SCIP based CPO with integrated silicon photonics provides a step improvement in I/O efficiency of next gen high speed interfaces

- Chiplet ecosystem partner investment in Foundry, EDA, Assembly and Test is crucial

- SCIP platform can scale to serve the I/O needs beyond ethernet switching to next generation compute and memory system connectivity