#### CU WIREBOND TECHNOLOGY IN 16FFC HIGH PERFORMANCE AUTOMOTIVE RADAR PROCESSOR WITH IR DROP REDUCTION METHODOLOGY

Tu Anh Tran, Jasmine Lim, YK Au, MJ Song, Mollie Benson MARCH 16, 2023

SECURE CONNECTIONS FOR A SMARTER WORLD

#### **PUBLIC**

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2023 NXP B.V.

#### CONTENT

- What is IR drop?

- Methods for IR drop reduction

- IR drop simulation and results

- SSB (Stand-off stitch bond) development & challenges

- Product package reliability

- Board level reliability (BLR)

- Summary

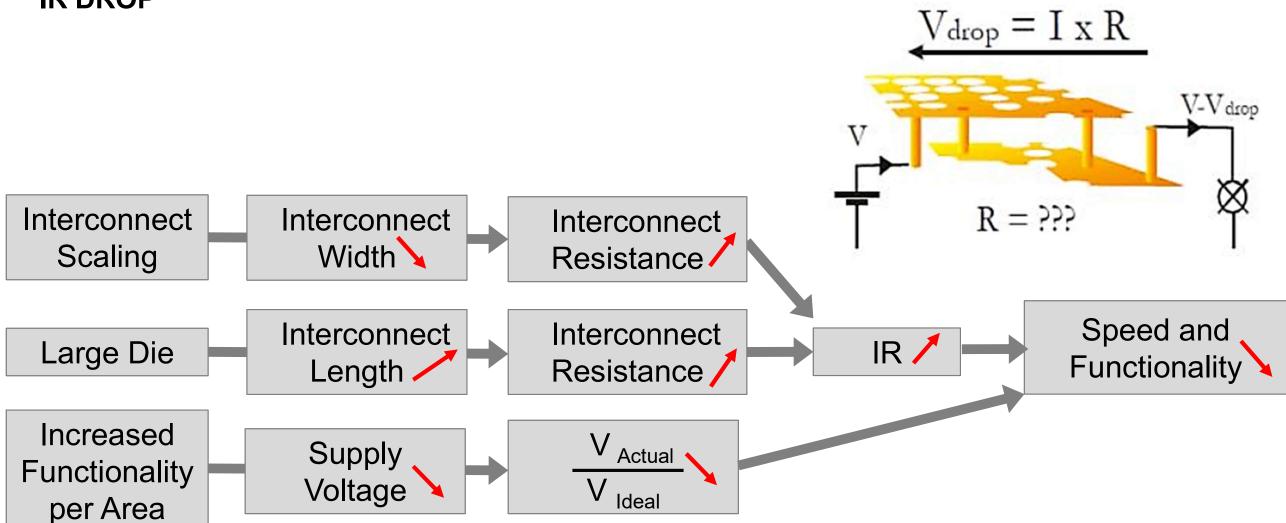

### **IR DROP**

#### STATIC IR DROP REDUCTION METHODS

#### Die Level

- Increase metal width of supply connections

- Increase BEOL wiring layers

- Increase BEOL thickness

- Increase Al pad thickness

#### Package Level

- Flip chip: Bumps or Cu pillars across PDN

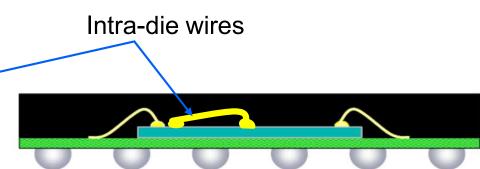

- Wire Bond: Add intra-die wires to connect peripheral supply pads to active devices in die core area

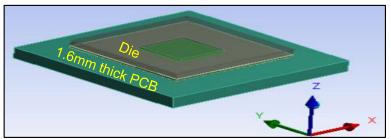

#### PRODUCT DESCRIPTION

- Function: Auto radar processor

- Die: 30mm2 in 16FFc

- Power: 2W

- IR drop 30% off target

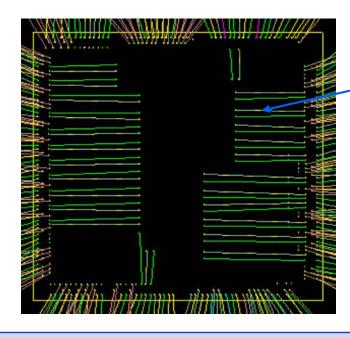

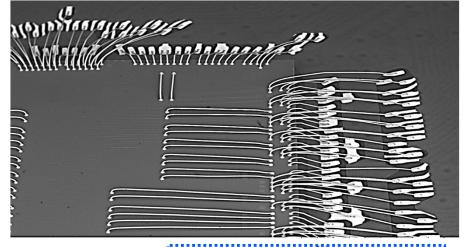

- Intra-die bond pads added at periphery and die core area

- 49 intra-die wires (24 VDD and 25 VSS)

- Package: 14x14mm MAPBGA

- Substrate: 2-layer

- Wire: 20um Pd-Cu

#### IR DROP SIMULATIONS

#### **Quantity of Intra-die Wires**

# | COCCOCCCC| COCCCC| C

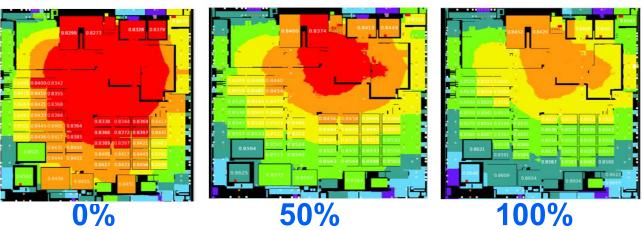

#### **IR Drop Mapping Simulation**

| Intra-die Wire<br>Quantity | Intra-die<br>Wirebond<br>Count | No. of Instances > 40mV | Worst IR Drop<br>(VDD+VSS)<br>(mV) |

|----------------------------|--------------------------------|-------------------------|------------------------------------|

| 0%                         | 0                              | 100K +                  | 56.6                               |

| 50%                        | 26                             | 100K +                  | 46.2                               |

| 100%                       | 49                             | 30                      | 40.4                               |

Adding 49 intra die wires enables 30% IR drop reduction.

#### IR DROP EMPIRICAL RESULTS

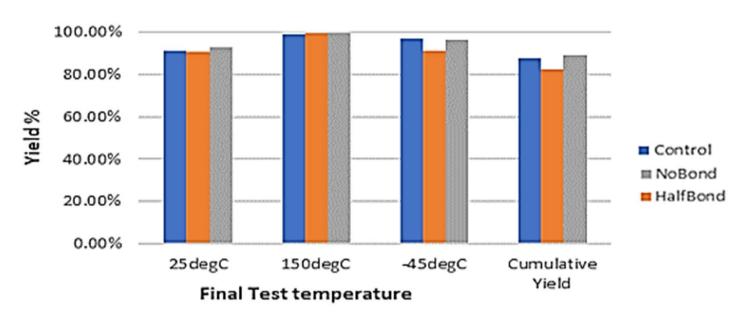

#### **Final Test Yield**

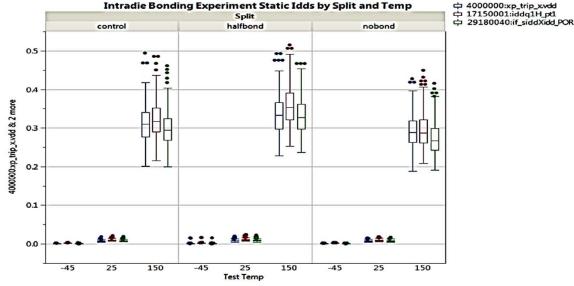

#### Trip Idd, iddq, Static Idd

- Actual parts with 0%, 50% and 100% intra-die bonds did not show significant differences in test yield or parametric characterization.

- Nominal wafer was used. IR drop would have been more significant if worst case wafer was used.

- Intra-die wires are kept in the radar processor to provide better IR drop margin.

001329

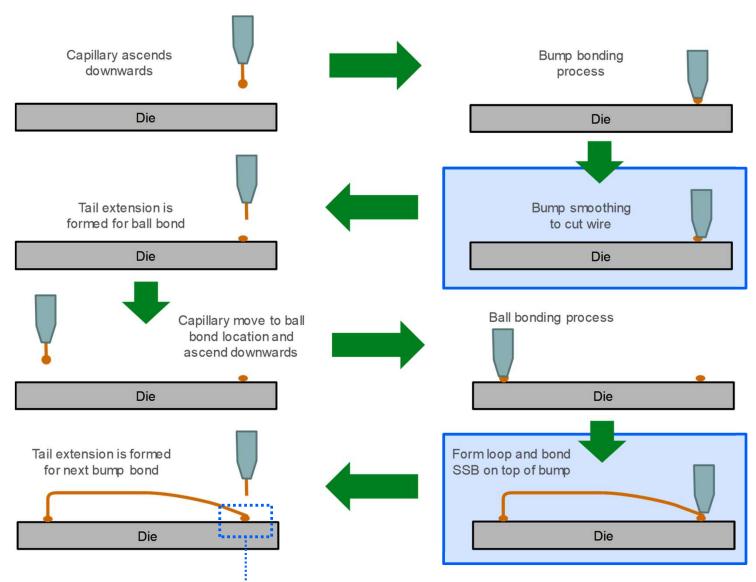

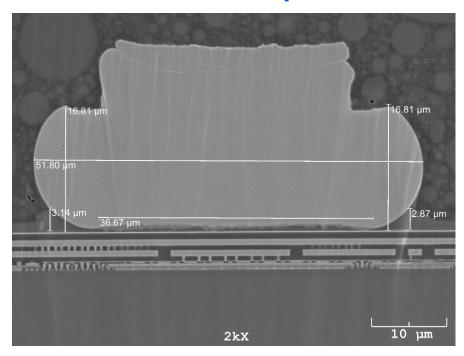

#### SSB (STAND-OFF STITCH BOND) PROCESS

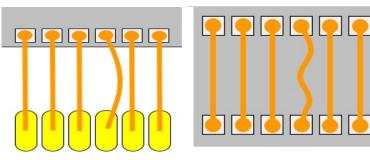

# SSB bonding is required when a design has "2<sup>nd</sup> bond" that needs to be placed on the die.

#### **SSB Wire Bonding Process**

#### **SSB DEVELOPMENT**

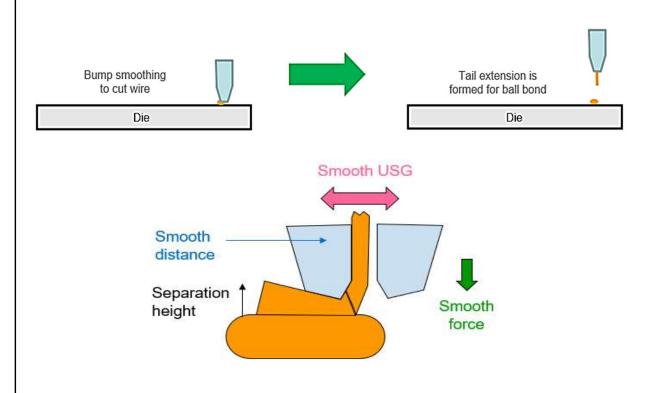

Bump Smoothing – Cutting wire after bump bond, and preparing tail for ball bond

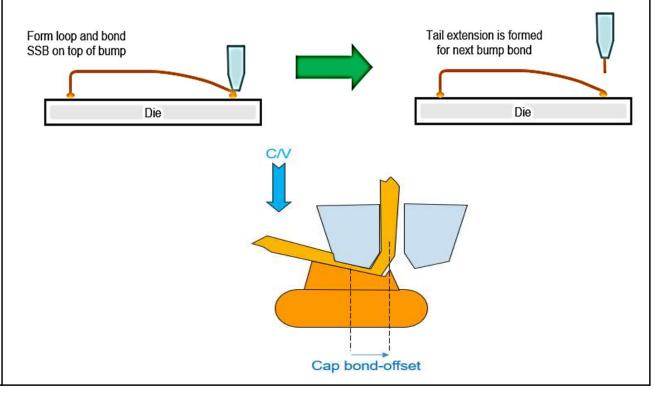

**SSB Wire Bonding** – Bonding of stitch bond on top of bump, and preparing tail for bump or ball bond (depending on next wire being normal or intra-die wire)

- Bump smoothing optimization is required to eliminate short or long tail event after bump.

- 2<sup>nd</sup> bond parameter optimization is required for SSB to eliminate non-stick and short tail events.

#### **OPTIMIZING SSB BONDING PROCESS**

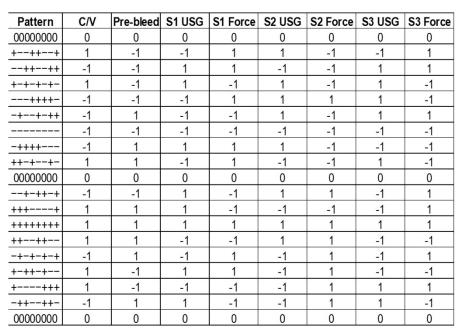

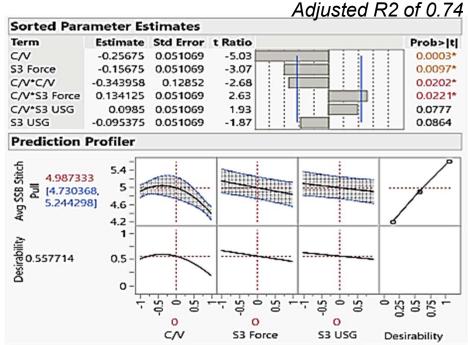

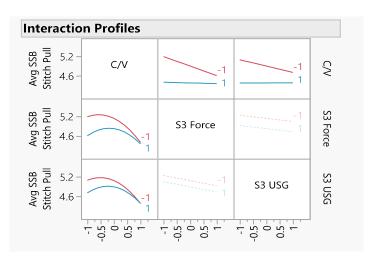

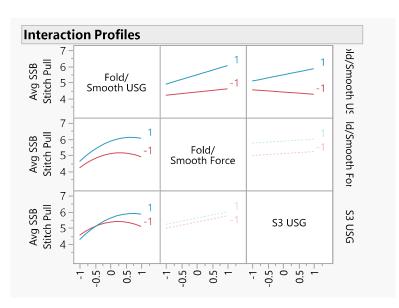

DOE 1: Identify SSB parameters that can improve SSB stitch pull strength

DOE design: 8-factor 2-level fractional factorial DOE with 3 center points (19 cells)

R2 of 0.82

- 2 significant factors for higher SSB stitch pull strength: C/V and S3 force

- Lower C/V can yield higher stitch pull due to thicker stitch formation.

#### **OPTIMIZING BUMP SMOOTHING**

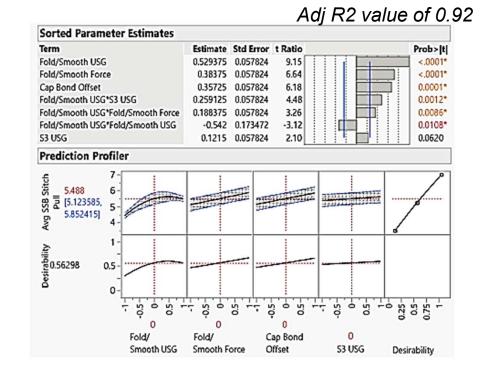

DOE 2: Identify bump smoothing parameters that can improve SSB stitch pull strength

DOE design: 6-factor 2-level fractional factorial DOE with 2 center points (18 cells)

Cap Fold/ Fold/ Smooth Pattern S3 USG S3 Force **Bond** Smooth Smooth **Distance** Offset USG **Force** 000000 0 0 0 -1 -1 -1 -1 1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -++--+ -1 -1 -1 -+-+-+ -1 1 1 -1 -+++-1 1 -1 -1 +-++-+ +++----1 -1 -1 -1 -1 -1 -1 1 -1 -1 --++---1 -1 1 -1 1 1 --+-++ -1 -1 1 ++--++ +++++ -1 -1 -1 +--+-1 +-+-+--1 -1 -1 -1 1 1 -1 -1 ++-+---1 ---+++ -1 -1 000000

R2 value of 0.95

3 significant factors for higher SSB stitch pull strength: Fold/Smooth USG, Fold/Smooth Force and Cap Bond Offset

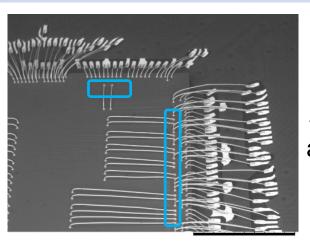

#### INTRA-DIE WIREBOND MANUFACTURING CHALLENGES AND MITIGATIONS

Wire Looping: Wire touching exposed metal on die surface causing electrical failure

Wire Straightness: Wire shorting due to wire sway and Sing due to stitch bond being formed on the same plane as 1st bond

Bump Smoothing: Excessive bump smoothing results in short tail errors, while insufficient smoothing results in long tail errors.

- Looping optimization to form a lowest possible loop height without wire sagging near 2<sup>nd</sup> bond region (SSB side)

- Different looping parameters for different wire lengths

- Establish design rules for minimum wire pitch for intra-die wires

- SSB bump optimization DOE

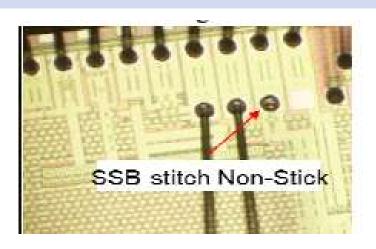

- Monitor bump and SSB defects: Bump NSOP, Short/long tail after bump, SSB stitch NSOB and SSB stitch short tail

#### INTRA-DIE WIREBOND MANUFACTURING CHALLENGES AND MITIGATIONS

Bump placement: Capillary's reverse motion hitting on other wires during intra-die ball looping trajectory

#### **SSB Bump Oxidation:**

Oxidation causing NSOL and reduced interconnect reliability

Yield Loss: SSB process doubles the failure opportunity as compared to standard bonding.

- Place SSB bumps near peripheral pads and intra-die balls in die interior

- Use Pd coated Cu wire

- Use Bump-bond-bump-bond concept for intra-die wires or control delay time before SSB

- Optimized intra-die wire bond recipe can produce low defect rate.

SSB bump at die edge

#### PACKAGE RELIABILITY RESULTS – ELECTRICAL TESTS

| Reliability<br>Stress | Conditions | Readpoints |          | Electrical<br>Test Results |            |

|-----------------------|------------|------------|----------|----------------------------|------------|

|                       |            | 1X         | 2X       | 3X                         |            |

| uHAST                 | 110C/85%RH | 264 hrs    | 528 hrs  | 792 hrs                    |            |

| THB                   | 85C/85%RH  | 1000 hrs   | 2000 hrs | 3000 hrs                   | $\bigcirc$ |

| HTSL                  | 150C       | 1000 hrs   | 2000 hrs | 3000 hrs                   |            |

| AA-TC                 | -55/150C   | 1000 cyc   | 2000 cyc | 3000 cyc                   | $\bigcirc$ |

Package BOM passes electrical test up to 3X readpoints of AEC Grade 1.

#### PACKAGE RELIABILITY RESULTS – AEC Q006 CU WIRE BOND CONSTRUCTION ANALYSIS

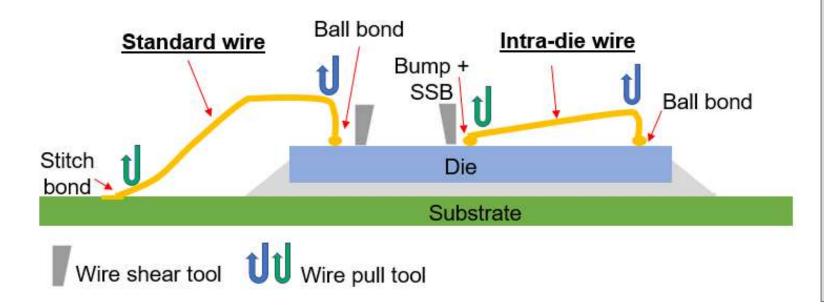

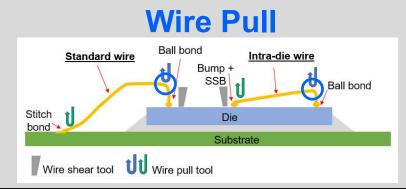

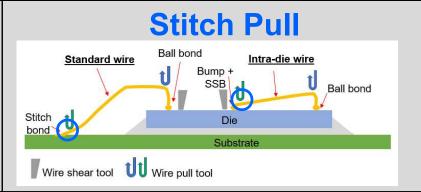

#### **Standard wire**

- Ball side ball shear

- Ball side wire pull

- Stitch side stitch pull

#### **Intra-die Wire**

- SSB bump ball shear

- Ball side wire pull

- SSB stitch stitch pull

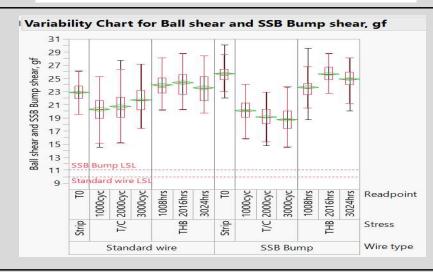

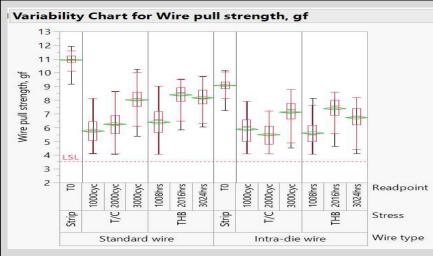

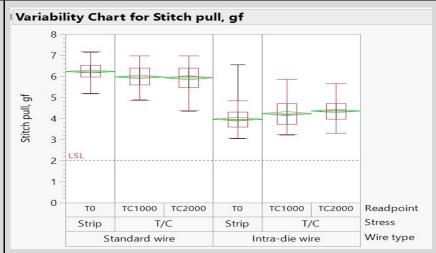

#### PACKAGE RELIABILITY RESULTS – WIRE BOND INTEGRITY

# Standard wire Ball bond Bump + SSB Ball bond Bump + SSB Ball bond Substrate Wire shear tool Wire pull tool

- Passed LSL with preferred failure mode of shearing through Cu ball. No significant degradation after 3X tests.

- Higher T0 ball shear in SSB bump due to larger bump size.

- Passed LSL with preferred failure mode of break at wire.

- Lower T0 wire pull of intra-die wire due to wire trajectory.

- Lower results with wide variation after package stresses due to chemical decapsulation.

- Passed LSL with preferred failure mode of break at stitch.

- Lower T0 SSB stitch pull strength due to intra-die wire trajectory and stitch formation on bump.

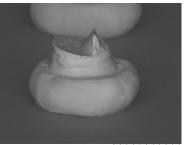

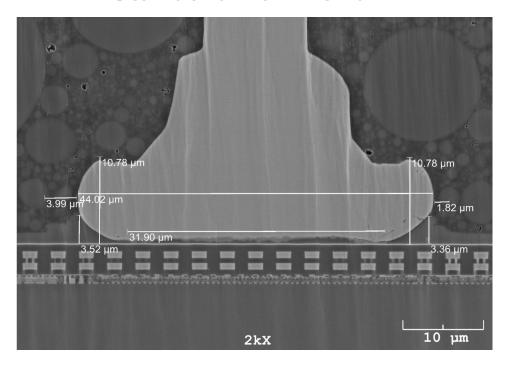

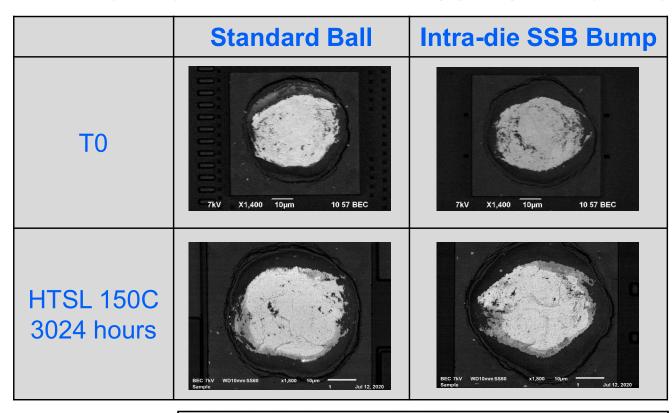

#### PACKAGE RELIABILITY RESULTS – IMC FORMATION

#### **Bond Ball Cross Sections 2016 hour HTSL 150C**

#### **Standard Ball Bond**

**SSB Bump**

Minimal interfacial crack is observed at Cu-Al IMC region. No BEOL damage is observed.

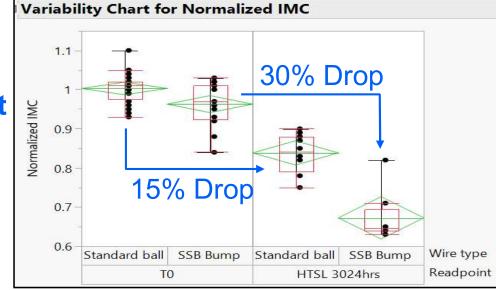

#### PACKAGE RELIABILITY RESULTS - IMC DEGRADATION

- Planar analysis is used to quantify IMC coverage and degradation after package stress.

- SSB bump IMC degradation is faster than standard ball.

- Even with IMC degradation, the remaining IMC remains strong.

### IMC Contact Diameter

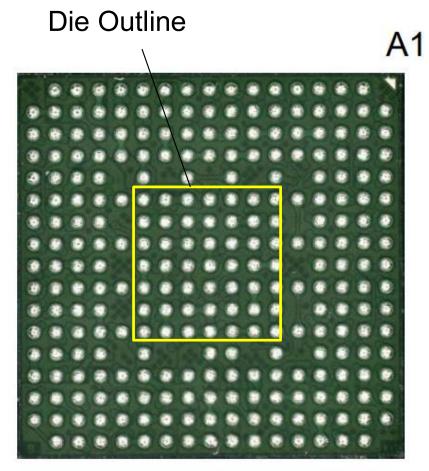

#### **BOARD LEVEL RELIABILITY (BLR)**

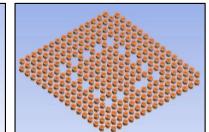

**Package Bottom View**

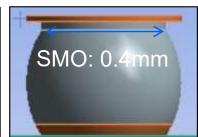

- Test Vehicle :

- Die size: 30mm2

- Package: 14mm x 14mm 0.8mm pitch MAPBGA

- Die:Package: 15%

001340

- Substrate: 2-layer

- Solder ball: 0.4mm SnAg

- Depopulated 4 corner balls

- PCB: FR4, 8 Cu layers, 1.6 mm thick, 0.34mm Cu pads, NSMD

- Purpose: To continuously monitor the solder joint integrity during thermal cycling

- Concern: Depopulated 4 corner balls may increase the fatigue damage in the neighboring corner balls.

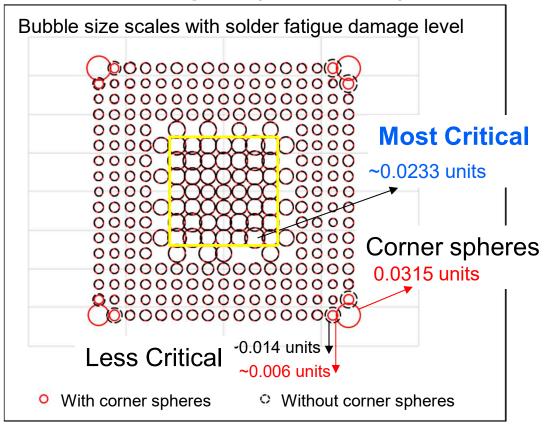

#### **BOARD LEVEL RELIABILITY (BLR) SIMULATION**

#### **Creep Strain Energy Density** per Cycle (-40C/125C)

- Damage parameter: Creep strain energy density

- With corner ball depop, increased damage in neighboring corner balls is minimal.

- Solder balls near die edge and depopulated BGA area experience highest level of damage in board-level cycling.

19

001342

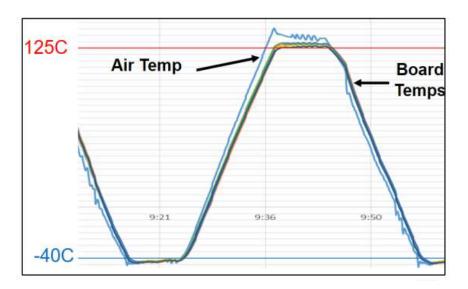

#### **BLR TEST METHOD**

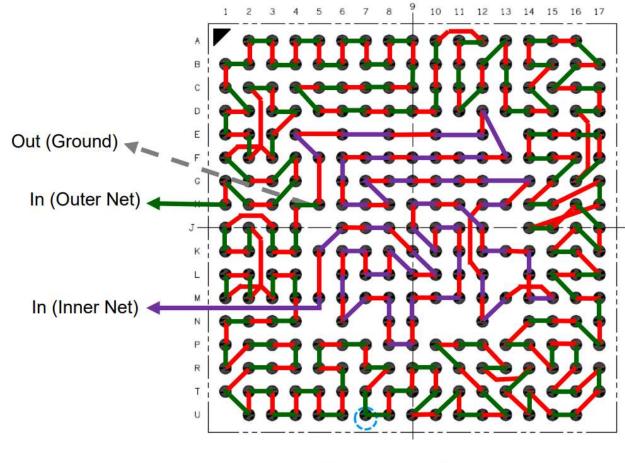

#### **Daisy Chains through Substrate and PCB**

Pkg Schematic (M1 & M2)

PCB Routing (Outer Net)

PCB Routing (Inner Net)

( No Connect

Single Chamber Thermal Cycling (-40/125°C, 15 minute ramp and 15 minute dwell, 1 hour cycle)

Continuous in-situ resistance monitoring with failure when resistance  $\geq 1000\Omega$ .

20

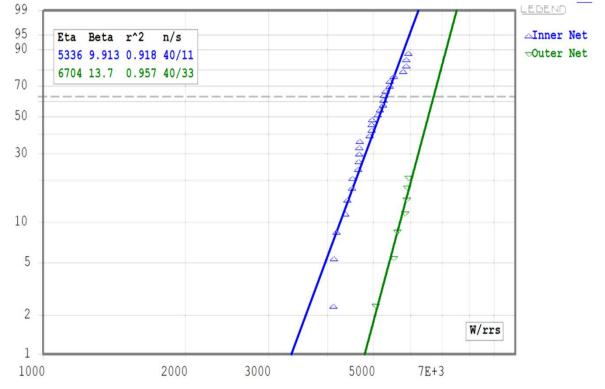

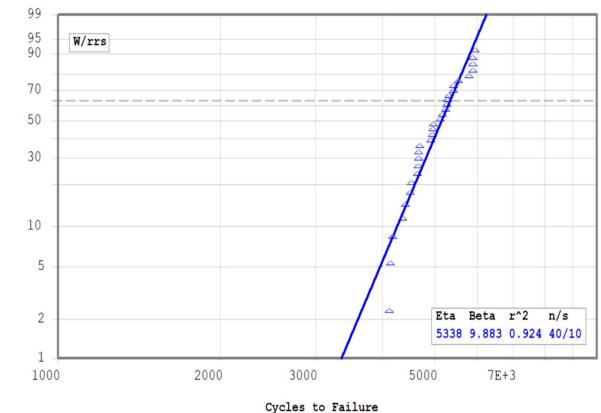

#### **BLR WEIBULL PLOTS**

Cycles to Failure

#### **Combined Nets**

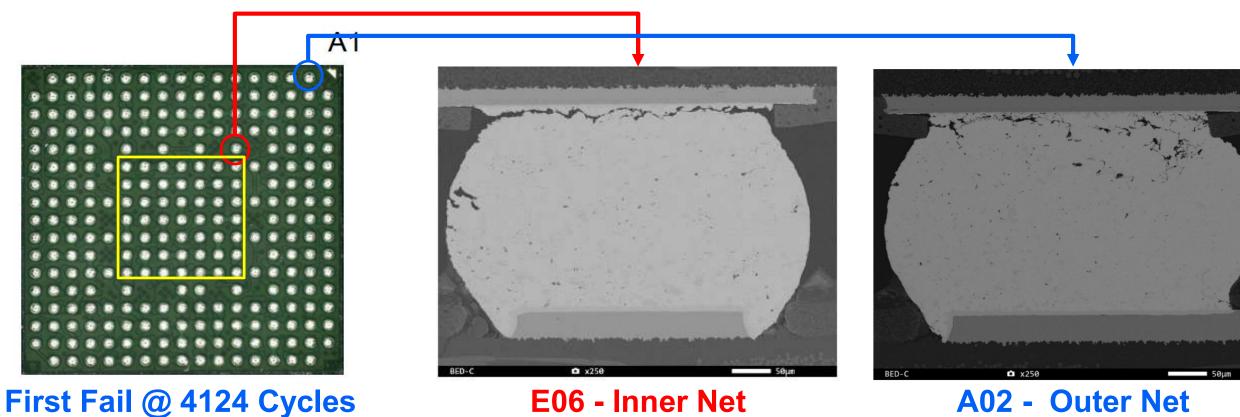

| Net Type  | First Fail (Cycles) | ETA (Cycles) |

|-----------|---------------------|--------------|

| Inner Net | 4124 cycles         | 5336 cycles  |

| Outer Net | 5055 cycles         | 6704 cycles  |

| Combined  | 4124 cycles         | 5338 cycles  |

Exceeding internal BLR requirements for AEC G1

#### **BLR BGA CROSS SECTIONS**

- First BGA failure occurred near die edge and near ball depopulation.

- Empirical data matches simulation.

**Partial Bulk Fracture**

**Complete Bulk Fracture**

#### **SUMMARY**

#### **Intra-die Wire Layout Design**

- Co-design between die design and assembly reduces manufacturing defects.

- IR drop simulation helps justify the implementation of high number of intra-die wires.

#### **Intra-die Wire Process and Challenges**

- Stand-off stitch bond (SSB) for intra-die wire requires two separate tail formation process, which increases the opportunity for error by a factor of 2.

- Detailed DOE's for parameter screening and optimization for bump smoothing, SSB bonding and low wire looping are required.

#### Package Reliability

- Package BOM exceeds AEC Grade 1 and Q006 requirements, passing 3X readpoints.

- Bump shear strength and SSB stitch pull strength observed minimal degradation at 3X package stress readpoints.

#### **Board Level Reliability**

- BLR simulation predicts the solder ball most susceptible to cyclic fatigue to be near the die edge and near the depopulated BGA area. Die:package ratio is 15%.

- Empirical study confirms simulation.

**PUBLIC**

#### **ACKNOWLEDGEMENT**

#### **Intra-die Wire Design**

Kuo-hsuan Meng

Mohamed Moosa

Scott Ruth

Melanie Etherton

Burt Carpenter

# BLR Simulation Package Electrical Model IR Drop Simulation

Sandeep Shantaram Frank Paglia Rohan Gupta

#### **Assembly Engineering**

Ghanesh Periasamy

Boh Kid Wong

Mei Jiun Tan

JH Wang

ZB Song

#### **Product / Test Engineering**

KL Tey

Vincent Tan

TL Mah

Amirthavel Kandasamy

Mai Tran

Mark Wagner

Kevin Kirkendoll

#### **Board Level Reliability**

Andrew Mawer

John Greider

Taylor Liu

## Package Analyses Failure Analyses

Thammarat T. and team Phyllis Vasquez Alvin Youngblood Roy Arldt

PUBLIC

## SECURE CONNECTIONS FOR A SMARTER WORLD