# Advanced Thermal Interface Materials: Assembly and Integration for System in Package

# **Power Dissipation**

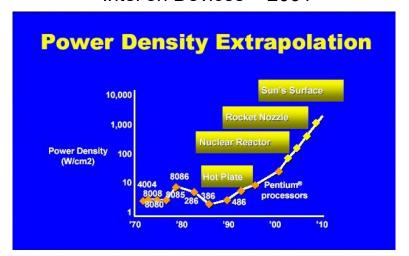

Power dissipation is perhaps the greatest challenge facing modern electron devices.

Intel on Devices ~ 2001

Intel on Packaging ~ 2001

Power dissipation, or self-heating, has limited the performance of integrated circuits for nearly two decades<sup>1</sup>.

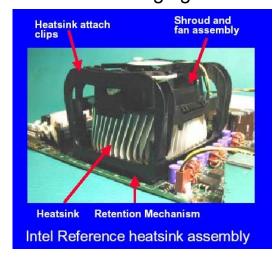

We often solve this via **packaging**, since self-heating is deeply rooted in charge transport in imperfect semiconductors at normal temperatures<sup>2</sup>.

- 1. S. Salahuddin, et al. The era of hyper-scaling in electronics. Nature Electronics 2018.

- 2. S. Data. Quantum Transport: Atom to Transistor. Cambridge University Press 2005.

### The thermal requirements on packaging are becoming more demanding.

#### Material Requirements<sup>3</sup>

|                                             | 1                                                                                               |                                                                                                                                        |                                                                                                                                     |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                             | Power Electronics/ Electrification Packaging Material Requirements                              |                                                                                                                                        |                                                                                                                                     |  |  |

| Attributes                                  | Current                                                                                         | 5 years                                                                                                                                | 10-15 years  Laminate & LF based (QFN, LGA, BGA, SiP ) Contact-less package (example: EM energy transfer) Flip chip/ (HD) FOWLP/PLP |  |  |

| Packaging platforms                         | Laminate & LF based (QFN,<br>LGA, BGA, SiP)<br>Power QFN, specialized<br>package (TO)           | Laminate & LF based (QFN,<br>LGA, BGA, SiP)<br>Flip chip/ (HD) FOWLP                                                                   |                                                                                                                                     |  |  |

| Pkg Dimensions                              | 2x2 to 7x7mm                                                                                    | 1x1 to 2x2 mm                                                                                                                          | Chip Scale                                                                                                                          |  |  |

| Device Material                             | Si                                                                                              | GaN, SiC                                                                                                                               | GaN, SiC                                                                                                                            |  |  |

| Max Junction Temperature                    | 175C                                                                                            | 200C                                                                                                                                   | 200C and beyond                                                                                                                     |  |  |

| Max Voltage                                 | 1300V                                                                                           | >2000V                                                                                                                                 | TBD                                                                                                                                 |  |  |

| Interconnect/via<br>material/surface finish | WB- Au wire,Cu wire,<br>Multiple Cu vias, Cu Pillar,<br>OSP, ENIG, ENEPIG,<br>Electrolytic NiAu | WB-Cu wire, OSP, SOP,<br>ENIG, ENEPIG, Electrolytic<br>NiAu, Cu Pillar interconnect,<br>Thicker Cu-via/ Larger<br>surface area (clips) | Cu Pillar, OSP, SOP, ENIG, ENEPIG,<br>Electrolytic NiAu<br>New Materials (graphite, etc)                                            |  |  |

| Die attach materials                        | Epoxy, Solder (Leadfree &<br>Leaded)<br>Sintering Adhesive (Pb-free)                            | Sintering Adhesive (Pb-free)<br>Diamond and Graphite<br>loaded materials                                                               | TLPS (Transient Liquid Phase Sintering) New Materials (graphite, etc.)                                                              |  |  |

Diamond and Graphite loaded materials

#### Thermal Requirements<sup>3</sup>

**Table 3:** Thermal Management Requirements. (Green: Solution available for manufacturing. Yellow: Additional development work needed. Red: Significant development effort needed for HVM. White: Information only)

| Thermal Management |                                    |                                 |            |  |  |  |  |

|--------------------|------------------------------------|---------------------------------|------------|--|--|--|--|

|                    | >2023                              | >2028                           | 2033 and + |  |  |  |  |

| Ingredients        |                                    |                                 |            |  |  |  |  |

| Thermal            | Thermal interface materials with   |                                 |            |  |  |  |  |

| Interface          | low thermal resistance and high    |                                 |            |  |  |  |  |

| Materials          | resilience to package and board    |                                 |            |  |  |  |  |

| (TIMs)             | level assembly techniques (50% or  |                                 |            |  |  |  |  |

|                    | greater reduction especially in    |                                 |            |  |  |  |  |

|                    | effective thermal resistance under |                                 |            |  |  |  |  |

|                    | reliability conditions)            |                                 |            |  |  |  |  |

| Heat               | High conductivity (2x or greater   | High conductivity spreaders for |            |  |  |  |  |

| Spreaders          | than copper), low-cost materials   | integration within a 3D stack   |            |  |  |  |  |

|                    | for interfacing which are capable  | which are process compatible.   |            |  |  |  |  |

|                    | of being cost effectively          | Thermal conductivities >= 3000  |            |  |  |  |  |

|                    | manufactured into integrated       | W/m/K with a thickness of       |            |  |  |  |  |

|                    | heat spreaders on the package      | 50mm to 200mm                   |            |  |  |  |  |

Thermal conductivities >= 3000 W/m/K with a thickness of 50mm to 200mm

3. National Institute of Standards and Technologies. Microelectronic and Advanced Packaging Technologies Roadmap. Interim Edition 2023.

### **Die Attachment**

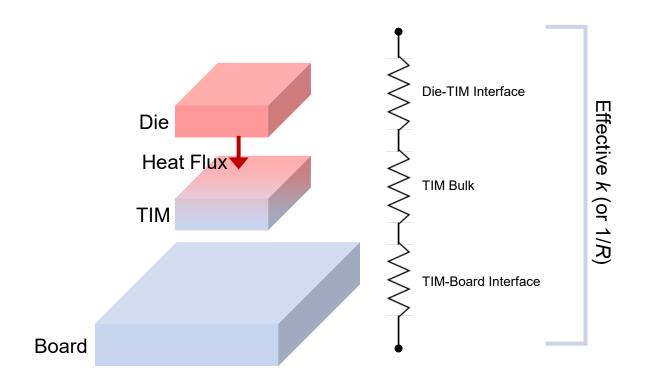

The thermal conductivity (k) of the thermal interface material (TIM) is directly related to the device's temperature rise ( $\Delta T$ ) at a given operating power or heat flux (q).

#### Fourier's law

$\Delta T = qL/k$  where L is the ~ 100 mm thickness of the TIM

As devices push heat fluxes of  $\sim 10^5 \text{ W/m}^2$ , thermal conductivities of  $\sim 10^3 \text{ W/mK}$  are required for acceptable temperature rises<sup>3</sup>.

3. National Institute of Standards and Technologies. Microelectronic and Advanced Packaging Technologies Roadmap. Interim Edition 2023.

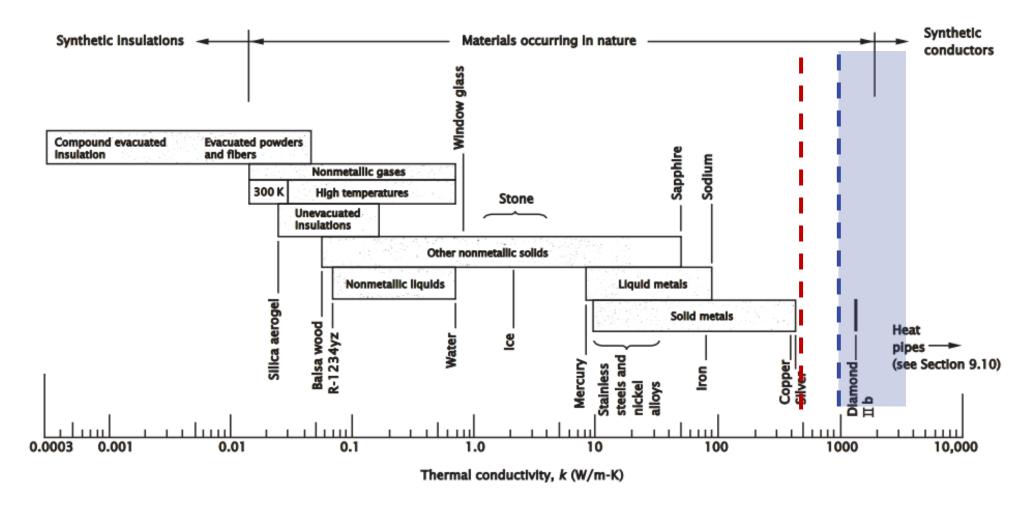

# **Moving Beyond Metals**

Metals are limited to  $k \sim 10^2$  W/mK and few materials can tap into the  $10^3$  W/mK range<sup>4</sup>.

4. G. Chen. Nanoscale Energy Transport and Conversion: A Parallel Treatment of Electrons, Molecules, Phonons, and Photons. Oxford University Press 2005.

# **Why Carbon Materials?**

Why are carbon materials (graphene, graphite, carbon nanotubes, diamond) seemingly alone on many roadmaps for advanced passive/conductive thermal packaging?

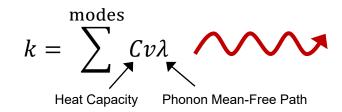

$$\omega = \sqrt{\frac{k}{m}}$$

From mechanics, the vibrational frequency ( $\omega$ ) of a harmonic oscillator is related to the atomic mass and stiffness of the interatomic potential.

Carbon has light atoms and stiff bonds

From kinetic theory, the thermal conductivity is related to the group velocity  $(v \propto \omega)$  of the phonons.

Carbon has high thermal conductivity

From nature, electrical insulating (diamond) and conducting (graphite) forms exist.

Carbon has electrically insulating and conducting forms

Many synthetic conductors, like heat pipes or microfluidics, may not be compatible with highly integrated systems. For example, back-end-of-the-line compatibility for monolithic 3D integration.

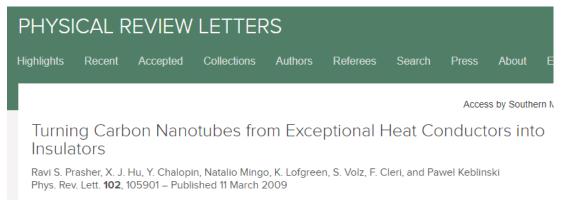

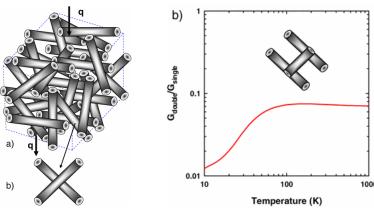

### The atomic-scale interfaces within the TIM are major challenges.

Under some conditions, the interface of graphite is 3× more thermally resistive than air!

- 5. S. Prasher, et al. Turning Carbon Nanotubes from Exceptional Heat Conductors into Insulators. Physical Review Letters 2009.

- 6. S. Vaziri, et al. Ultrahigh thermal isolation across heterogeneously layered two-dimensional materials. Science Advances 2019.

### Heterogeneous integration of these TIMs is limited by many areas.

#### **Fabrication**

How do we build these carbon-based materials?

- controlling interface chemistry

- controlling material quality

- controlling material uniformity

#### Metrology

How do we characterize these materials?

- mapping nanoscale thermal profiles

- measuring thermal boundary resistance

- relating thermal, structural, and chemical properties

Integration

How do we integrate these materials?

- preventing damage

- avoiding thermal expansion mismatch

Table 5.1: Illustration of the current State of the Art and future needs for different metrology requirements.

| Metrology<br>Technology                                                | Current                                                                                                                        |                                                                                                                           | 5 years                                                                                                                                                                                 | 10 years                                                | 15 years                                  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|

| Atomic-level<br>characterization<br>of new<br>materials and<br>devices | Aberration<br>corrected<br>STEM  Automated FIB<br>sample<br>preparation<br>with consistent<br>lamella<br>thickness  APT<br>SPM | Advanced electron diffraction methods  Advanced energy dispersive X- ray spectroscopy  Backscattered electron diffraction | Aberration corrected SEM  Al/ ML analysis of characterization data i.e. strain analysis  ML-based analysis of crystal phase and orientation in nanostructures  Reduced time to analysis | Continued<br>improvement                                | Continued<br>improvement<br>via invention |

|                                                                        |                                                                                                                                |                                                                                                                           | Increase in wavelength range                                                                                                                                                            | Increased X-ray<br>source Intensity<br>for In-fab X-ray |                                           |

AI/ ML analysis

ML-based analysis

3. National Institute of Standards and Technologies. Microelectronic and Advanced Packaging Technologies Roadmap. Interim Edition 2023.

## **Metrology Limitations**

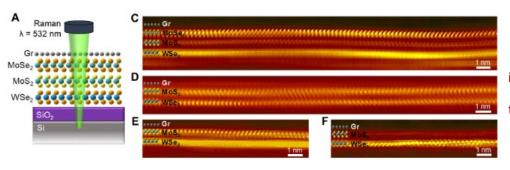

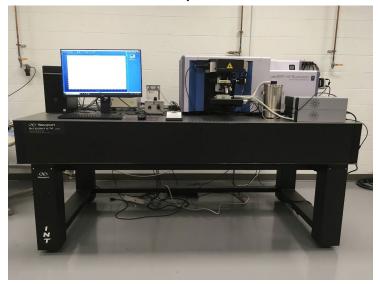

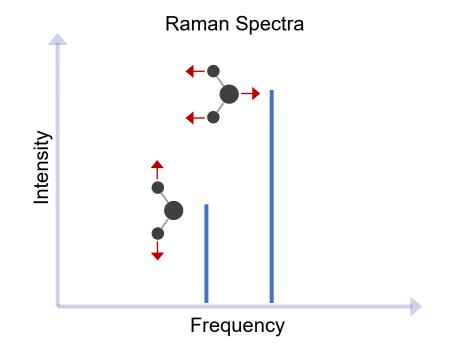

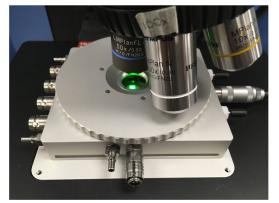

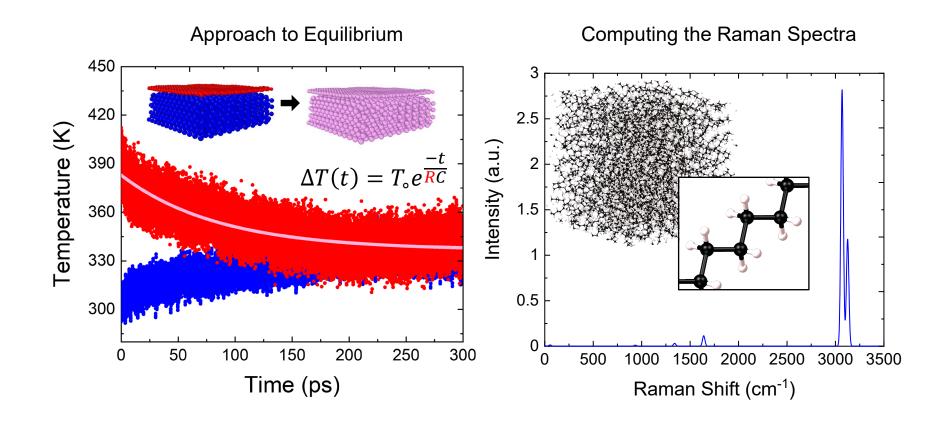

Raman spectroscopy is a powerful metrology that probes the vibrational modes of materials.

#### Raman Spectrometer

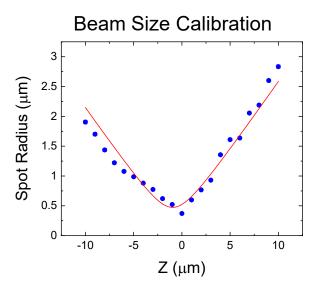

A ~ 600 nm optical laser beam that can be moved (or rastered) with nanoscale resolution and can see through transparent layers (like GaN, SiC, or oxides).

Applied Research

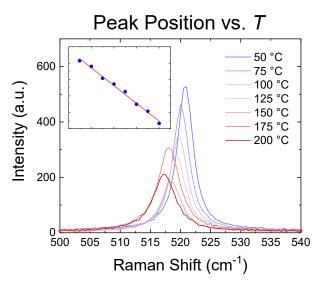

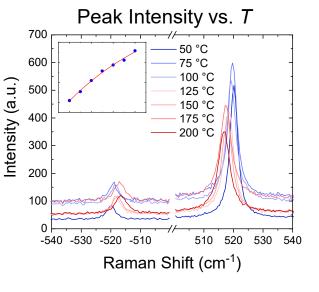

The peak intensity, width, and frequency can tell us:

- temperature

- composition

- defects

- strain

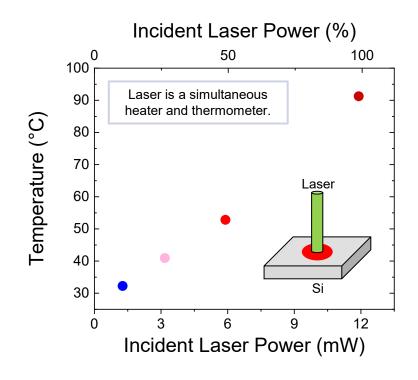

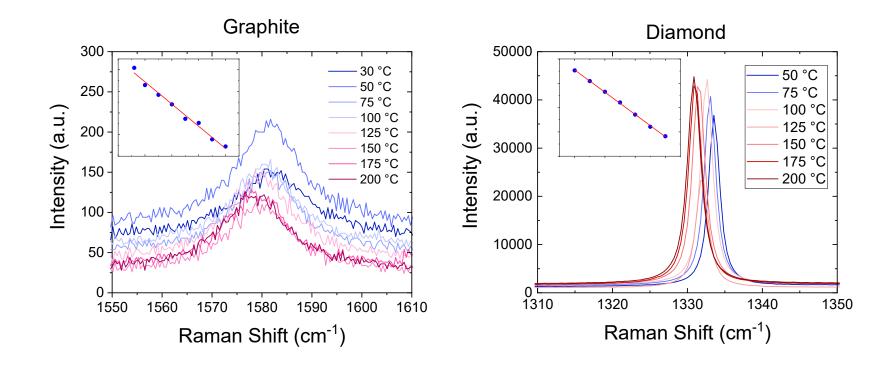

Raman thermometry is the method of using the Raman spectrum to characterize temperature (T).

Thermal Stage

# Raman-Based Thermal Conductivity Measurements

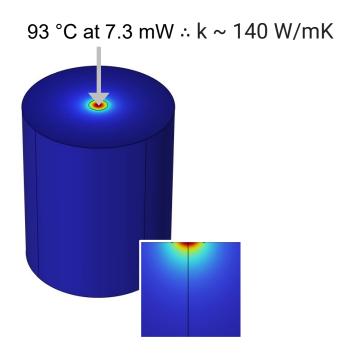

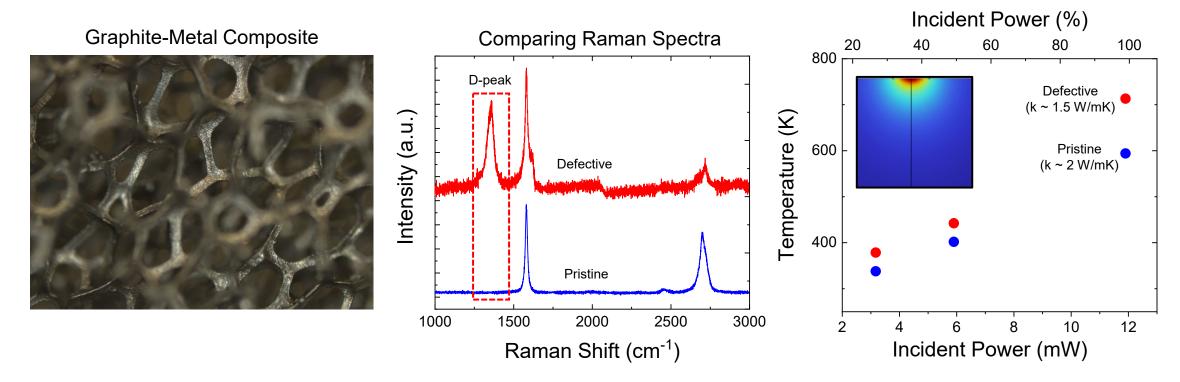

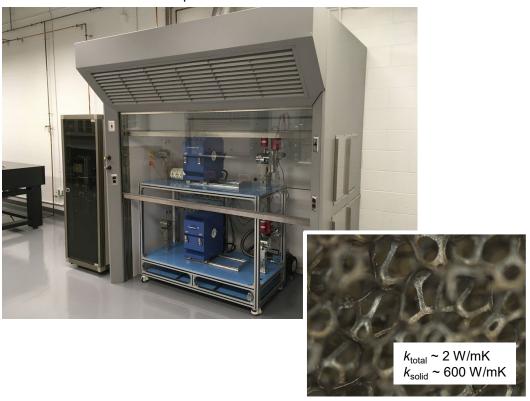

On materials with complex or delicate morphologies, Raman thermometry can be expanded to an optical thermal conductivity extraction.

The temperature of graphite and diamond can be calibrated, providing a framework for investigating carbon-based thermal packaging.

# Thermal Conductivity vs. Structure and Chemistry

While temperature is characterized with peak shifts, peak broadening (or new peaks) can characterize the structure and chemistry.

The Raman laser is now a simultaneous heater, thermometer, and characterizer of structural/chemical details!

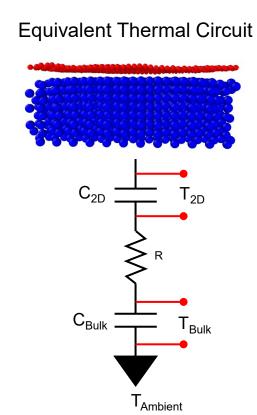

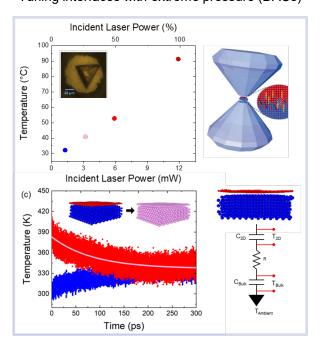

Raman thermometry can be coupled with molecular dynamics simulations to investigate the structure-(thermal) property relationships of interfaces.

There are a variety of promising avenues for carbon-based thermal packaging.

# Graphene/Graphite Grown Directly on Metals Templated Growth?

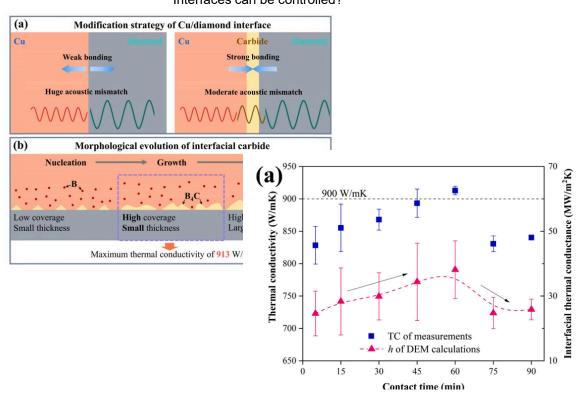

# Successful Engineering of Carbon-Metal Interfaces Interfaces can be controlled?

- 7. M. Pettes, et al., "Thermal Transport in Three-Dimensional Foam Architectures of Few-Layer Graphene and Ultrathin Graphite." Nano Letters 2012.

- 8. Y. Zhang, et al. Manipulating in-situ discrete carbide interlayer to achieve high thermal conductivity in Cu-B/diamond composites. Materials Today Communications 2022.

# Takeaways and Future Work Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

- Power dissipation will continue to be a major limiter of electron devices, and likely require packaging solutions.

- Materials with thermal conductivities of ~ 103 W/mK are needed, and carbon-based materials are the best options

- Integration and assembly of carbon-based packaging materials are limited by **interfaces** and require new metrology and fabrication approaches.

Example Work from Our Lab

Tuning interfaces with extreme pressure (DACs)

# Kevin Brenner Southern Methodist University Department of Electrical and Computer Engineering

brenner@smu.edu | 214-768-4755 | people.smu.edu/brenner

Dr. Jyothi Chintalapalli

Jesus Alejandro Avendano Bolivar

Chaman Islam