# Toward Thinner and Higher Heat Dissipation Advanced Chip Embedded Power Supply Module Packaging

Katsuhiro Takao, Atsushi Kuroha, Michihito Kawada, Ichiro Kono, Takashi Suzuki and Yoshiaki Aizawa AOI ELECTRONCS CO., LTD.

- Background

- Introduction of Our Coreless Chip Embedded Technology

- Trial production and evaluations for a Prototype

- Manufacturing flow

- Process flow

- Package structure

- Prototyped package

- Package warpage

- Summary

- Background

- Introduction of Our Coreless Chip Embedded Technology

- Trial production and evaluations for a Prototype

- Manufacturing flow

- Process flow

- Package structure

- Prototyped package

- Package warpage

- Summary

## **Background**

#### Applications : Power Supply System

Source: NTT Corporation

Source: TOYOTA corporation

- ✓ Data centers and various power supply equipment shift from 12V to 48V systems.

- ✓ As power supply output current increasing, wiring resistance is a big issue about power distribution loss.

- ✓ Placing the power supply near the processor (CPU/GPU) will be an important for power integrity.

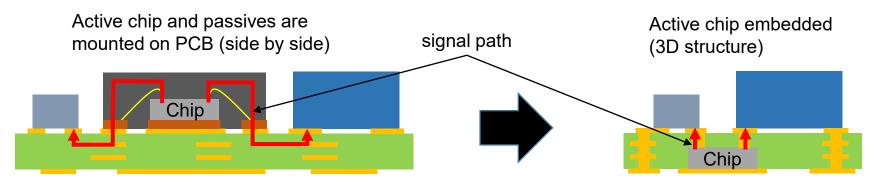

- Chip-embedded packages (PoP/CoP/3D-SiP) can shrink size and increase current density.

According to Texas Instruments 's white paper, they have brought an average module size reduction of 25 percent annually.

Source : U. Chaudhry et al, SiP Power Modules White Paper "Powerful solutions come in small packages", Texas Instruments, page2

## Background

#### Packaging Technologies

Smaller package Lower resistance and inductance properties

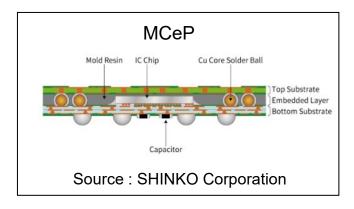

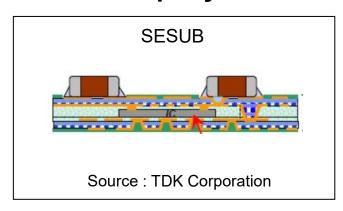

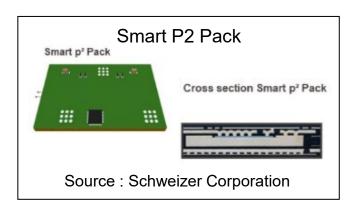

#### Chip Embedded package trends of each company

Recently, several chip-embedded packages have been proposed. We want to propose a new thinner and higher heat dissipation coreless package structure.

## Background

Concerns about reducing thermal resistance with PCB prepreg substrates

#### ✓ Cu foil + core material

Difficult to form large vias due to glass cloth as disturbance.

Also difficult to fill with Cu in the via due to thick plating requirement.

Thinning down is limited due to thick core material.

## Core Cu Resin

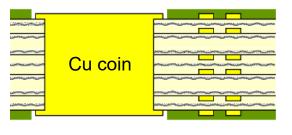

## √ Cu inlay / coin

Cu coins are large in size and thick, so difficult to make smaller and thinner.

And, there are also layout design restrictions. Built-in process has difficulty affecting productivity and cost.

Source : ELNA PRINTED CIRCUITS corporation

Source : FINECS corporation

For power applications, PCBs based structure size/thickness, heat dissipation properties, and cost are still non-negligible issues and consequently necessitate the development of further concepts.

- Background

- Introduction of Our Coreless Chip Embedded Technology

- Trial production and evaluations for a Prototype

- Manufacturing flow

- Process flow

- Package structure

- Prototyped package

- Package warpage

- Summary

## Introduction of Our Coreless Chip Embedded Technology

AOI's new approach of *Ultra thinner, Higher heat dissipation* chip embedded technology in analog and power solutions.

## **Features of this concept**

- Unique Coreless structure with all-Cu plating embedding method, using power customized fan-out processes

- Panel form of 300 mm square with cost benefit

- Smaller and Ultra thinner module package with coreless structure

- Excellent thermal property with large electrode pad and large via filling

- High reliability and short TAT with one stop solution (from panel substrates to package assembly in-house)

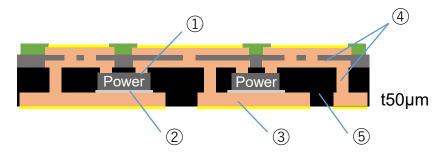

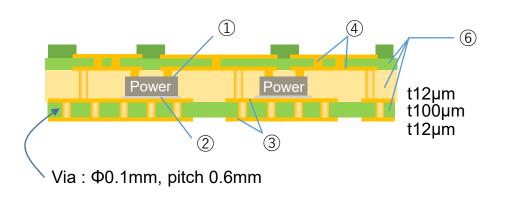

## Thermal Resistance Simulation with Our Concept Package

#### Simulation conditions and structures

#### Our concept package

#### Conventional Prepreg package (assumption)

#### **Analysis conditions**

| Analysis software         | ANSYS                                   |  |  |

|---------------------------|-----------------------------------------|--|--|

| Analysis type             | Steady heat transfer                    |  |  |

| Heat transfer coefficient | 10W/(m²°C) assuming natural air cooling |  |  |

| Chip Power                | Total 1.0W<br>0.5W/power chip           |  |  |

#### Material properties

| Parts          | Thermal conductivity [W/(m.°C)] |  |  |

|----------------|---------------------------------|--|--|

| ①Chip          | 124                             |  |  |

| ②Ag sinter     | 100                             |  |  |

| ③Electrode PAD | 360                             |  |  |

| ④RDL, VIA      | 360                             |  |  |

| ⑤EMC           | 1.0                             |  |  |

| 6Prepreg       | 0.7                             |  |  |

| ⑦Solder resist | 1.0                             |  |  |

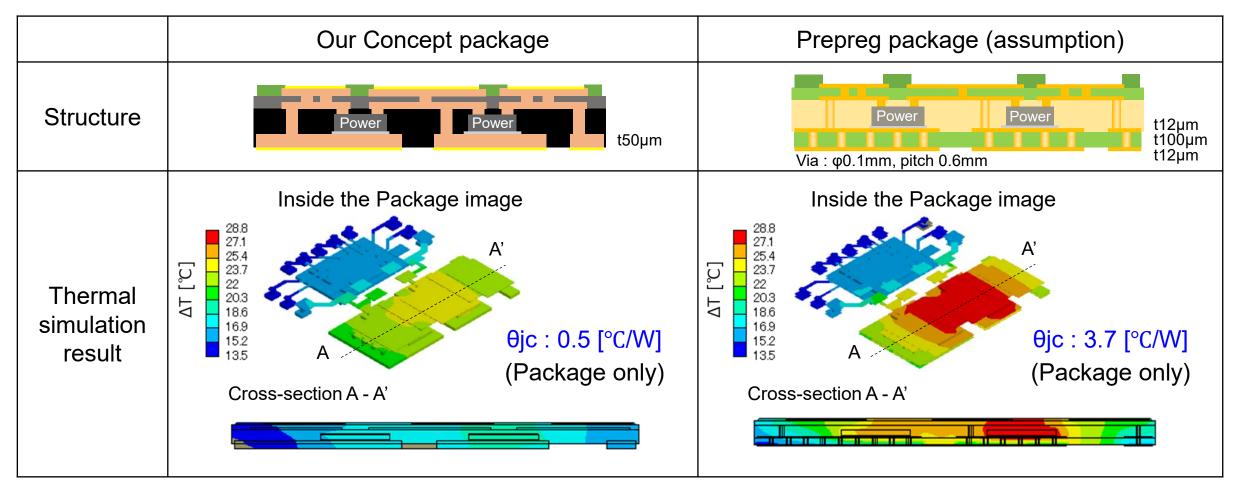

## Thermal Resistance Simulation with Our Concept Package

#### Simulation result

The thermal resistance of our concept package is very low, and it has the advantage of quickly dissipating heat to the substrate side.

- Background

- Introduction of Our Coreless Chip Embedded Technology

- Trial production and evaluations for a Prototype

- Manufacturing flow

- Process flow

- Package structure

- Prototyped package

- Package warpage

- Summary

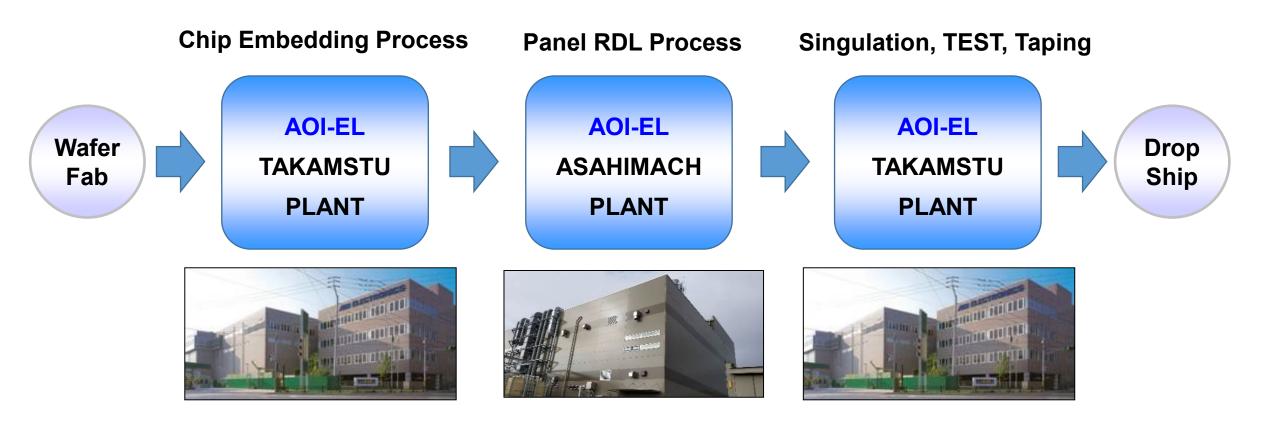

■ Panel level package manufacturing flow

We can perform one-stop production in-house, from panel substrates to chip embedding process, panel RDL process and package assembly.

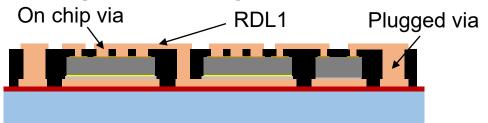

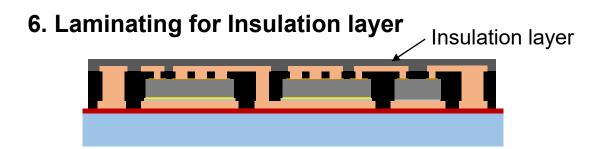

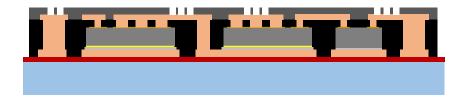

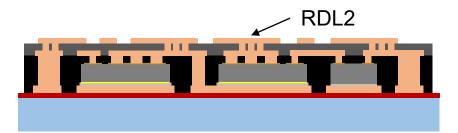

- Process flow (1)

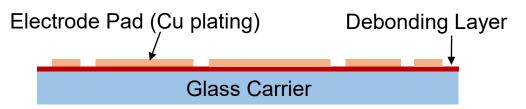

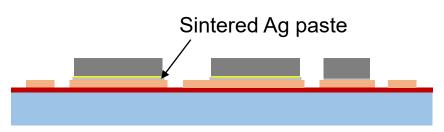

- 1. Electrode Pads Formation on Glass Carrier

5. Cu plating for Via-filling and RDL1

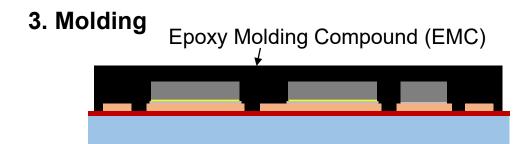

- Process flow (2)

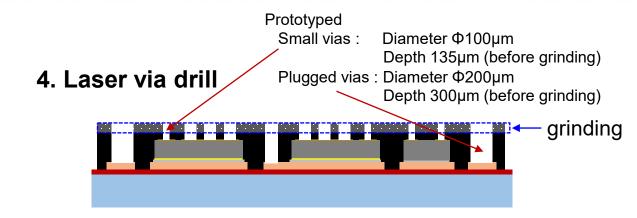

- 7. Laser via drill

8. Cu plating for Via-filling and RDL2

9. Solder resist formation

10. Glass Carrier Debonding / Terminal plating / Singulation

Our usual inspection or test

- Pattern inspection for each process

- Open/short test for checking internal connection

- Optional function test

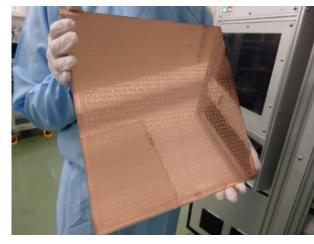

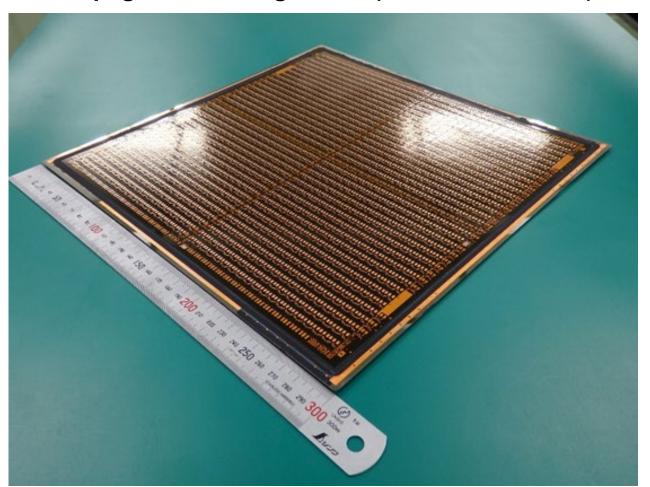

■ 300 mm square Panel-level photo

**Warpage Before singulation (with Glass Carrier)**

Panel warpage : 2mm Maximum

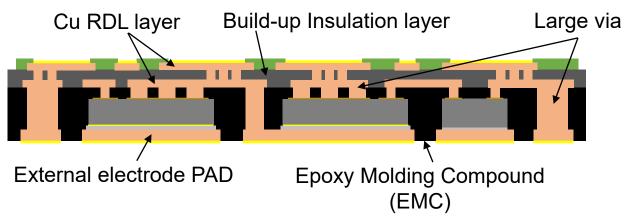

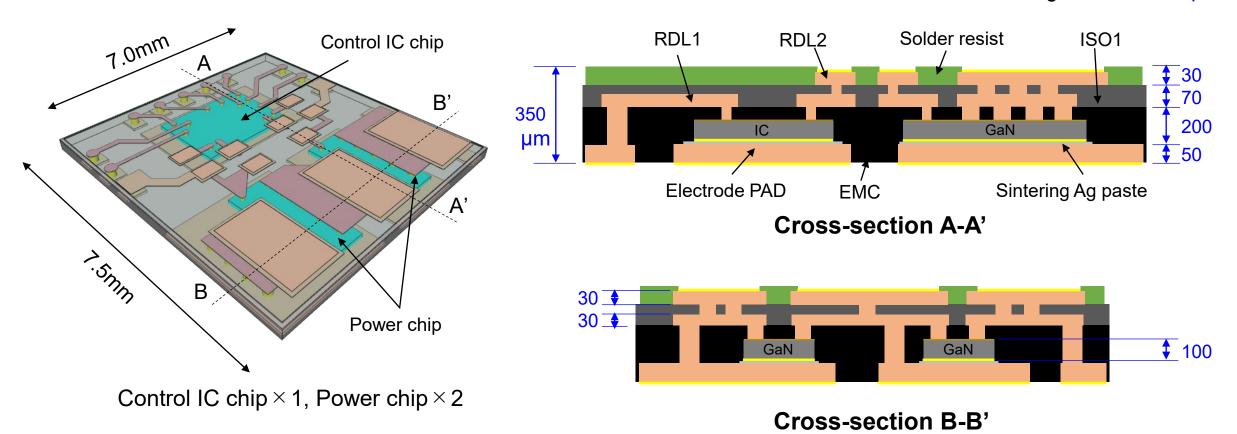

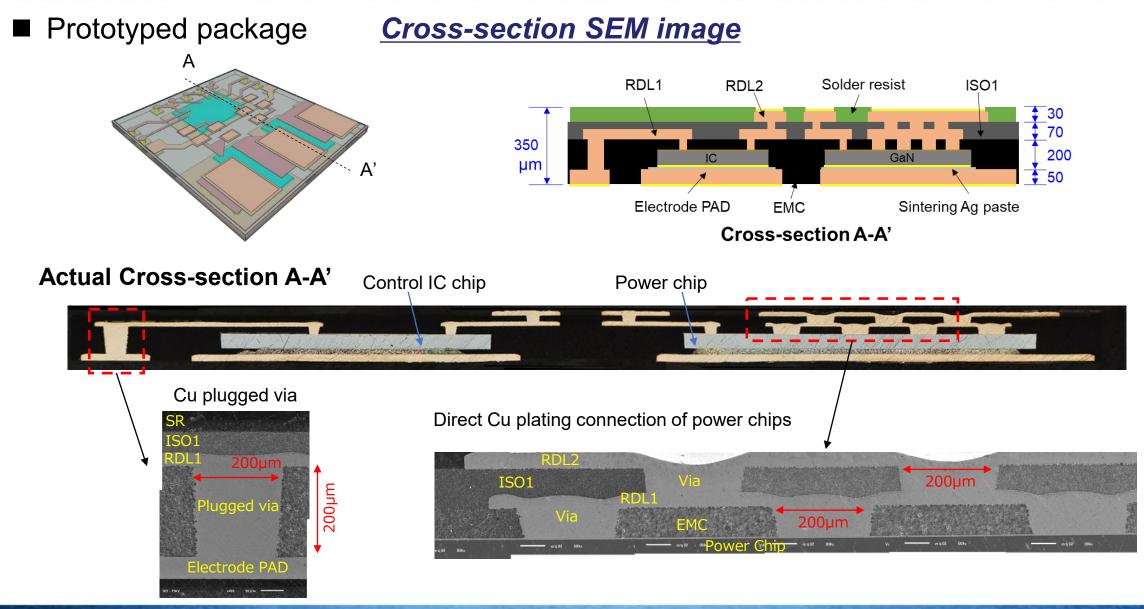

Prototype package structure

Design value /unit : µm

- · Ultra-thin & high heat dissipation module with DC-DC half-bridge structure.

- Motif of GaN HEMT for power and high-speed switching.

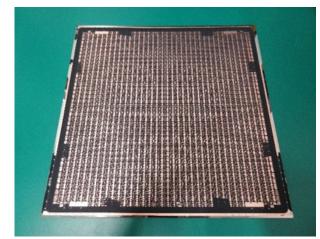

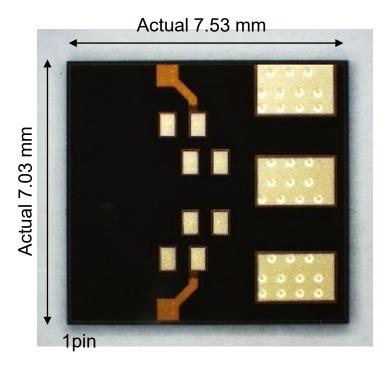

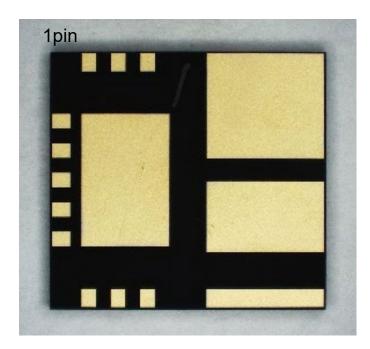

Prototyped package

Top side

Bottom side (Board mounting side)

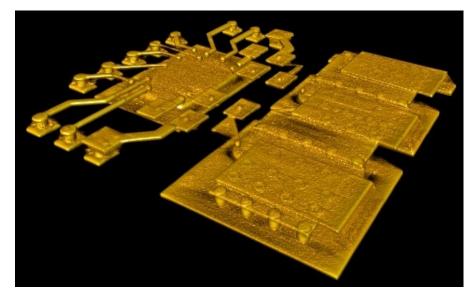

X-ray CT 3D image (Internal structure)

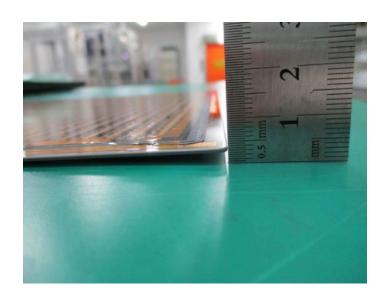

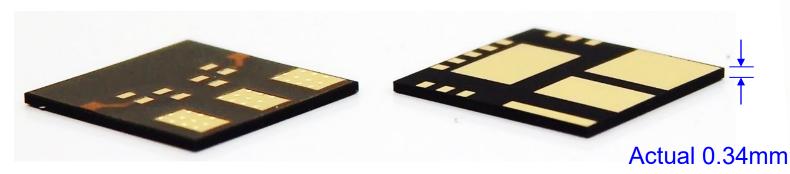

Prototyped package

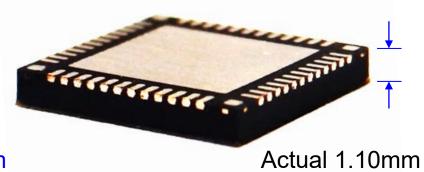

Package thickness comparison

#### New Coreless chip embedded module package

#### Conventional Power QFN

Top side

Bottom side

Package size: 7.0×7.5mm

Package size: 8.0×8.0mm

Our proposed new Coreless chip embedded package thickness is actual 0.34mm. It is very thin compared to conventional power QFN.

Very thin SoC-like analog and power module package such as heterogeneous chip bonding can also be realized.

Prototyped package **Cross-section SEM image** B' RDL1 RDL2 **ISO1** Solder resist 30 🛊 **‡** 100 В **EMC** Sintering Ag paste Electrode PAD **Cross-section B-B' Actual Cross-section B-B'** Power chip Power chip **Good Necking** Chip attached paste Direct Cu plating connection of power chips Sintering Ag p 200um Power Chip **Electrode PAD**  $\times 1,000$  $\times 50,000$

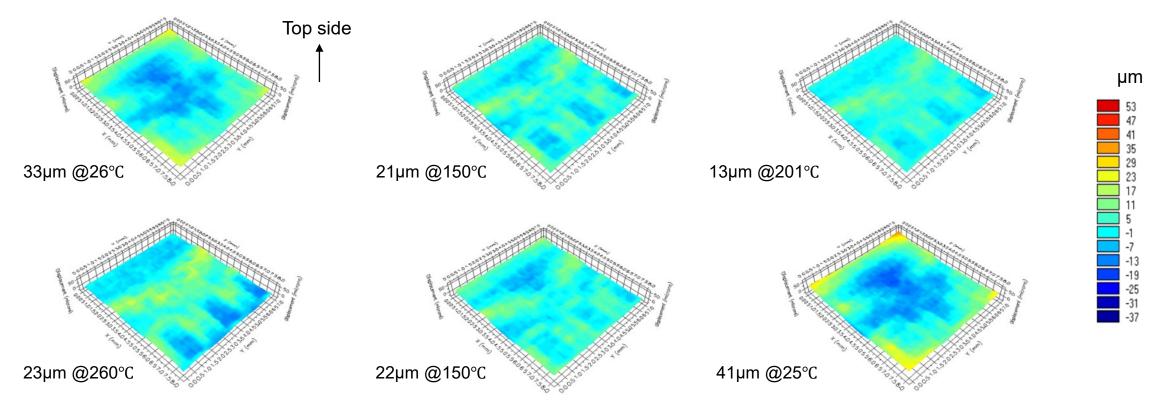

Package warpage

Warpage Behavior in the Reflow Temperature Range using shadow moiré method (3D Plot)

At room temperature, warpage was maximized (less than 50µm) with smile shape. At high reflow temperature, warpage became small, tended to be flat.

## ■ Reliability test

| Test<br>Items    | Test Condition                                                             | Duration | Judgment                                   | Status  |

|------------------|----------------------------------------------------------------------------|----------|--------------------------------------------|---------|

| Precondition     | 85°C, 60%RH, 168hr<br>⇒ >260°C, 30sec. 3X<br>(JEDEC J-STD-020D MSL Level2) | -        | SAT<br>Open/shot test                      | Ongoing |

| HTHH             | Precondition<br>⇒ 85°C 85%RH                                               | 1,000hr  | SAT SEM Cross-section Open/shot test       | Ongoing |

| Unbiased<br>HAST | Precondition<br>⇒ 121°C, 100%RH, 2atm                                      | 100hr    | SAT<br>SEM Cross-section<br>Open/shot test | Ongoing |

| HTS              | Precondition ⇒ 150°C                                                       | 1,000hr  | SAT<br>SEM Cross-section<br>Open/shot test | Ongoing |

| TC               | Precondition ⇒ -65°C~150°C                                                 | 500cycle | SAT<br>SEM Cross-section<br>Open/shot test | Ongoing |

There is no initial failure at Unbiased HAST 48hr, TC 100cycle (SAT, Open/shot test).

- Background

- Introduction of Our Coreless Chip Embedded Technology

- Trial production and evaluations for a Prototype

- Manufacturing flow

- Process flow

- Package structure

- Prototyped package

- Package warpage

- Summary

## **Summary**

- ✓ We have demonstrated a very thin thickness of 350µm and higher heat dissipation new advanced chip-embedded power module package with 300mm square panel-level process.

- ✓ This proposed new package is very suitable for high power delivery solutions, especially for complex power delivery structures such as multi-core processors, FPGAs and so on, with thinness and being placed in close proximity to each point of load.

- ✓ Very thin SoC-like analog and power module package such as heterogeneous chip bonding can also be realized.

## Thank you for your attention.

## Our presentation will also be in Poster Session. Please join and discuss!