# Chip to Wafer Hybrid Bonding Development for High Volume Manufacturing

## **AGENDA**

- Introduction

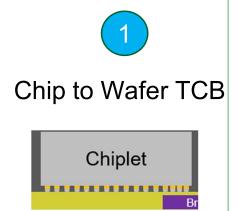

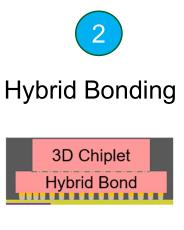

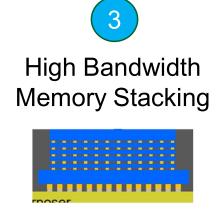

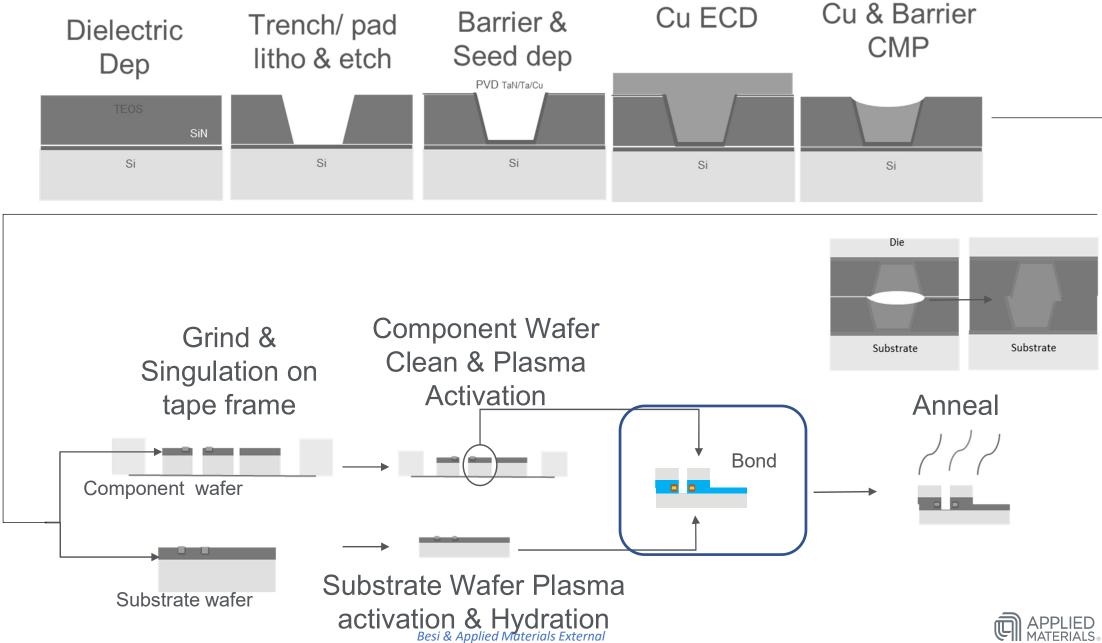

- Chip to Wafer Hybrid Bonding Process Flow

- Characterisation and Electrical Yield

- Die to Wafer Hybrid Bonding

- Conclusion

## Hybrid Die Bonding: Next Generation Bonding Technology

|                 | Wire Bond<br>(1975)  | Flip Chip<br>(1995)          | TCB Bonding<br>(2012)   | HD Fan Out<br>(2015) | Hybrid Bonding<br>(2018)  |

|-----------------|----------------------|------------------------------|-------------------------|----------------------|---------------------------|

| Architecture    | PCS                  | 000 _ 000<br>PG              | Heat compression force  | Custom Digital       | Cu Dielectric resolveriel |

| Contact Type    | Wire                 | Solder ball or copper pillar | Copper pillar           | RDL or copper pillar | Copper to copper          |

| Contact Density | 5-10/mm <sup>2</sup> | 25-400/mm²                   | 156-625/mm <sup>2</sup> | 500+/mm²             | 10K-1MM/mm²               |

| Substrate       | Organic/leadframe    | Organic/leadframe            | Organic /Silicon        | None                 | None                      |

| Accuracy        | 20-10µm              | 10-5μm                       | 5-1µm                   | 5-1µm                | 0.5-0.1μm                 |

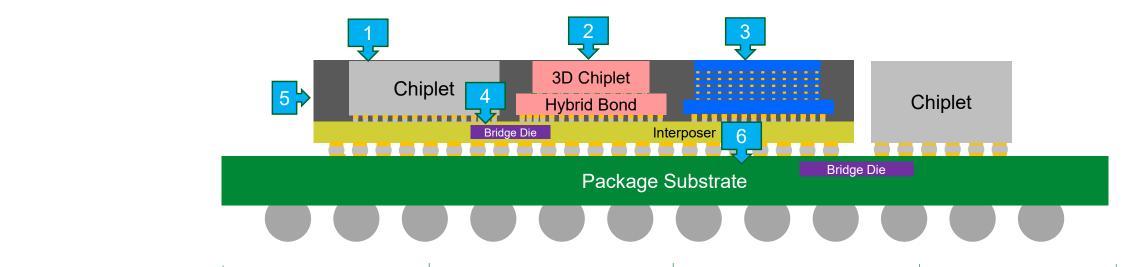

## New 3D Chiplet Structures Use Variety of Processes

## Besi – Industry leading portfolio

#### Die Attach

#### **Hybrid Bonding**

• 8800 CHAMEO ultra plus

#### **Thermo Compression**

- 8800 TC advanced (Substrate)

- 8800 TC NEXT (Chip to Wafer)

### <u>on</u>

**Embedded**

**Bridge Attach**

• 8800 FC CHAMEO Ultra

#### Flip-chip

- 8800 CHAMEO advanced / PLP

- 8800 FC Quantum adv / sigma

- 8800 FC Quantum hs

- 2100 FC hS

#### **Direct Lid Attach**

- DLA

- TGB 2.0

#### **Epoxy / Soft Solder**

- 2100 hS

- 2009 SSI

- 2100 hS i

- 2100 SSI

- 2100 sD advanced i 2100 DS

- 2100 hS ix

#### **Multi-Module Attach**

- 2200 evo

- 2200 evo plus

- 2200 evo hS

- 2200 evo advanced

- 2200 evo hf

### **Packaging & Plating**

#### Wafer & Panel Molding

#### **FML**

- Wafer molding

- Panel molding

### **Substrate Molding**

#### AMS-LM

- Substrate strip format

- Exposed die

### **Leadframe Molding**

#### AMS-i

- MEMS

- AMS-X

HD Leadframe

- Sensors

- Power Devices

#### **Singulation**

### FSL

Substrate strip singulation Sorting

#### **Trim and Form**

#### FCL-X/P

Leadframe trim & form Sorting

#### Plating

- Leadframe

- Solar

- Film & Foil

- Chemical Deflash

- Wettable Flank

## **Hybrid Bonding Basics**

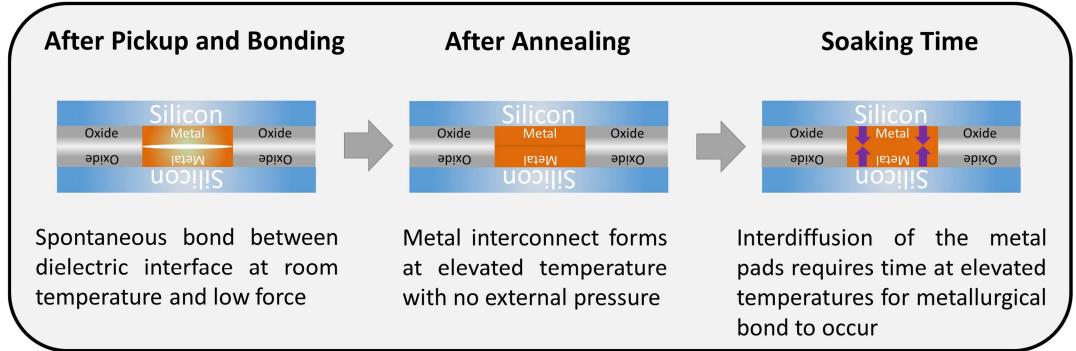

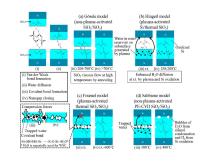

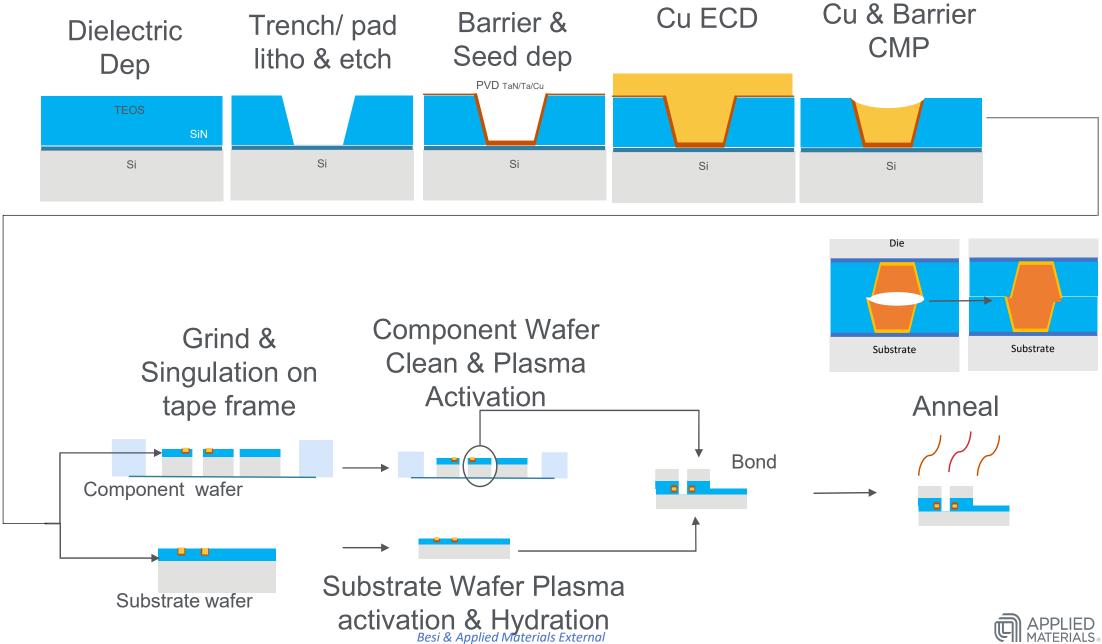

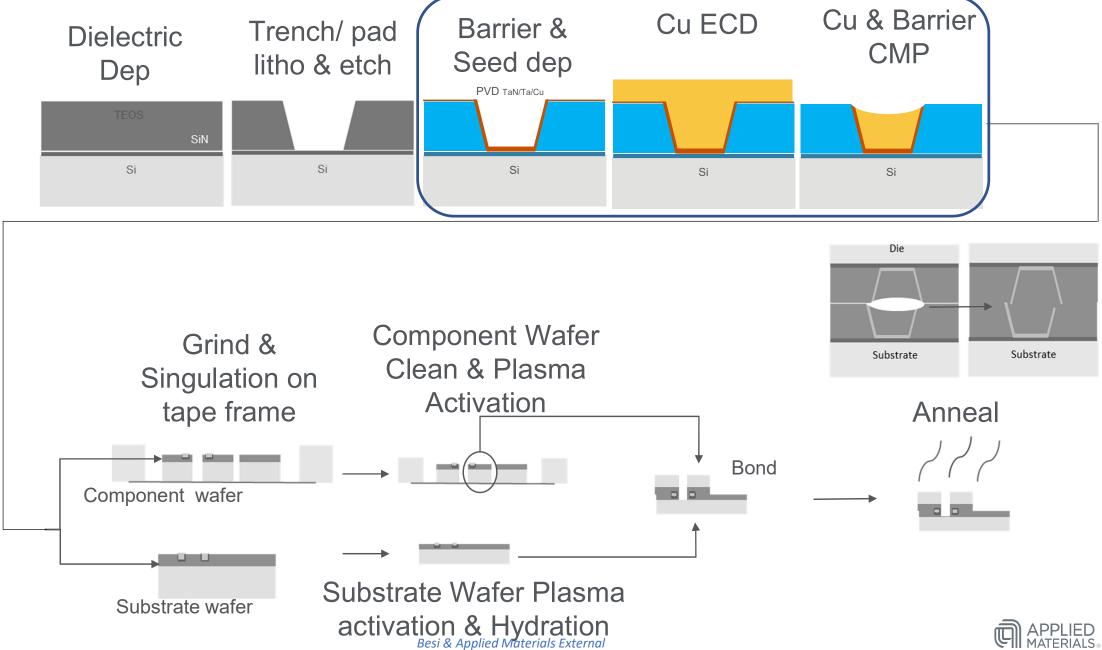

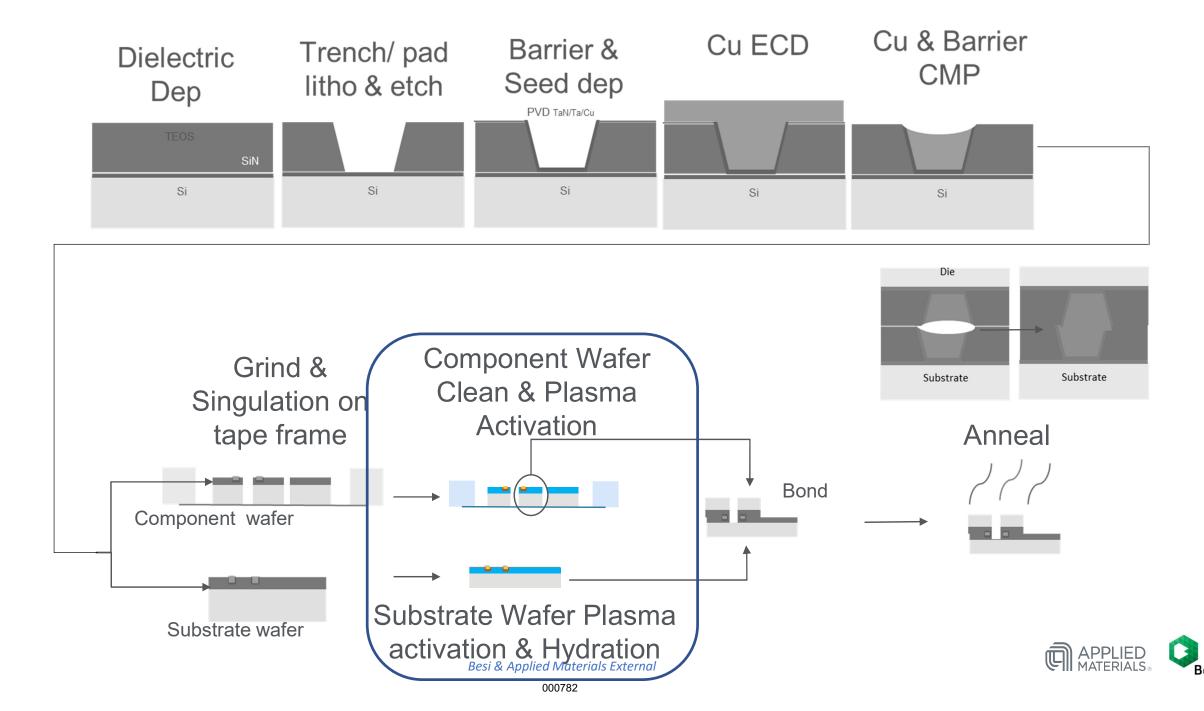

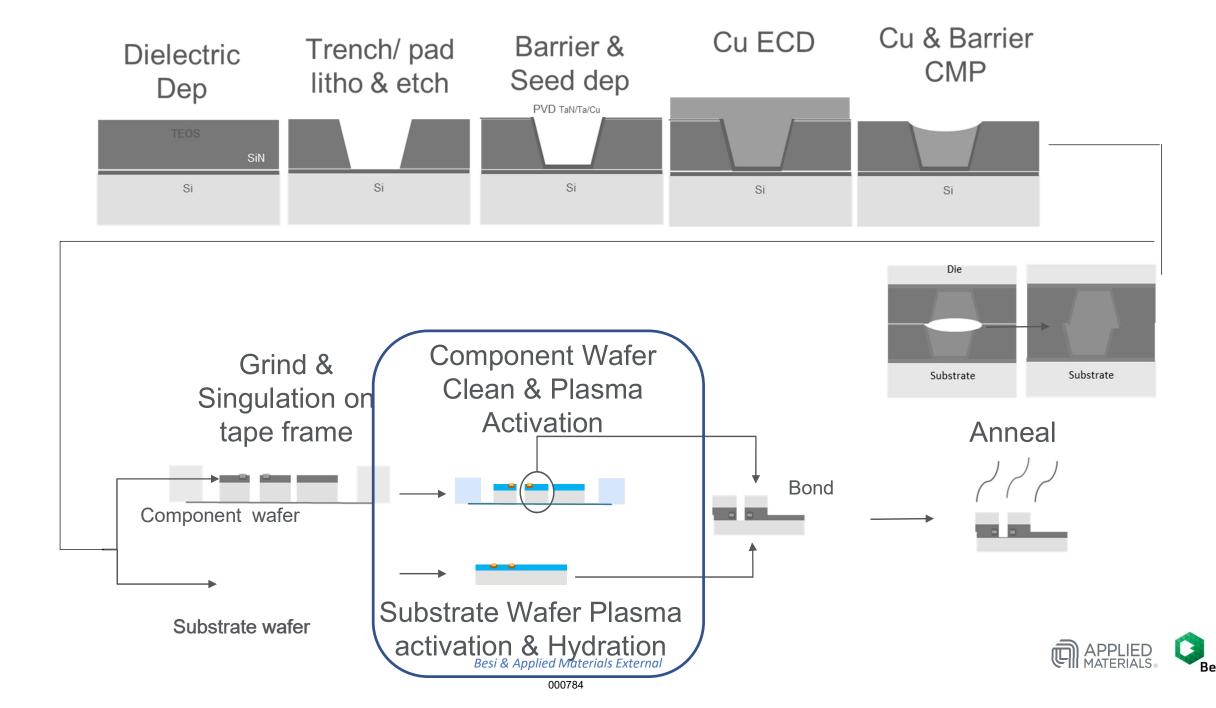

Procedural steps for conventional direct wafer bonding of hydrophilic silicon are:

- Wafer pre-processing pre-cleaning and removing of specific contamination (particles, organic and ionic contaminants) and/or plasma activation.

- Pre-bonding at <u>room temperature with low force (up to 15N)</u> primary adhesive effects are caused through van der Waals forces and hydrogen bonds. Subsequently, covalent bonds are created.

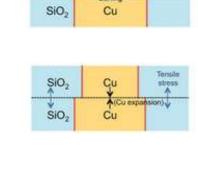

- Annealing at elevated temperature from 150°C up to 400°C causes further diffusion of dielectric, strengthening the bond. Copper pads are also expanded resulting in electrical connection.

## Hybrid Bonding – Many Challenges

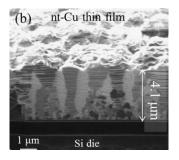

### **Copper quality** and fill

### Impact of oxide depostion

### **CMP** and **Dishing**

### **Dicing Cleanliness**

### Cleaning **Parameters**

### Plasma **Activation Parameters**

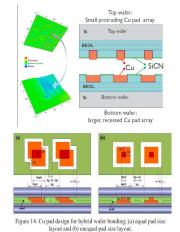

### **Optimized Bonding** Geometry

### **Bonding Process Industrial Solution**

### **Integrated Process** Flow, Low Particles, Inspection

### **Anneal**

Cu

SiO,

### **Electrical**

### Life Time

- Corrosion

- Electromigration

- Thermal Stability

## Applied Materials | Broadest Portfolio in Advanced Packaging

Al Pad / RDL Expose | Develop PVD UBM Etch PR Strip Bump **FanOut** Endura Charger 000000 00000 Nokota Raider Raider Execta 2 Al 00000 00000 **RDL Endura** TSV Etch CVD Liner PVD Barrier | Seed Cu Plating Planarization (Si/FE films) **TSV Formation** Nokota Centris **Reflexion LK** Producer Endura Sym3 Via Raider **LKP** InVia 2 **Ventura** Sym3X Mustang Silicon Polish Recess Etch **CVD LT Passivation** Cu & Oxide Polish **TSV Reveal Reflexion LK** Producer Centris **Reflexion LK** Sym3 Via Avila ILD Dep CVD Barrier/Seed PVD Cu Pad Fill ECD Cu CMP (w/Dishing) D2W Bonder Damascene Etch **Hybrid Bonding** Producer **Reflexion LK** Sym3 GT Endura Avila / UHP Mustang **LKP**

Cu ECD

**EnCoRe 2**

**TEOS**

000779

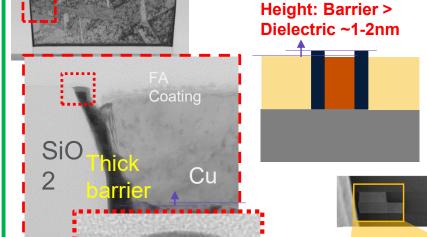

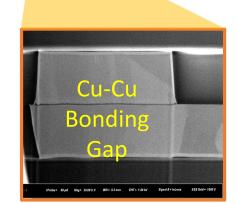

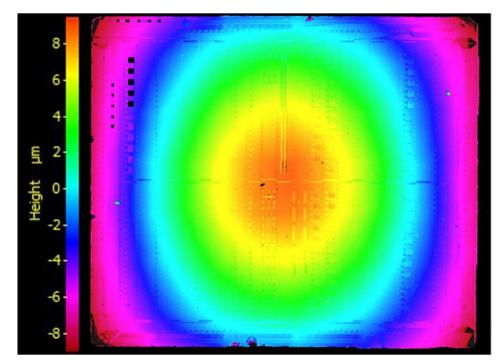

### **BEFORE OPTIMISATION**

Thick barrier having slightly protruding profile <u>before</u> anneal. After <u>anneal</u> it becomes worse due to higher thermal expansion than oxide

50 mm

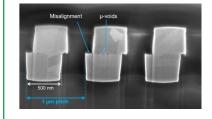

XSEM: showing Cu-Cu bonding gap

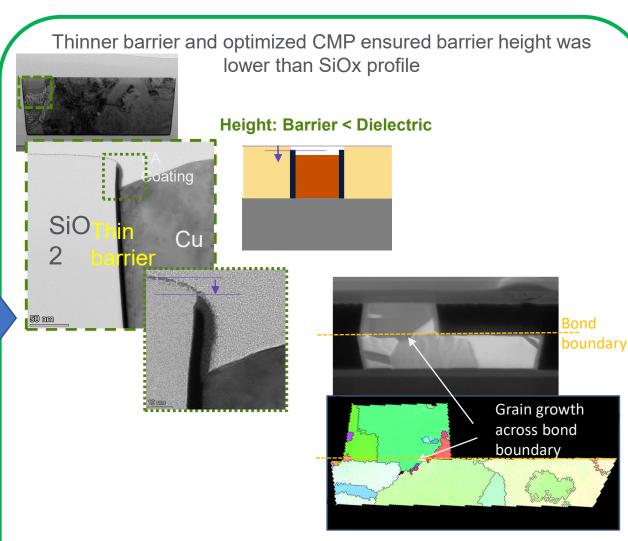

### AFTER OPTIMISATION

T-EBSD: showing grain continuity across bond

interface indicating successful Cu inter-diffusion

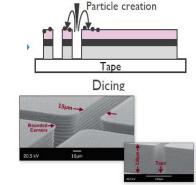

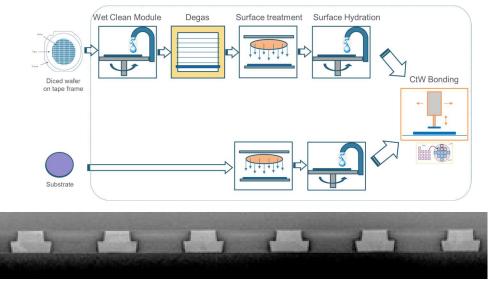

## C2W Hybrid Bonding Process Flow - Cleanliness

• Cleanliness is paramount for hybrid bonding. Any particle on the bonding surface can lead to poor adhesion, weak bonds, or complete failure of the bond

• Challenging for diced wafers on flexible tapes, since the dicing processes could introduce additional particles and/or contaminants.

Insufficient post-dicing cleaning could leave particles on the tape or die sidewalls

More particles on surface when stirred up from the tape or die sidewalls, causing delamination In TCB process, a small particle may have little effect

In hybrid process, a small particle may cause an open contact

**Total Clean Time**

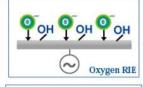

## C2W Hybrid Bonding Process Flow - Surface Activation

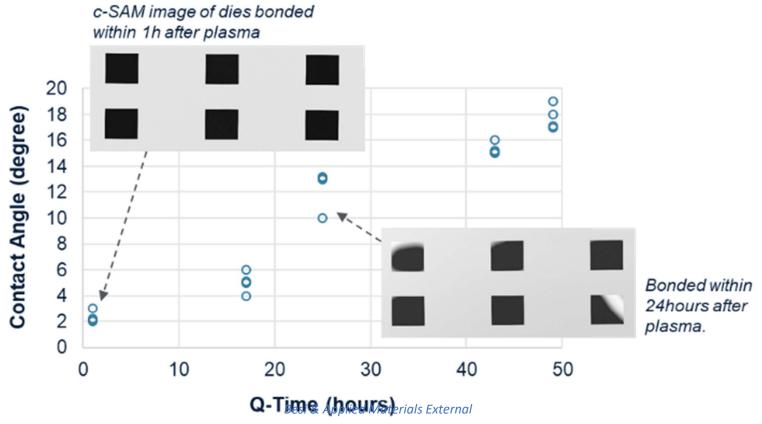

- Plasma activation effect and queue time impact on contact angle on SiO2 surface wrt bonding performance were investigated

- Bonding degrades with excessive queue time between activation and bonding as shown in C-SAM

- In correlation, the contact angle degrades over time if the wafers are exposed to air after activation, leading to poor bonding performance.

## C2W Hybrid Bonding Process Flow - Surface Activation

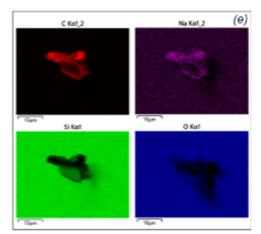

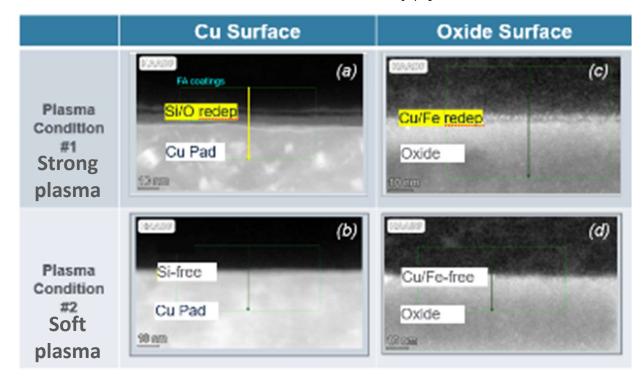

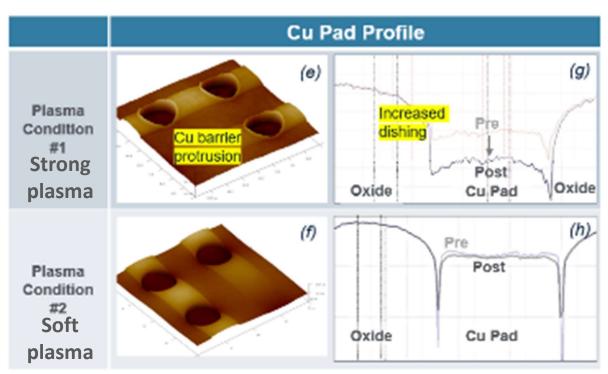

• When the ion energy is too high, the dielectric surfaces are roughened, which creates voids and diminishes the bonding performance.

- In addition, the sputtered materials from the dielectric surface and organic adhesive can further redeposit on the die surface

- The redeposition creates an undesired Cu diffusion barrier during the post-bonding annealing stage

- Copper pad profile is impacted resulting in increased dishing

- Ideal plasma should achieve surface roughness of <0.5 nm and etching of SiO2 of <1 nm

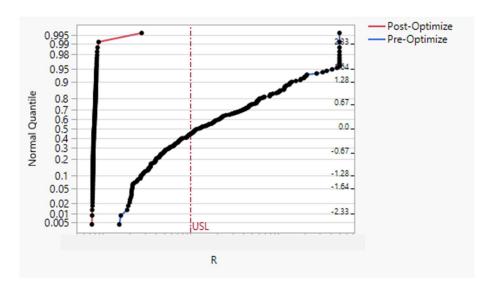

## Characterisation and Electrical Yield

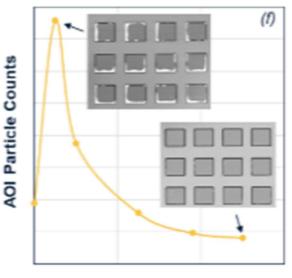

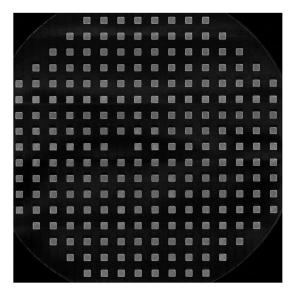

cSAM showing no gross random void indicating high cleanliness

Electrical continuity test on a 10k daisy chain (DC) connectivity

Normal-Quantile plot of 10k connectivity DC showing >99.5% yield (~230-dies)

- Electrical test shows a significant improvement for the post optimized process with >99.5% yield.

- The same test vehicle was used to characterize yield impact of queue time.

- Samples were processed with 36 hours queue time and compared with baseline; in HVM one could expect a queue time of 1 to 2 days bonding configurations with >3-5 different chiplets.

- Three bonded wafers from the "delayed" lot were compared to baseline. Conclusion is that adding queue time leads to significantly lower yield (80%) vs. the reference case (98%).

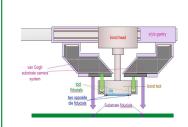

## 8800 Chameo Ultra Plus Chip-to-Wafer Hybrid Bonder

- First high-volume die-to-wafer hybrid bonder

- In production since 2022

- 200 nm placement accuracy

- At high speed of 2000 CPH

- Designed for use in front-end fab environment

- Die pickup from film frame and Silicon/glass carrier

- Integration via collaboration with AMAT

- 100 nm accuracy bonder in development

- Roadmap to <50 nm accuracy</li>

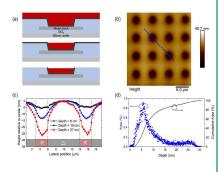

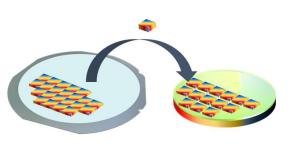

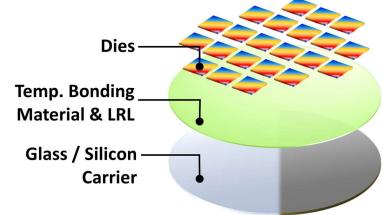

## Die to Wafer Bond Front Propagation

- To address the bond front propagation, tooling was developed which enables the die to be shaped in a convex manner, such that the initial point of contact when bonding is at the centre of the die.

- This ensures two things:

- 1. The initial contact causes instant bonding through Van der Waals's forces, thereby locking the die laterally and rotationally and minimising placement accuracy loss from possible mechanical influences.

- 2. This allows the air between die and substrate wafer to be expelled symmetrically outwards as the die is flattened, thereby ensuring equal conditions on all sides of the die as well as minimising risks of void entrapment.

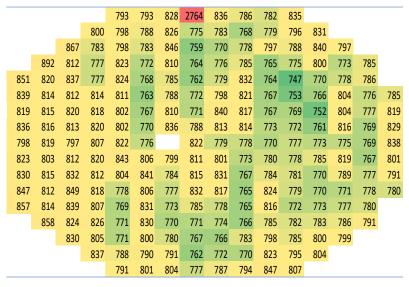

Top View (Pseudo Colour) of Shaped Die

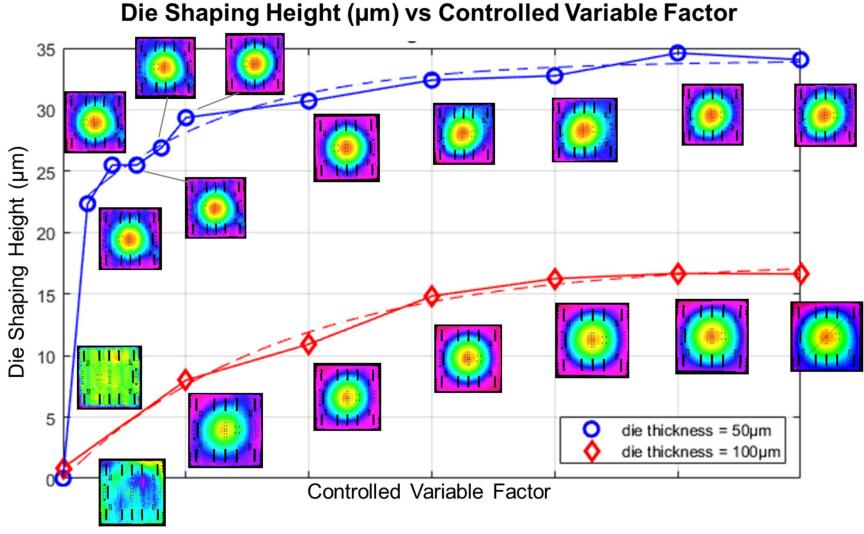

## Die Shaping for Bond Front Propagation

- For the 50µm thick die, the change in shape occurs at a much lower value for the controlled variable factor and that the maximum height is also larger.

- For the 100µm die, no get deformation for the first 4 values of the controlled variable factor can be measured.

- For 100µm, the maximum height is lower than the 50µm thick die, but both exhibit a similar behaviour whereby the maximum die shape height flattens out.

- At all stages following the initial conditions however, the first point of contact is always in the centre of the die.

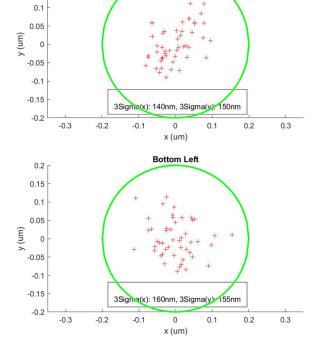

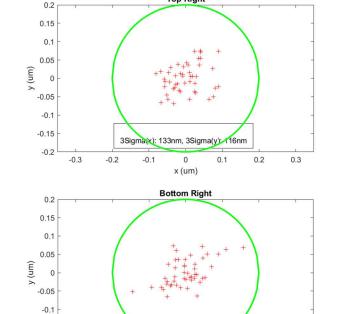

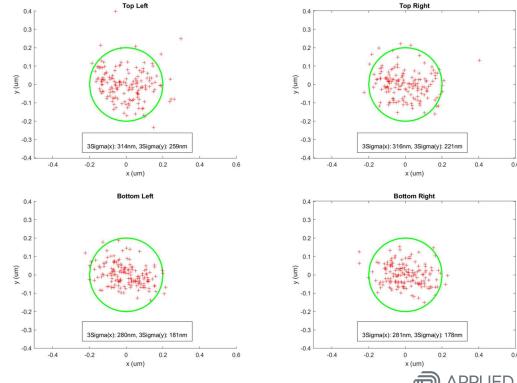

## Die-to-Wafer Overlay Results

0.2

### 160nm @ 3s worst case corner on TBM

-0.15

316nm @ 3s worst case corner Cu-Cu Hybrid Bonding

### Conclusions

- A working process flow for Die to Wafer Hybrid Bonding has been presented

- Positive outcomes of an HVM-capable process heavily depend on the cooptimization of many pieces of a complex technical jigsaw

- Importance of cleanliness was clearly demonstrated via voids formations arising from particle entrapment

- The bonding dielectric needs to be controlled in terms of surface roughness, and needs to be properly activated without damage.

- Control of queue time along the whole process is critical to guarantee optimal yield.

- Bonding process itself was realized with advanced dynamic die shaping capabilities and a state of the art overlay (160nm @  $3\sigma$ ).