# Advanced Packaging Materials and Open Innovation at Resonac

Hidenori Abe Senior Director, Electronics Business Headquarters **Resonac Corporation**

March 15, 2023

# Today's Presentation IMAPS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

- 1. Corporate Introduction

- 2. Introduction of Packaging Solution Center & JOINT2

3. R&D Status for Advanced Package

# Showa Denko Materials

(Former Hitachi Chemical)

# RESONAC Chemistry for Change

#### Other **10**%

Life science products etc.

#### **Chemical 34%**

Petroleum chemistry Chemicals Graphite electrode Sales (2021)

1,259

Billion¥

#### Innovation material 11%

High-functionary chemicals

High-performance resin

Coating material, Ceramics,

Aluminium functional component

# **Semi conductor and Electronics materials**

**31%** (392 Billion¥)

- 1. High purity Gas for semiconductor

- 2. CMP slurry

- 3. Epoxy molding compound

- 4. Die bonding material

- 5. Cupper clad laminate

- 6. Photosensibity film

- 7. Photosensibity solder mask

- 8. Hard disc

- 9. SiC epitaxial wafer

- 10. Composite semiconductor (LED)

#### **Mobility 14%**

**Automobile component Lithium-ion battery material**

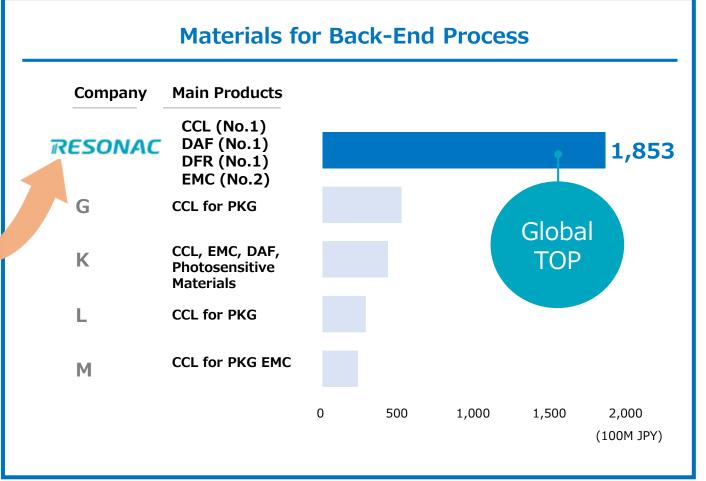

# Top Company in Semiconductor related Materials

#### **Top Share in Back-End Process**

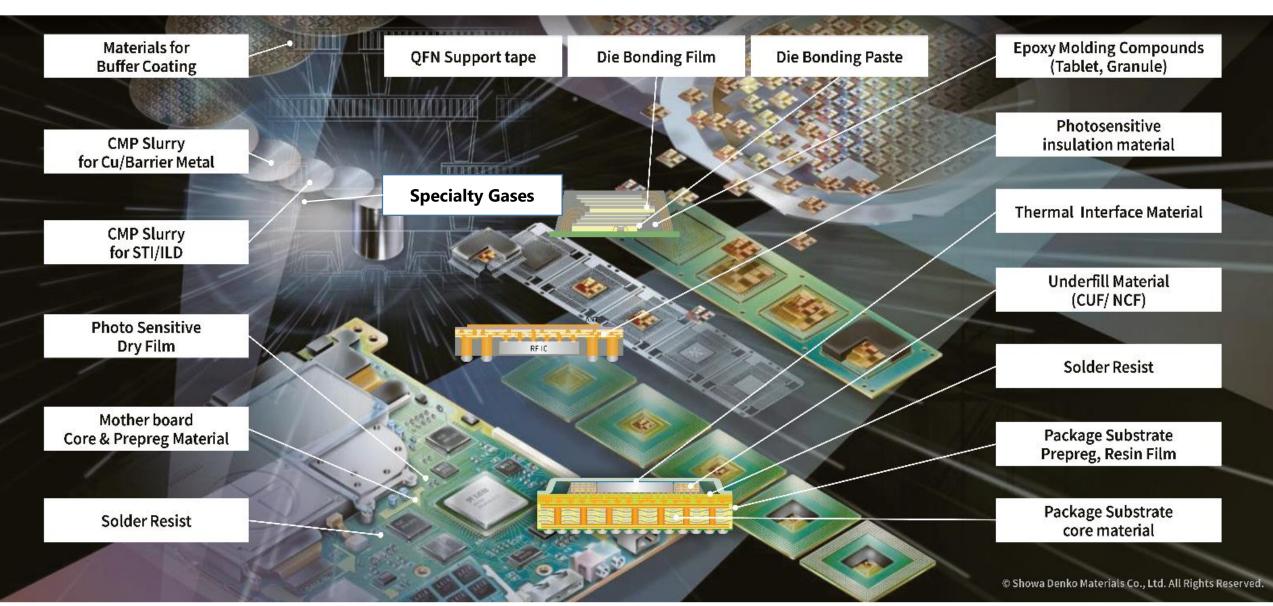

# Materials Line-Up for Semiconductor PKG

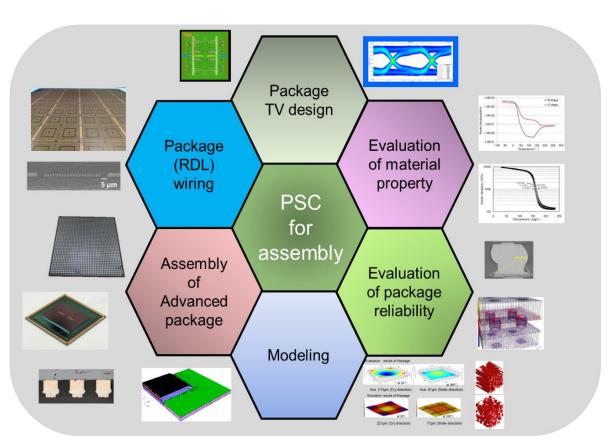

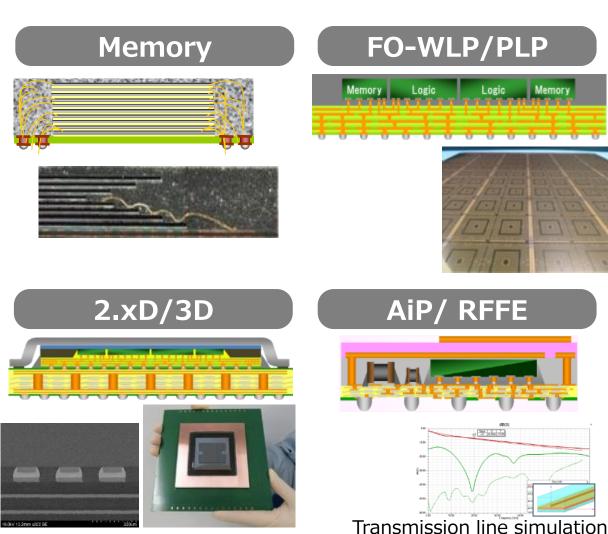

# Packaging Solution Center (PSC) March 13-16, 2023 | Fountain Hills, AZ USA

#### [ Strong point of PSC ]

- Global top for packaging R&D site

- Long term experience of PKG assembly and reliability evaluation (over 28 years)

- Deep knowledge of assembly evaluation

- Through integrated Assembly Line

- Combination and control of materials

#### Through collaboration ]

- Many experiences and results through Open Innovation

- Many connections among material and equipment suppliers.

**JOINT1**

**Function of PSC**

Regardless of the collaboration type, all activities are operated with utilizing PSC' key functions.

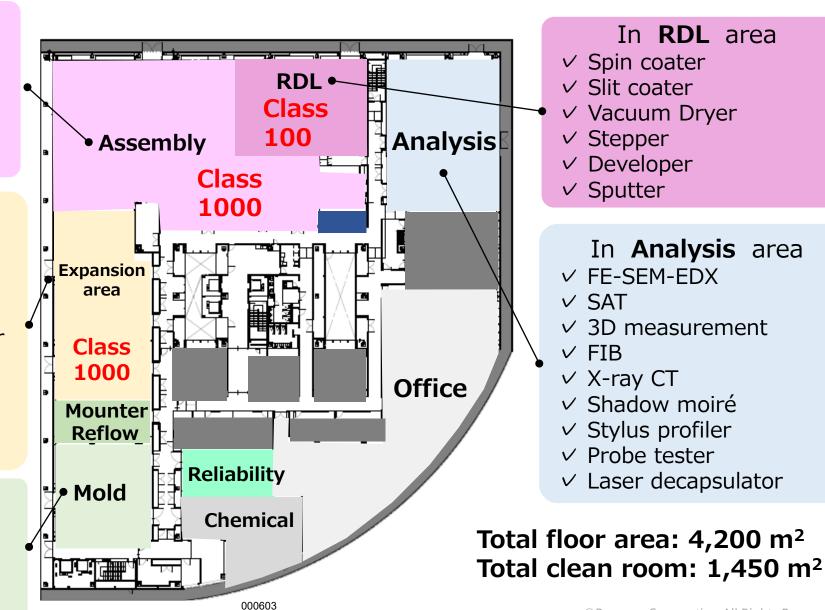

## 3<sup>rd</sup> Floor layout

#### In **Assembly** area

- ✓ Grinder

- ✓ Blade & Laser Dicer

- ✓ CoC, CoW flip chip bonder

- ✓ Laminator

- ✓ Plating

#### In **expansion** area

- √ C2W bonder

- ✓ Plasma asher

- ✓ Large die mounter

- ✓ Panel CMP

- ✓ Temporary bonder & debonder

- ✓ Compression molding

- √ C2W bonder

- ✓ Panel Grinder

- ✓ Panel Su/Ag plating

#### In Mold area

- ✓ Transfer

- ✓ Substrate Comp.

- ∨ Wafer Comp.

- ✓ Panel Comp.

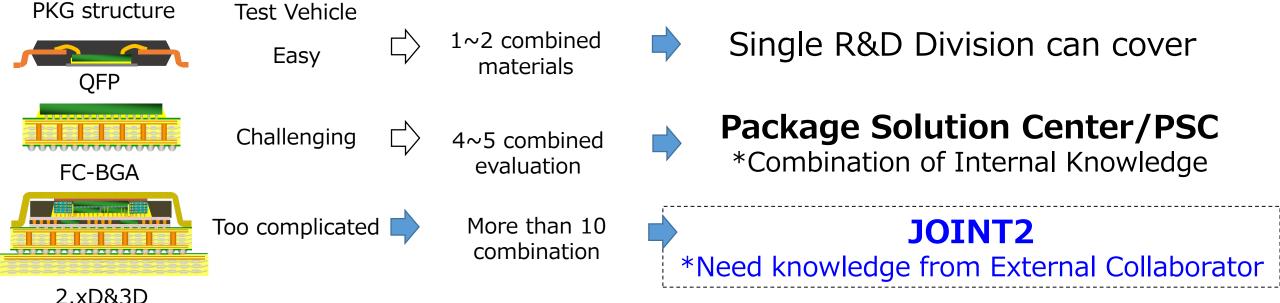

# Co-Creative R&D Platform IMAPS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

#### New consortium "JOINT2" for

- 1. unifying contact of each equipment & material companies to customer.

- 2. creating and increasing opportunity of discussion among equipment & material companies.

- 3. building advanced PKG test vehicle.

We hope these activities accelerate Customer's R&D and expand our material business.

#### RESONAC

# Be a leader in semiconductor technology innovation

#### "Open innovation platform" evolve to "Consortiums with multiple company"

Multiple working groups

X

Mutual utilization of technology and information

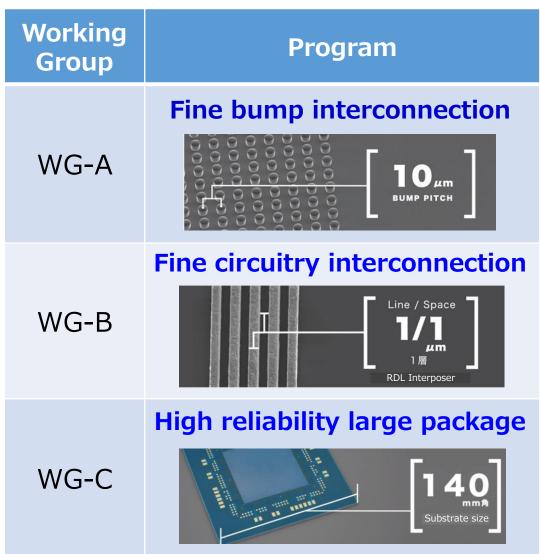

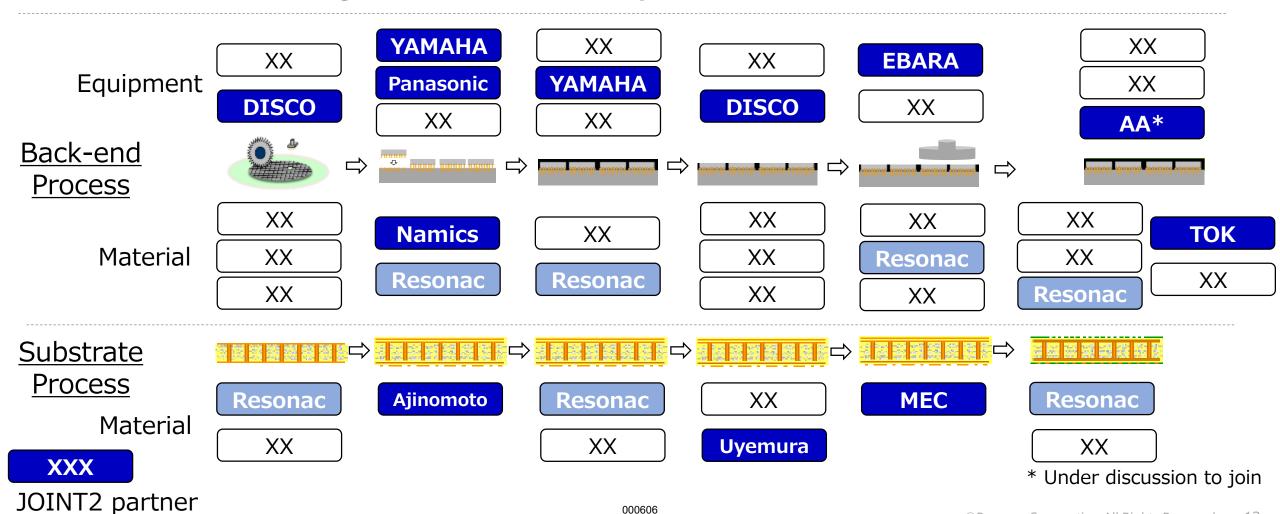

# Back-end Process & JOINT2 Partner

#### JOINT2 is unparalleled scale consortium with high market share companies for Back-end Process

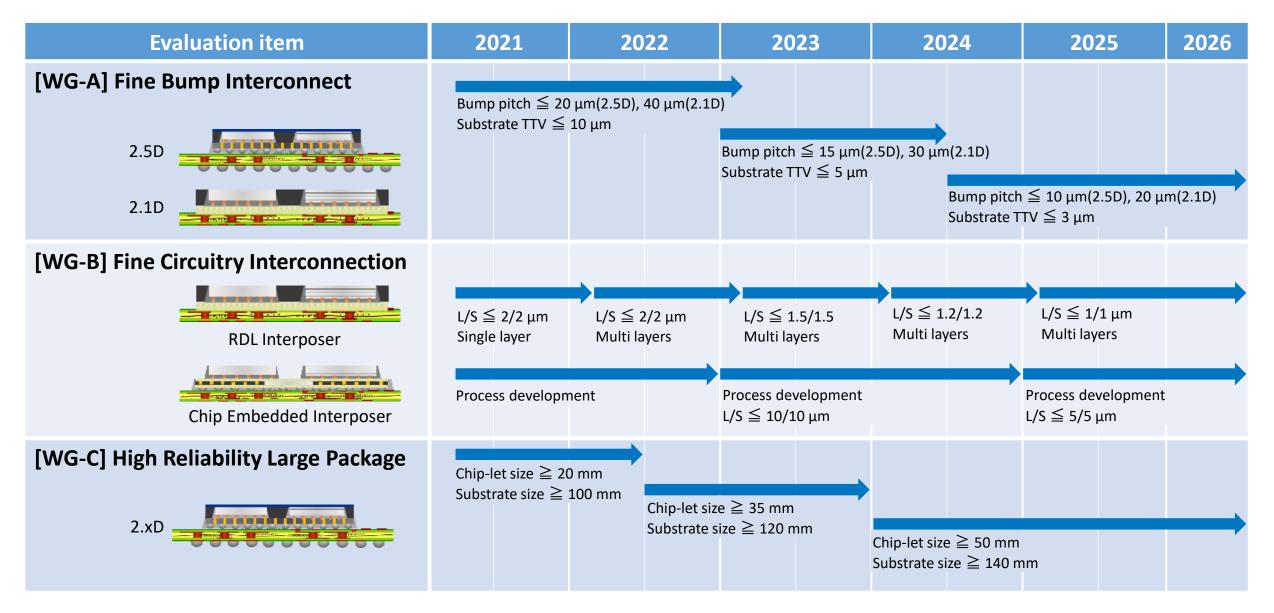

# Technical roadmap and schedule

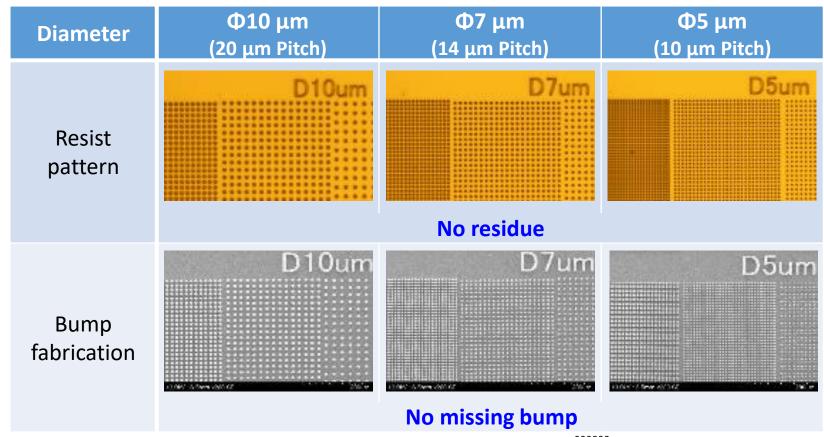

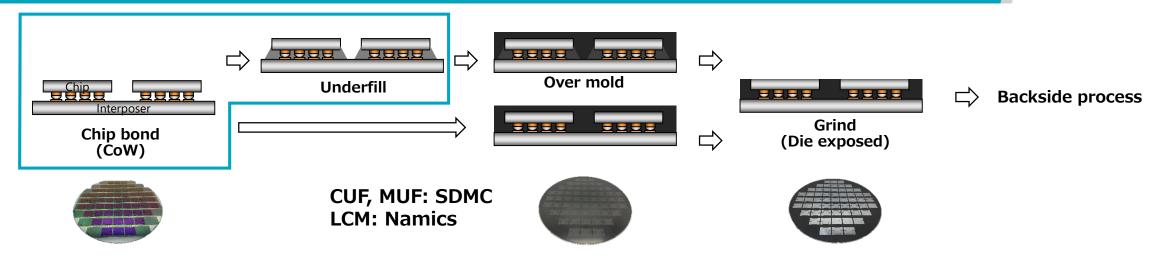

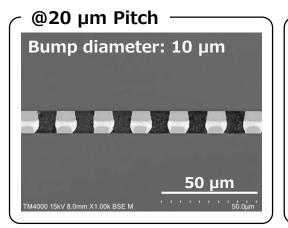

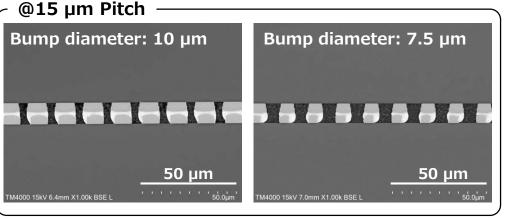

# Fine Vertical Interconnection Fine Bump Interconnection [Interconnection]

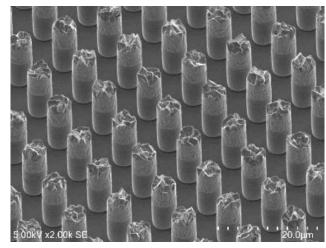

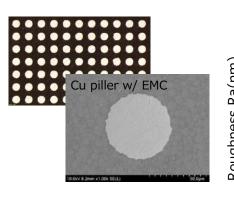

#### **SEM image**

Φ5 μm(10 μm Pitch) bump

### Fine Vertical Interconnection MAPS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

#### RESONAC

# Fine Pitch Underfill Technology

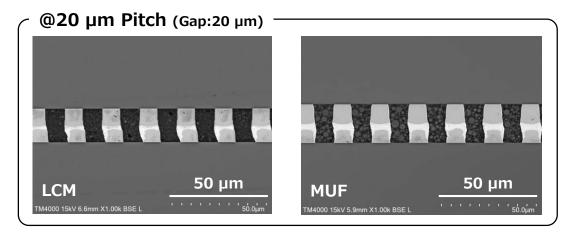

#### Cross section image after bonding and underfilling

**Excellent underfillability in narrow pitch and gap**

# Fine Vertical Interconnection 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA Fine Pitch Underfill Technology

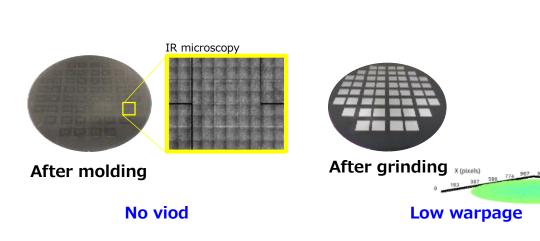

Cross section image after Compression mold (Bulk molding)

Achieves narrow gap filling by compression mold

microns

1384.6

-1384.6 -1692.3

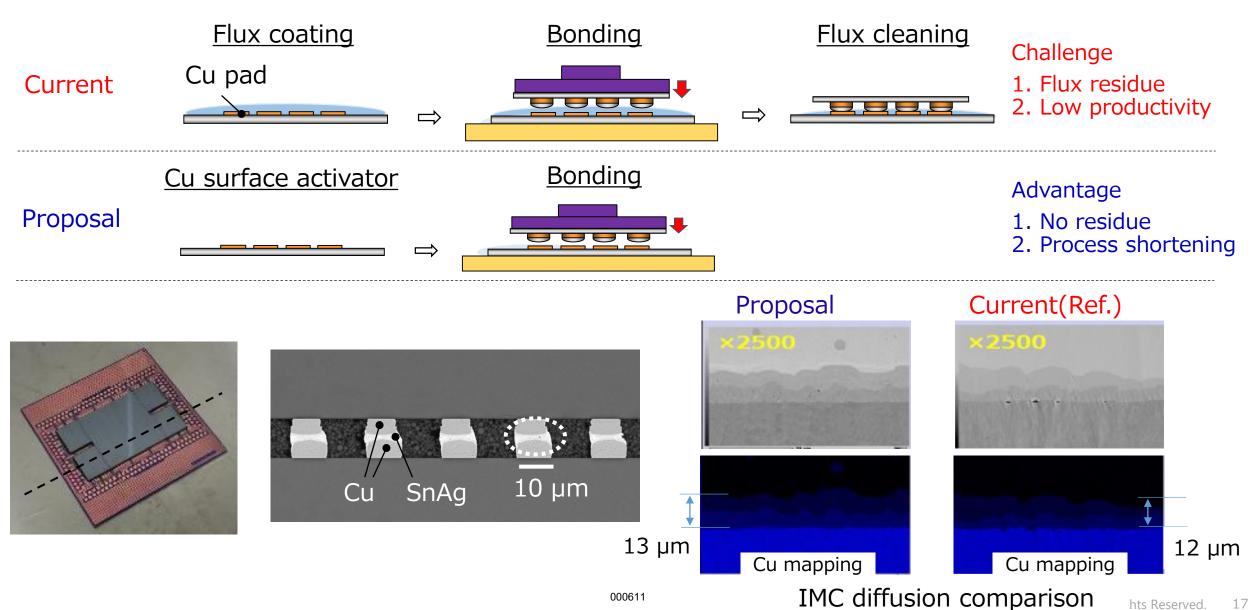

### Fine Vertical Interconnection, MAPS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA Flux-less Bonding Technology

## Fine Lateral Interconnection MAPS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

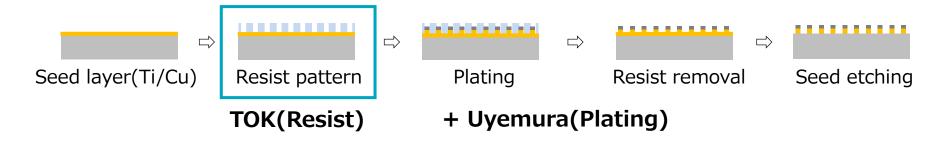

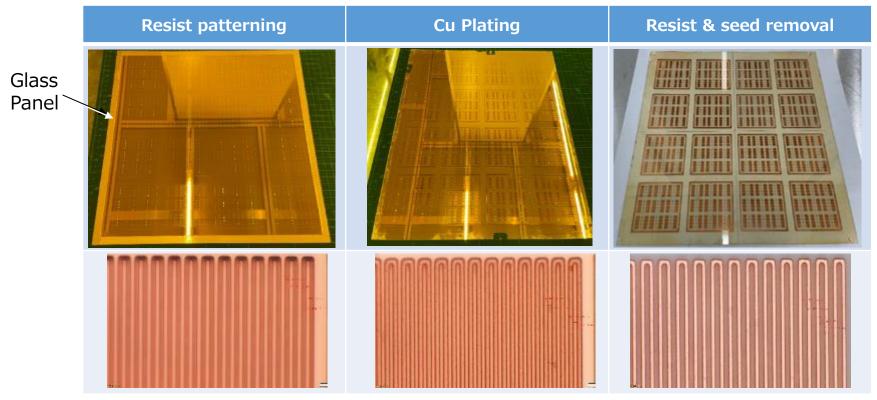

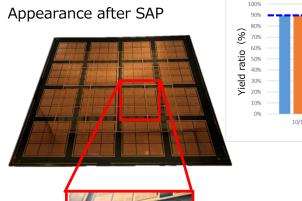

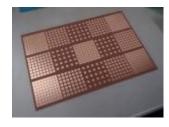

# RDL Interposer by Semi-Additive Process

Semi-additive plating

Polymer patterning

Resist patterning

Plating

Resist & seed removal

Panel size: 320x320 mm

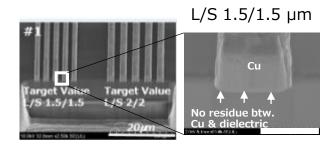

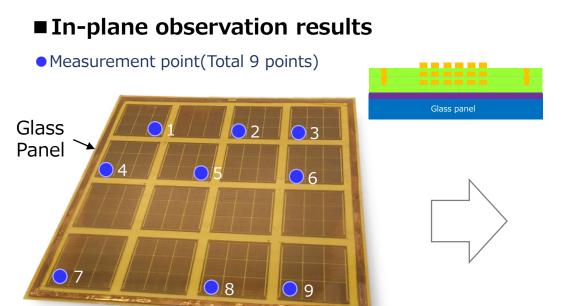

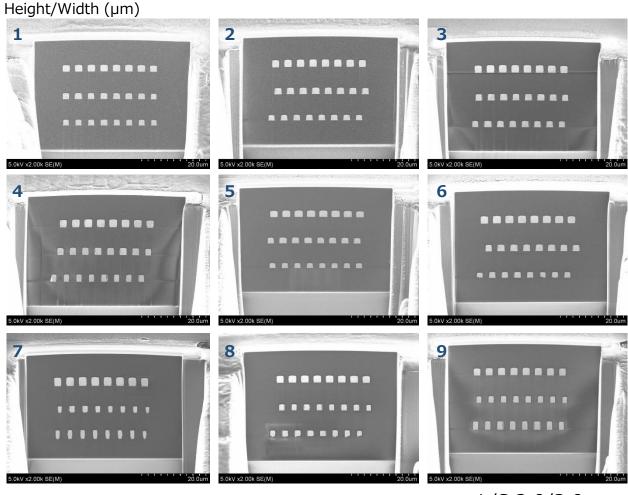

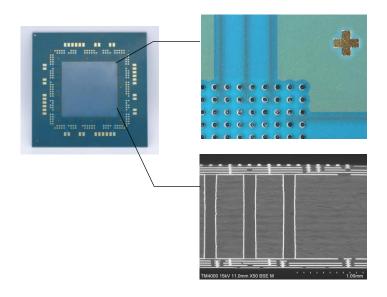

# Fine Lateral Interconnection APS 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA RDL Interposer by Semi-Additive Process

#### RESONAC

#### Fabrication results of three layers of Cu wirings by SAP

#### **Processing and imaging conditions**

Panel size: 515x510 mm

FIB: NB5000(Hitachi High-Tech Co.)

Accelerating voltage 40 kV

FE-SEM: S-4800(Hitachi High-Tech Co.)

Accelerating voltage 5 kV

L/S 2.0/2.0 µm

### Fine Lateral Interconnection Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA Chip Bridge Interposer

Leg5 Leg7 Leg1Over 90% Yield

Line / Space (µm)

Size: 320x320 mm

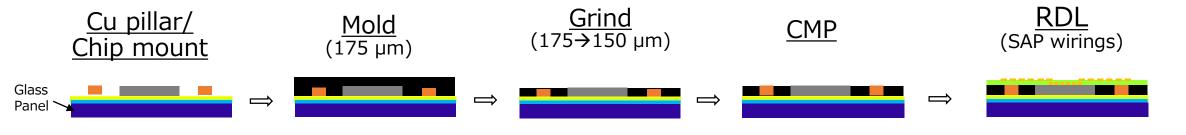

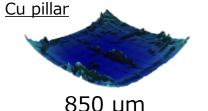

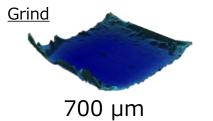

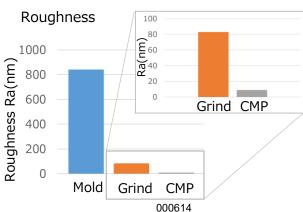

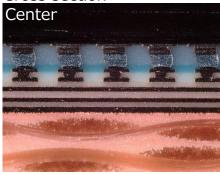

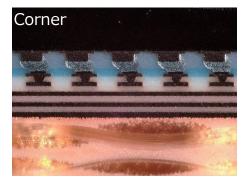

#### Panel Warpage

850 µm

Mold

2200 µm

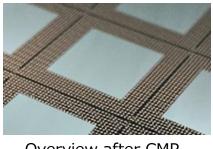

Planarization (CMP)

Overview after CMP

• RDL

### High Reliability Large Package 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

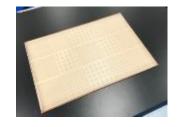

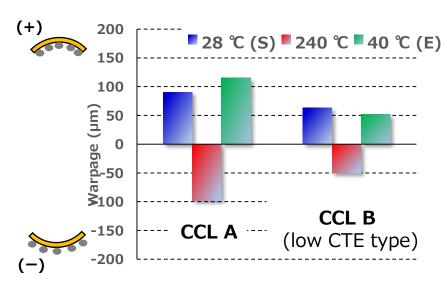

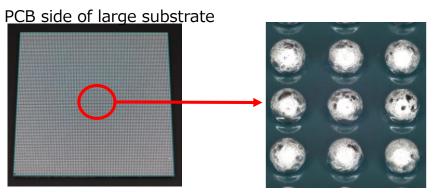

### Package Substrate Fabrication

**Fabrication** Process

Package

Board

#### Completed 100x100 mm substrate fabrication

| Substr       | ate Structure       | Target<br>Specification |  |

|--------------|---------------------|-------------------------|--|

| Layer        |                     | 4-2-4                   |  |

| Core         | Thickness           | 1.3 mm                  |  |

| Core         | Cu foil thickness   | 12 μm                   |  |

| BU           | Thickness on copper | 15 µm                   |  |

| Cu thickness |                     | 15 μm                   |  |

| SR           | Thickness on copper | 18 μm                   |  |

|              | SR opening          | SMD                     |  |

- ·Large substrates could be fabricated according to specifications.

- ·Warpage was suppressed by using low CTE CCL. ©Resonac Corporation All Rights Reserved.

### High Reliability Large Package 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

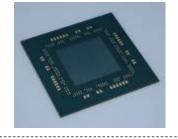

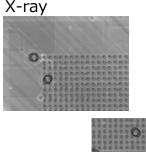

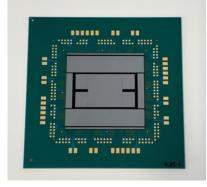

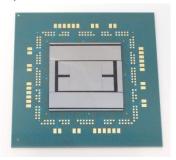

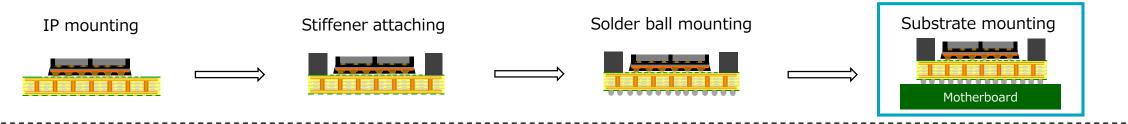

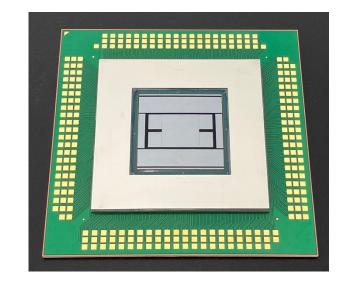

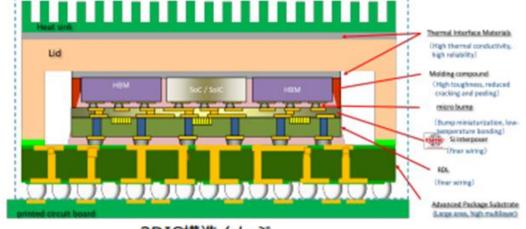

# Interposer / Substrate Mounting

#### Mounting process (Interposer, Substrate)

#### **IP** mounting

Solder joint (reflow)

X-ray

Cross section

Overview after IP mounting

Solder joints were formed with good alignment.

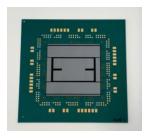

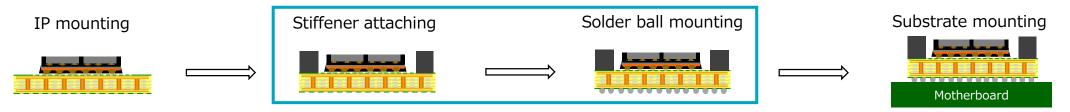

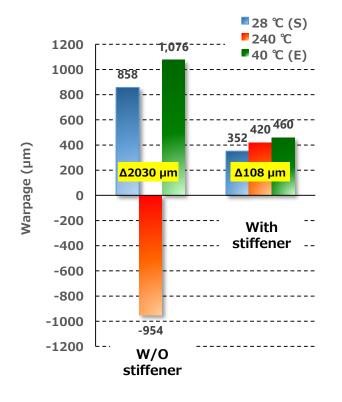

# High Reliability Large Package 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA Interposer / Substrate Mounting

#### Mounting process (Interposer, Substrate)

#### Stiffener attaching

W/O stiffener

With stiffener

#### Solder ball mounting

| Item       |           | Target Specification |  |

|------------|-----------|----------------------|--|

| Ball pitch |           | 1 mm                 |  |

| Ball size  |           | Ф600 µm              |  |

| Pad size   |           | Ф600 µm              |  |

| SR         | Structure | SMD                  |  |

|            | SRO       | Φ500 μm              |  |

Solder ball height: 478 µm (Avg.)

### High Reliability Large Package 19th Conference on DEVICE PACKAGING | March 13-16, 2023 | Fountain Hills, AZ USA

# Interposer / Substrate Mounting

#### Mounting process (Interposer, Substrate)

#### Mother board (PCB)

| Cro      | ss sec | tion |        |

|----------|--------|------|--------|

| <b>.</b> |        | iii  |        |

|          |        |      |        |

|          |        |      |        |

|          |        |      |        |

|          |        |      | Holoso |

| Item  |       | Target Specification  |        |

|-------|-------|-----------------------|--------|

| Layer |       | 28 (Simple structure) |        |

| Size  |       | 150x150 mm            |        |

| Thick | ness  | 2.8 mm                |        |

| Pad   | Pitch | 1 mm                  |        |

|       | Size  | Ф400 µm               |        |

|       | SRO   | Ф500 µm               | 000618 |

#### **Reliability sample**

Completed the reliability sample after mounting the 2.5D package substrate on the PCB.

#### **Packaging Solution Center in Silicon Valley**

- ✓ Assembly technology: Dicer, Bonder, Cleaner, Dispenser, Plating, Molding, Reflow, etc.

- ✓ RDL technology: Coater, Laminator, Exposure, Developer, Oven, Sputtering, Plating, CMP, etc.

- ✓ Reliability & Failure analysis technology: SEM, AFM, Reflow, TC chamber, B-HAST chamber

#### Partner Contribution Scheme

- ✓ Provide your State-of-the-art equipment and materials to realize customer's POC

- ✓ Cover our operating costs together with us

- ✓ Send your engineers to R&D site to cooperate with us

- ✓ Regular Projects to propose to both customers

- ✓ Some equipment and technology are open to use for your own project

If you are interested to join in this Ecosystem, please don't hesitate to contact us!

# RESONAC

「JOINT2 is being implemented under the "Research and Development Project for Strengthening Post 5G Information Communication System Infrastructure" (JPNP20017), a subsidized project of the New Energy and Industrial Technology Development Organization (NEDO), a national research and development agency.」

#### Note

Performance forecast and other statements pertaining to the future as contained in this presentation are based on the information available as of today and assumptions as of today regarding risk factors that could affect our future performance. Actual results may differ materially from the forecast due to a variety of risk factors, including, but not limited to, the influence of the coronavirus disease 2019 (COVID-19) on the world economy, the economic conditions, costs of naphtha and other raw materials, demand for our products such as graphite electrodes and other commodities, market conditions, and foreign exchange rates. We undertake no obligation to update the forward-looking statements unless required by law.

Japanese government semiconductor strategy by METI(Ministry of Economy, Trade and Industry)

#### 【参考】先端半導体製造MAKS後、正程。) on Devict なみ技術の開発。」 F採択にTAZUSZ 概要(1)

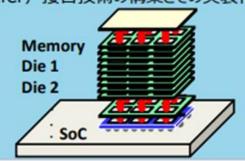

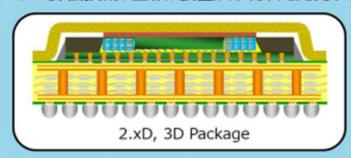

- 高性能コンピューティング、広帯域5Gネットワークスイッチング、自律走行の人工知能や統合センシング・診断等を実現する ためには、半導体デバイスのさらなる集積化・高性能化を可能とする3Dパッケージ技術(ロジック、メモリー、周辺デバイスを 1つのパッケージに高密度に実装する技術)の開発が不可欠。

- このため、本事業では、基板上実装技術(on-substrate technologies)を中心として、新しい加工材料、基板材料、 接合プロセス、新規の接合・計測機器技術等を含む3Dパッケージング技術について開発し、TSMCジャパン3DIC研究 開発センターが産総研のクリーンルームに構築するプロセスラインでの評価・検証を通じて、信頼性の高い組立技術として統合する。

- また、本センターは、日本の材料・装置メーカー及び研究機関・大学(下記)とのパートナーシップに強力に取り組む。最 先端の技術ポジションを獲得すべく、拡張性があり、製造可能で費用効果の高いソリューションの開発を行う。

パーパーカーシャール(つくば市)

3DIC構造イメージ

Mounting and assembly technology

実施者: TSMCジャパン3DIC研究開発センター株式会社

<パートナー企業・機関 (50音順) > ※下記に限定するものではない

【材料メーカー】旭化成、イビデン、JSR、昭和電エマテリアルズ、信越化学工業、新光電気工業、住友化学、積水化学工業、東京応化工業、長瀬産業、日東電工、日本電気硝子、富士フィルム、三井化学、【装置メーカー】キーエンス、芝浦メカトロニクス、島津製作所、昭和電工、ディスコ、東レエンジニアリング、日東電工、日立ハイテク、【大学・研究機関】産業技術総合研究所、先端システム技術研究組合(RaaS)、東京大学

quote: 20210531002-2.pdf (meti.go.jp)

\*Development target

(Development Items)

#### 【参考】先端半導体製造 ((後)正程)。 プロセス技術の開発: 採択示表で収 概要(2)~(5)

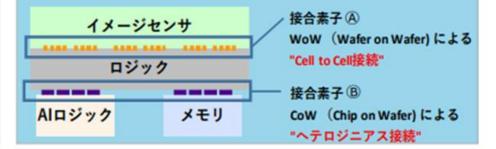

#### (2) 実施者: 先端システム技術研究組合 (RaaS) \*1

- 事業テーマ:ダイレクト接合3D積層技術開発 (WoWおよびCoW向け装置・プロセス開発)

- 概要: Cu-Cu の低温ハイブリッド接合による WoW (Wafer on Wafer) 接合技術及び CoW (Chip on Wafer) 接合技術の構築とその実装化に取り組む。

#### (4) 実施者:昭和電エマテリアルズ株式会社※2

- 事業テーマ:最先端パッケージ評価プラットフォーム創成

- 概要:基板、装置、材料メーカーによるコンソーシアムを 創成、評価プラットフォームを設置し次世代半導体パッ ケージの評価技術、基板、装置及び材料を開発する。

#### (3) 実施者: ソニーセミコンダクタソリューションズ株式会社

- 事業テーマ:ポスト5 Gエッジコンピューティング向け半導体の3D積層要素技術研究開発

- 概要:積層モジュールの基本特性および信頼性取得が可能となるピッチサイズ目標を年度ごとに設定し、ロバストな半導体製造プロセスの要素技術を確立する。

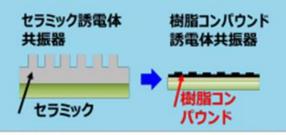

#### (5) 実施者: 住友ベークライト株式会社

- 事業テーマ:次世代情報通信向け先端パッケージの材料開発

- 概要:3次元実装密度向上において重要となる、 Wafer Level PKG向け封止材、アンテナ向け封止材、 再配線用感光材のファインピッチ対応技術を開発する。

- ※1 (共同実施先、組合員企業等)国立研究開発法人産業技術総合研究所、SCREENホールディングス、ダイキン工業、富士フイルム、パナソニックスマートファクトリンリューションズ、東京大学

- ※2 (共同実施先、協力企業等)味の素ファインテクノ、上村工業、荏原製作所、新川、新光電気工業、大日本印刷、ディスコ、東京応化工業、TOWA、ナミックス、バナソニックスマートファクトリーソリューショ

ンズ、ヤマハロボティクスホールディングス

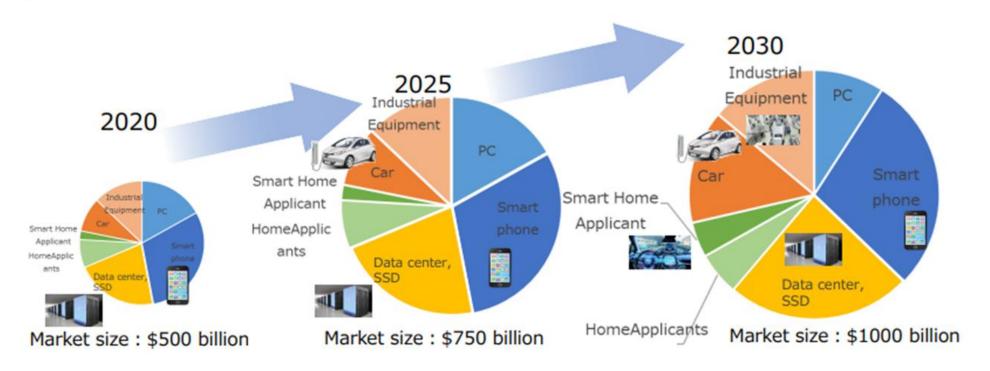

#### Basic Semiconductor Revitalization Strategy in Japan

#### Step 1: Enhancement of Basic Production Capacity for IoT

# Step 2 : Realization of Next Generation Semiconductor Technology through JP-US Collaboration

(Reference): prepared by METI, based on data from OMDIA

#### Step 3: RD For Future technology

Photonics-Electronics Convergence, Quantum Computing through Global Collaboration

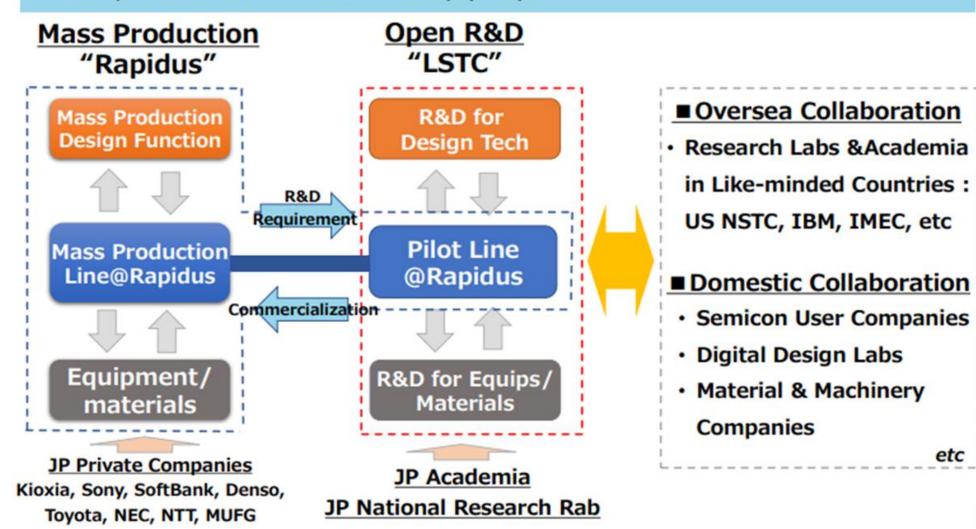

#### Project Framework for Next Generation Bewond Ram Project (B2P)

<METI announcement on 11th Nov.>: Establishment of Two Entities for B2P

- 1. "LSTC": Open Collaborative R&D Platform (Public Entity) \*\*Leading-Edge Technology Center

- "Rapidus": Mass Production Entity (Inc.)

etc