# Performance Enablement Through VIPack FOPOP for Mobile and Networking

Meiju Lu & Vincent Lin- ASE CRD Chienfan Chen A5 Mark Gerber –Engineering & Technical Marketing March 2023

aseglobal.com

#### **Outline:**

- Market Drivers

- Mobile & Network Performance Driver and Solutions

- SiPh FOPOP Sub Module & Key Attributes

- Electrical and Thermal Modeling Simulation

- Wafer Level Optical Test

- Conclusion

#### **Market Drivers**

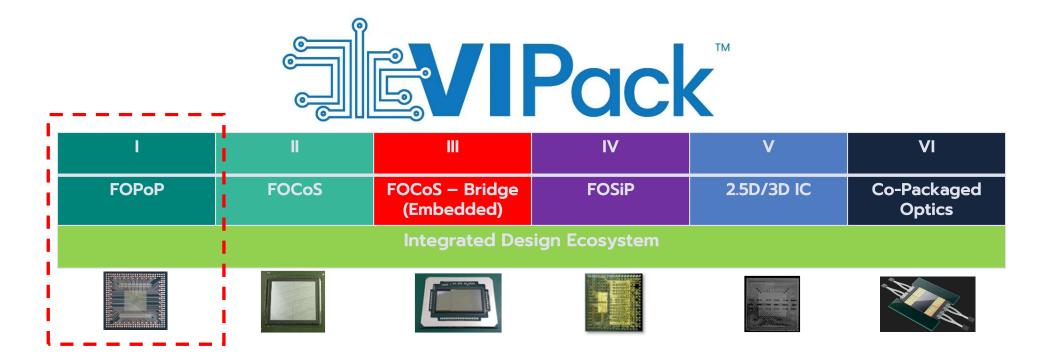

# Vertically Integrated Package Platform - VIPack™

#### **FOPOP Mobile & Networking Performance Enablement**

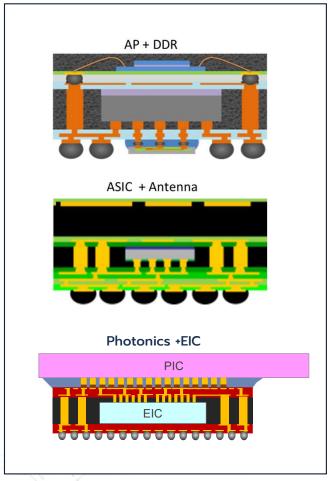

#### **Application:**

- AP + DDR Memory (4G/5G)

- ASIC + Antenna (5G)

- SiPh + EIC (Networking)

#### **Development Features:**

#### Mobile:

- Thinner Form Factor

HBPoP ~550um

FOPoP below 400um

- TMV + Double-side RDL Layer

- Thin passive IPD integration

- Heterogeneous surface grinding

- Wafer form memory stacking

- Embedded Molding Structure

- Lower Impedance/Insertion Losses in RDL vs HBPOP

#### **Networking:**

- Reduced Critical Lengths between PIC/EIC

- XY Size Reduction for additional sub-module integration

- Advanced Process Technology for Photonic Die Etching & Plating

- Bandwidth Density Enablement (Size, Critical Length Reduction)

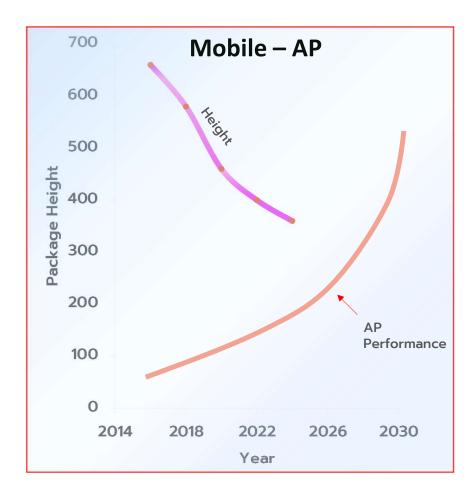

## **Mobile Performance Drivers & Solutions**

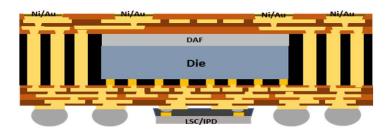

#### **Mobile Applications Processor – Device Example**

- DAF Die

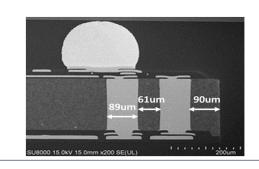

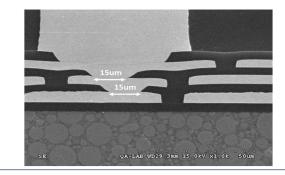

- √ PKG THK 389um (w/ ball) √ RDL L/S 5/5um

- Die THK 135um

- DAF THK 25um

- ✓ Cu stud 20um

- ✓ Cu post pitch 150um

- ✓ Solder ball 135um

- - ✓ RDL THK 5um

- ✓ Pl via 15um ✓ PI THK 5um (on RDL)

- ✓ Die to pillar 110um

- √ FS & BS-RDL 35/39um.

- √ 150um pitch Cu pillar w/ 180um THK

- √ Tall pillar to PKG edge is 90um (<100um)

</p>

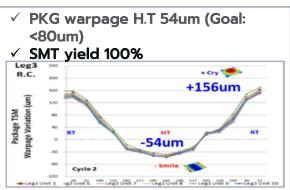

- ✓ PNL warpage 0.5~2.0mm (Goal: <2.5mm)</p> √ No handling issues Wafer Warpage -1500 -2500 -3000

- √ No delamination be found SAT 100% pass

- ✓ PI via 15um

- ✓ RDL flatness on stacked via w/out dimple

# Reliability Test Result of FOPoP

#### ☐ L0 CLR / BLR / Drop test passed

<u>CLR</u>

130°C/85%RH CondB-55C-125C

|     | TO<br>SAT | MSI   | .1    | uHAS  | T192  | TCT1000 |       |  |

|-----|-----------|-------|-------|-------|-------|---------|-------|--|

| CLR |           | O/S   | SAT   | O/S   | SAT   | O/S     | SAT   |  |

| 1   | 0F/90     | 0F/90 | 0F/90 | 0F/45 | 0F/45 | 0F/45   | 0F/45 |  |

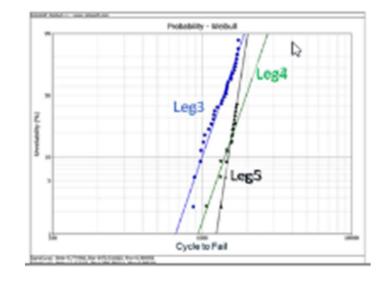

## **BLR**

| -400 | to | 850 |

|------|----|-----|

| WR<br>Leg# | BS_Cu Ratio<br>RDL1/2 | PCB<br>Side | UF | Net    | Cycle Count | # of Fails | 2-P Weibull Statistics |      |      |        |       |

|------------|-----------------------|-------------|----|--------|-------------|------------|------------------------|------|------|--------|-------|

|            |                       |             |    |        |             |            | First Fail             | 5%   | 50%  | 63.20% | Beta  |

| 3          | 69.12%/73.5%          | A           | No | Signal | 1774        | 30F/30     | 875                    | 880  | 1382 | 1473   | 5.77  |

| 4          | 68.93%/73.3%          | А           | No | Signal | 1774        | 13F/30     | 1340                   | 1414 | 1737 | 1788   | 12.63 |

| 5          | 65%/65%               | А           | No | Signal | 1774        | 8F/30      | 1068                   | 1248 | 1970 | 2100   | 5.71  |

## **Drop Test**

| WR   | BS Cu Ratio  | РСВ  | UF  |        | Cycle Count | # of Fails | 2-P Weibull Statistics |    |     |        |      |

|------|--------------|------|-----|--------|-------------|------------|------------------------|----|-----|--------|------|

| Leg# | RDL1/2       | Side | OF. | Net    |             |            | First Fail             | 5% | 50% | 63.20% | Beta |

| 3    | 69.12%/73.5% | Α    | No  | Signal | 30          | 0F/60      | -                      | -  | -   | -      | -    |

| 4    | 68.93%/73.3% | А    | No  | Signal | 30          | 0F/60      | -                      | -  | -   | -      | -    |

| 5    | 65%/65%      | А    | No  | Signal | 30          | 0F/60      |                        | -  | -   |        | -    |

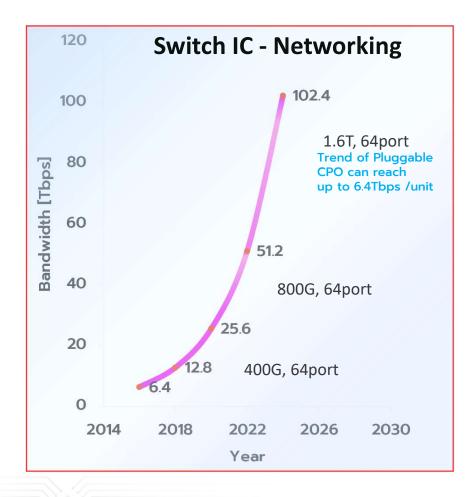

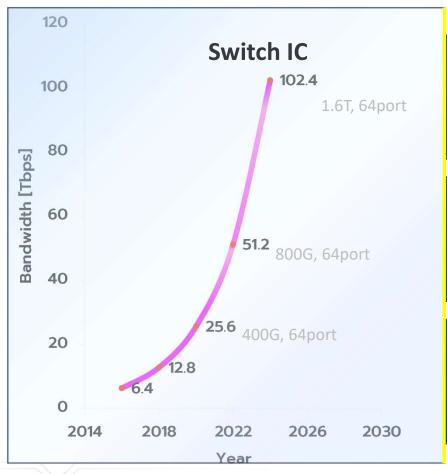

# **Networking Drivers and Solutions**

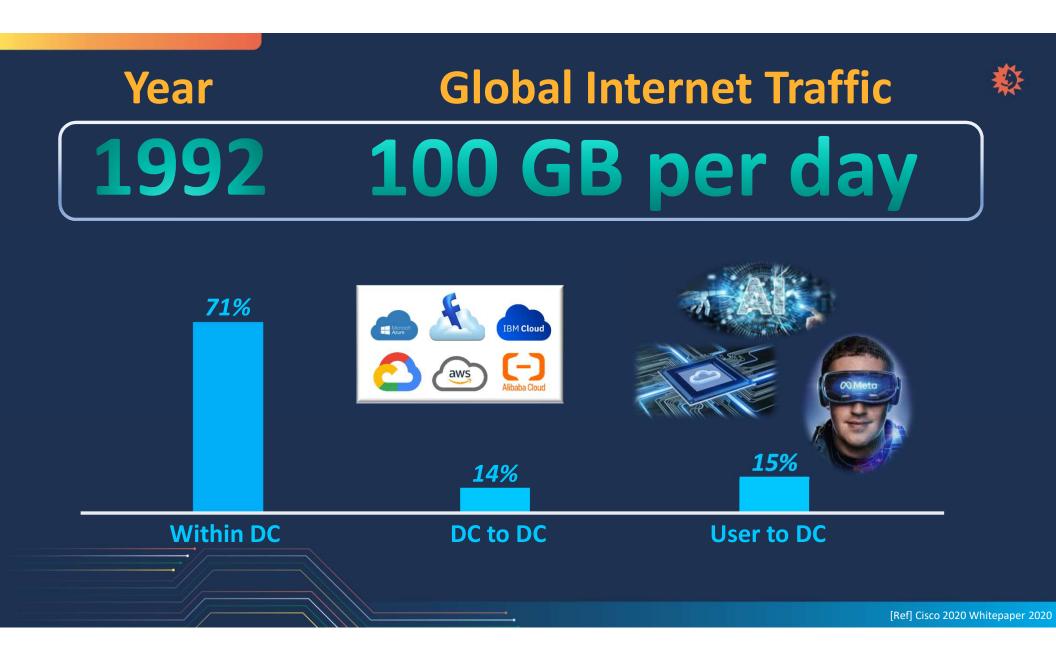

# **Emerging Application Markets**

# **Speed Evolution**

# Replace Cu with Optics

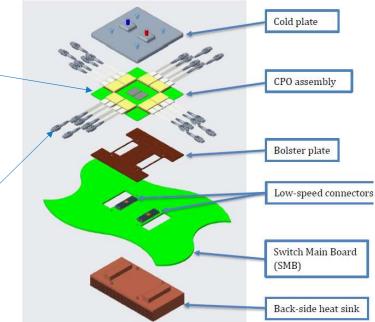

# **Background: Co-packaged Optics (CPO)**

#### System-level Requirements

Switch IC to Optical Electrical Interface

- CEI-112G-XSR

#### Optical Fiber Connections

- TX/RX fibers 2x (1x8) for 3.2T module

- ELS fiber 4x for 3.2T

- Total fiber count: 320

#### Power:

- Switch-51T:900W

- Optical: 1024W, 128 x 8W/400G

- Underside voltage regulators

#### Thermal Considerations

- Top surface components cold plate with water-cooled solution

- Underside heat sink: contact the voltage regulators

Ref: Co-Packaged Optic Assembly Guidance)

www.copackagedoptics.com

20.1±0.13 22.5±0.13

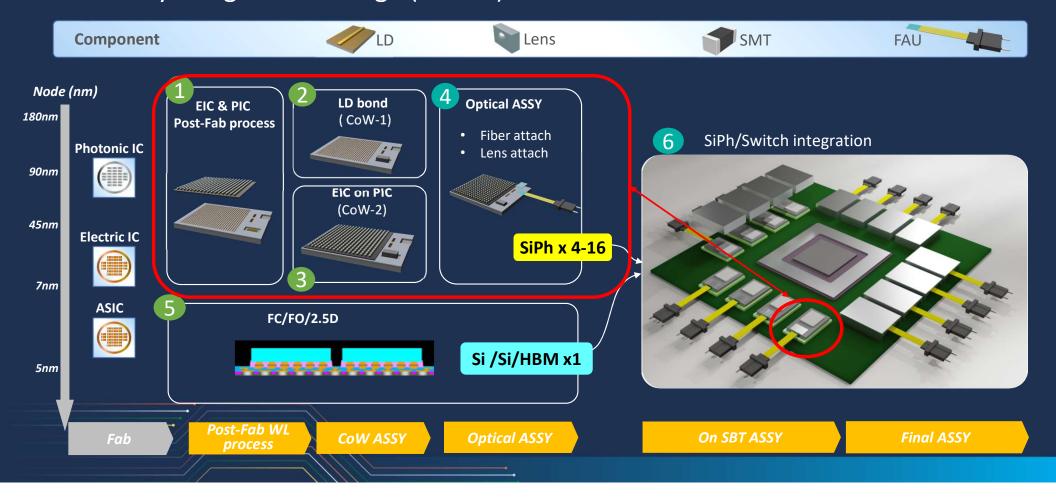

# **Key Integrating Technologies & Flow**

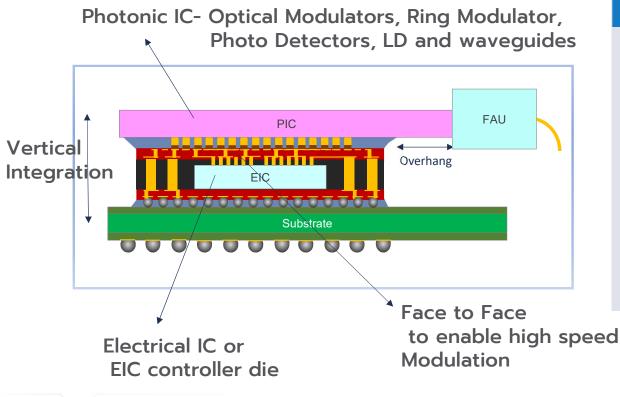

Vertically Integrated Package (VIPack)- FOPOP

## **Key Integrating Technologies**

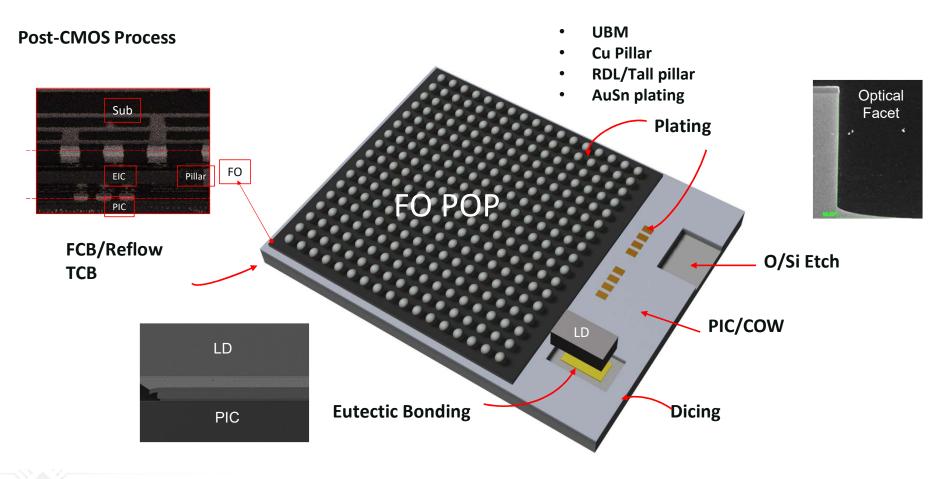

#### **Typical Structure Attributes for SiPh FOPoP (Custom By Device)**

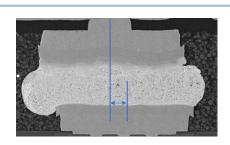

#### Typical Dimension (Ref: copackagedoptics.com) SiPh engine size ~20x20mm **PIC WLCSP** ~3mm overhang 16x16mm THK:200um **FO POP PKG size** (with T/B CuP bump height) PIC die size 18x17mm THK:750um - With or without V-groove - Typical V-groove pitch 200um Fiber coupling area - Typical V-groove length 2mm - 8-16 channels **PIC Lid** - With overhang or w/o overhang **Bump Pitch** - Typical 130um

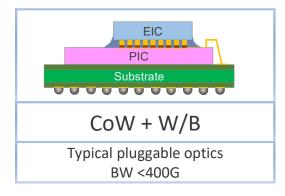

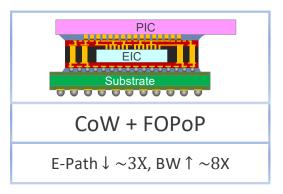

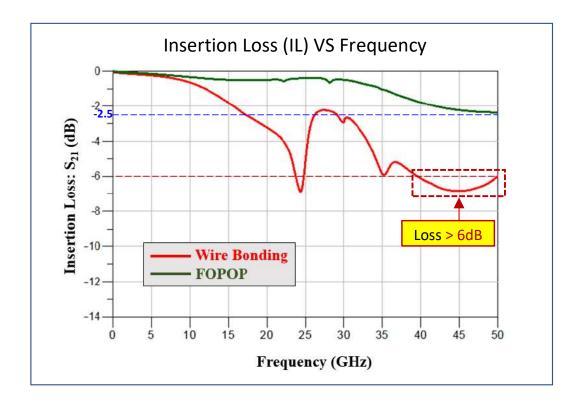

## SiPh FOPoP - Electrical Simulation (FOPOP vs COW+WB)

#### SiPh FOPoP - Thermal Simulation

| Package Type                                                      |     | CoW + W/B     | CoW + FOPoP       |  |  |  |

|-------------------------------------------------------------------|-----|---------------|-------------------|--|--|--|

| Thickness                                                         | EIC | 1             | 0.07              |  |  |  |

| (a.u.)                                                            | PIC | 1             | 1                 |  |  |  |

| Relative                                                          | EIC | 68.55         | 69.64             |  |  |  |

| Temperature (°C)                                                  | PIC | 67.30         | 67.43             |  |  |  |

| Structure                                                         |     | PIC Substrate | PIC EIC Substrate |  |  |  |

| Simulated<br>Data<br>Package with heat sink<br>under 2m/s airflow |     |               |                   |  |  |  |

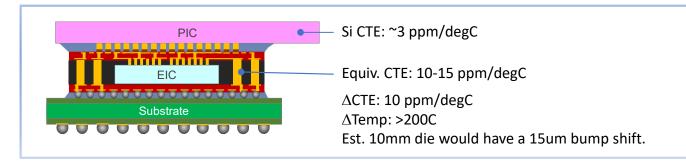

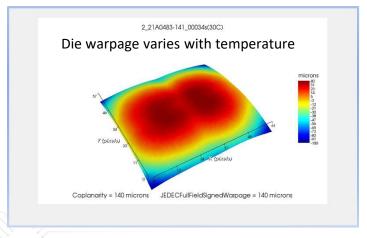

#### SiPh FOPoP - CTE Mismatches/Warpage Simulation

Challenges: CTE Mismatch/Warpage

#### [Mitigation Path]

- Proper fan-out design & consideration

- Material selection

- Proper assembly flow

- Bump joints via localized heating

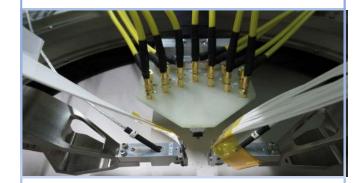

## **Wafer-level Optical Testing**

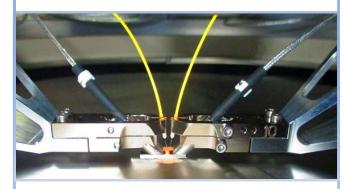

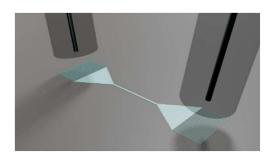

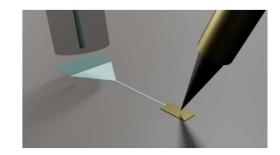

#### **Single Fiber Probing**

Probe Type: Single mode fiber

Holder: Single fiber

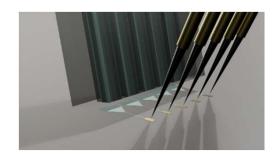

## **Fiber Array Probing**

Probe Type: 16ch fiber array

Holder: 8 or 10deg

# **Wafer-level Optical Testing**

| Types | Optical<br>Testing                           | Optoelectronic<br>Testing                                                                          |

|-------|----------------------------------------------|----------------------------------------------------------------------------------------------------|

| DUT   | <ul><li>Waveguide</li><li>Splitter</li></ul> | Diode laser, photodiode, modulatoretc.                                                             |

| Probe | • SMIE/EALL for both norts                   | <ul><li>SMF/FAU for optical port</li><li>Single DC probe/probe card for electrical port.</li></ul> |

#### **Conclusion**

- The Package-on-Package platform has evolved to enable a next level of performance for both Mobile and Networking through the VIPack FOPOP pillar

- Mobile Application Processors continue to require reduced height while addressing power delivery challenges by leveraging RDL Height benefits and reduced CL.

- Within the Network market space, higher bandwidth density is driving new integration requirements which are being enabled by the VIPack SiPh FOPOP structure

- The more photonic sub-modules that can be integrated, the higher the bandwidth, therefore, size of the Co-Package-Optics module is critical.

- Simulation data shows the SiPh FOPOP shows a reduced insertion loss when compared to the W/B format and showed equivalent thermal performance.

- The VIPack FOPOP and new process enhancements around the photonics die are enabling the next generation of Co-Packaged Optics Network solutions.