## **ADVANTEST**

Advanced Test Technologies for Heterogeneous & 2.5D/3D Packaging

March 2023

Marc Hutner, proteanTecs | Ken Butler, Advantest Inc

## Introduction

- Multi-Chip packaging is enabling the next wave of innovation in electronics

- Driving increased test complexity for wafer and package testing

- Die-to-Die (D2D) interfaces are an enabler SIP with improved power per bit transmission

- We will present a test solution for D2D interfaces that enables

- Full test solution where we present silicon results and test method at ATE

- Provides per-lane parametric grading

- Adaptive tester decision making leveraging trained functions

2 / **protean**Tecs

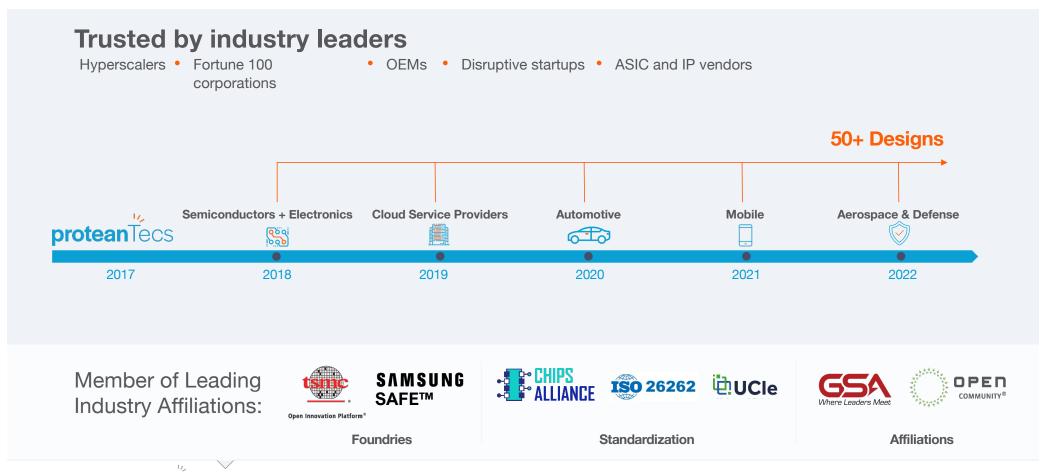

# proteanTecs at a glance

3 / proteanTecs

proteanTecs | Advantest Inc. for IMAPs 2023. All rights reserved.

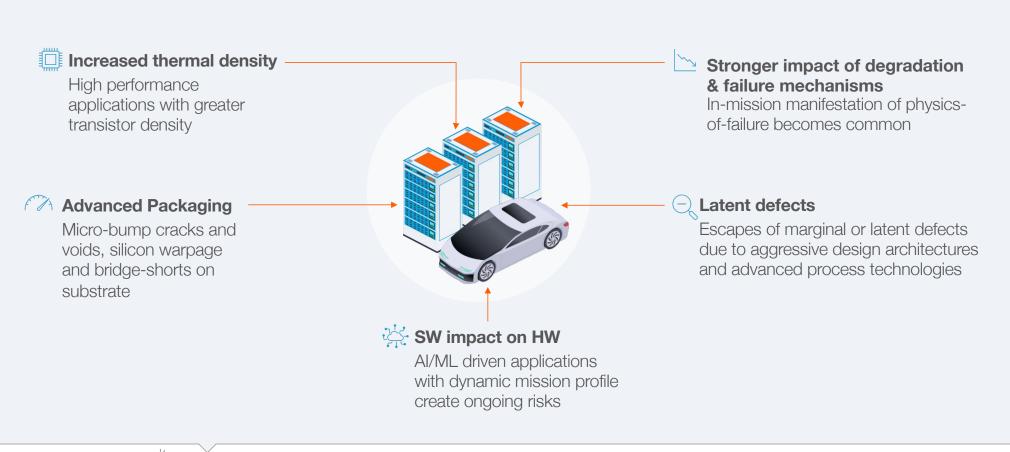

## **Increasing Challenges in Advanced Electronics**

4 / proteanTecs

proteanTecs | Advantest Inc. for IMAPs 2023. All rights reserved.

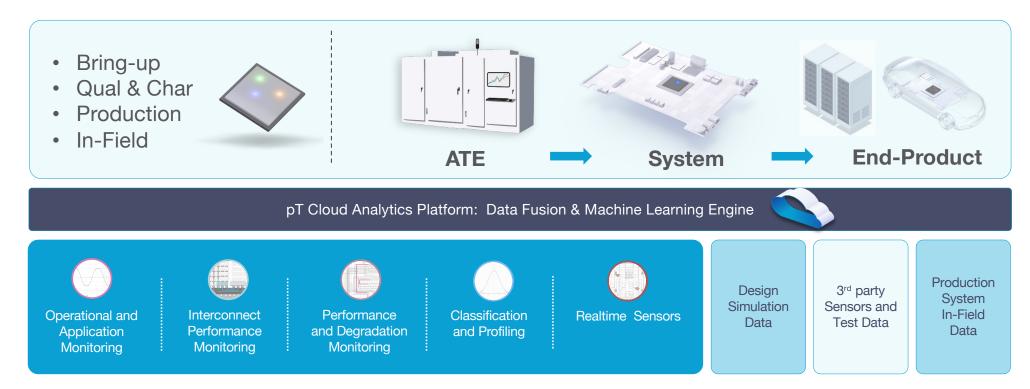

# Advanced Analytics Based on Deep Data

Agents + Simulations + SW Platform = Targeted Analytics & Insights

# **Targeted Applications per Stage**

Post to Pre silicon correlation

Correlation between value chain stages

Die-to-die visibility

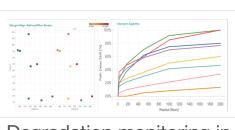

Degradation monitoring in qualification

#### Chip Production

Chip NPI

DPPM Reduction (Fine grain latent defects screening)

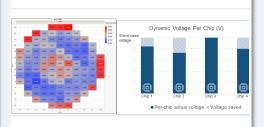

Power reduction

Test time reduction

Lower RMAs and Fast Time-to-Resolution

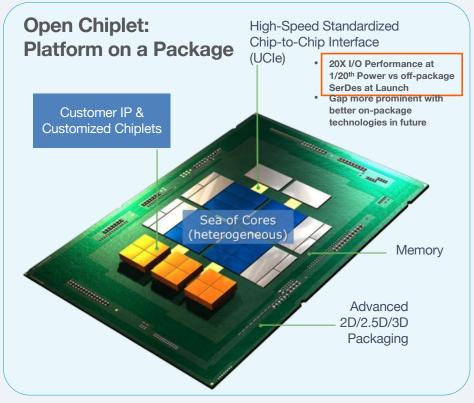

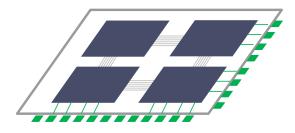

## **More Than Moore**

- Allow overcoming reticle size limitations for large devices

- Improve yield: Yield goes down exponentially with size but with tiling, it is linear

- Allow hybrid devices: Each IC in a SiP can be manufactured at a different process:

- CPU/GPU/NPU/TPU on latest CMOS technology

- DRAM on DRAM process

- Wireless/RF on Analog RF process

- Support "economies of scale" with Chiplet

- Uses the same building block multiplied according to application instead of multiple designs

### **Efficient interconnect is key for success!**

Heterogeneous Integration fueled by an Open Chiplet Ecosystem (Mix-and-match chiplets from different process nodes / fabs / companies / assembly

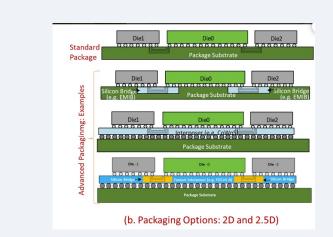

# 2.5D/3D Integration Technology Map

Substrate Technologies

|                       | SERDES (112G-<br>XSR)        | Parallel (GLink<br>2.3LL) |

|-----------------------|------------------------------|---------------------------|

| Bit Error Rate        | 1E-71E-12                    | Reliable                  |

| Power efficiency      | 1.5-2.5 pJ/bit               | 0.27 pJ/bit               |

| Beachfront efficiency | 0.6-0.7 Tbps/mm              | 2.5 Tbps/mm               |

| Area efficiency       | 0.3-0.5 Tbps/mm <sup>2</sup> | 2.1 Tbps/mm <sup>2</sup>  |

| Total power           | 150-250 W                    | 27 W                      |

| ASIC die beachfront   | 75-85 mm                     | 20 mm                     |

| ASIC die area         | 100-170 mm <sup>2</sup>      | 24 mm <sup>2</sup>        |

Silicon Interposer

CoWoS®

Organic Substrate

Serial

XSR/USR SERDES

Optimized for low pin count, long distances Complex, large area, high power

Optimized for high pin count, short distances Simple, low area, low power

#### **Parallel**

HBM2, HBM2e, HBM3

OpenHBI (-2, -3)

GLink™, AIB (Gen1, Gen2), BoW

UCle

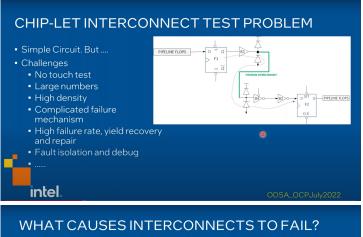

## **Industry Test Challenges Have Been Identified**

KGD, Quality and Visibility Concerns

#### **Waiting For Chiplet Standards**

902

An ecosystem is required to make chiplets a viable strategy for long-term success, and ecosystems are built around standards. Those standards are beginning to emerge today.

MARCH 25TH, 2021 - BY: BRIAN BAILEY

The need and desire for chiplets is increasing, but for most companies that shift will happen slowly until proven standards are in place.

Interoperability and compatibility depend on many layers and segments of the supply chain coming to agreement. Unfortunately, fragmented industry requirements may lead to a plethora of solutions.

Standards always have enabled increasing specialization. In the early days of the chip industry, a company had to design, implement, and fabricate everything. For most companies, fabrication became separated from design by well-defined interfaces and models, such as PDKs, BSIM models, and libraries.

https://www.youtube.com/watch?v=Am0AG6X28FQ

https://semiengineering.com/waiting-for-chiplet-standards/

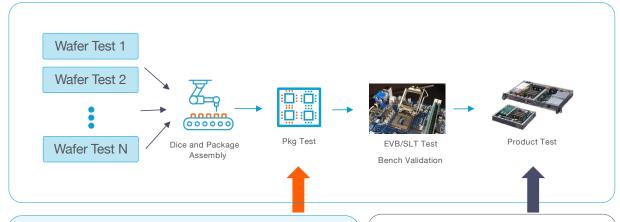

# **Testing Challenge for Chiplets**

#### System in Package (SiP)

✓ Interface available at package

#### With protean Tecs

Solution deployed at Package testing:

Provide parametric per-lane assessment Enables improved repair with deep data Test sequences 100x shorter than conventional approaches at later stage

Value in test coverage improvement:

Shift left with higher resolution testing Reduction of RMA by identifying marginal operation and latent defects

#### **Todays Problem:**

- 1000's of D2D connections no evaluated until system test

- No test access to D2D interface at SiP

- Existing test method Pass/Fail BIST with long runtime

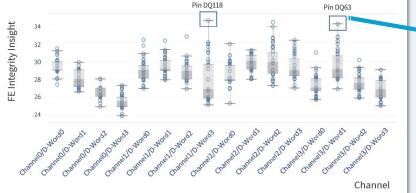

# **Enables per-lane parametric visibility**

- Comprehensive parametric lane grading

- 100% lane coverage

- Monitors the eye width and jitter

- During test and in-mission

- While the devices are at normal operation

- SW Platform solution with data analytics capabilities

- Characterization & Qualification

- HVM @ATE

- System HVM

- In mission

- Patent protected

Pass or Fail for the entire lane

Complementary to proteanTecs comprehensive chip performance and health monitoring solutions

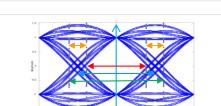

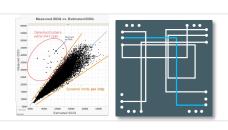

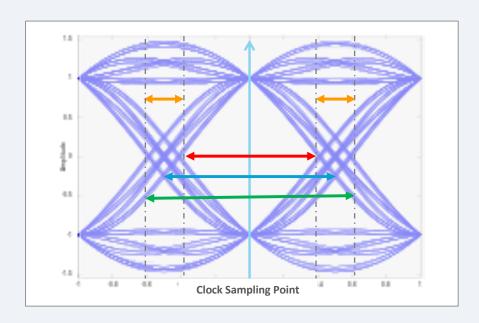

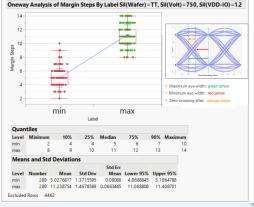

# **Parametric Lane Grading**

- Parameters of lanes are compared across the interface to determine Lane Grading

- TCA performs measurement at a single-lane level

- Measurement dynamic range and step resolution are configurable

- Combination of measured and calculated parameters

Measured Margin Setup and Hold time

Maximum Minimum Average

Calculated Eye width crossing jitter: -

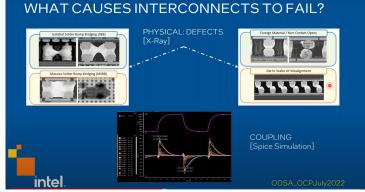

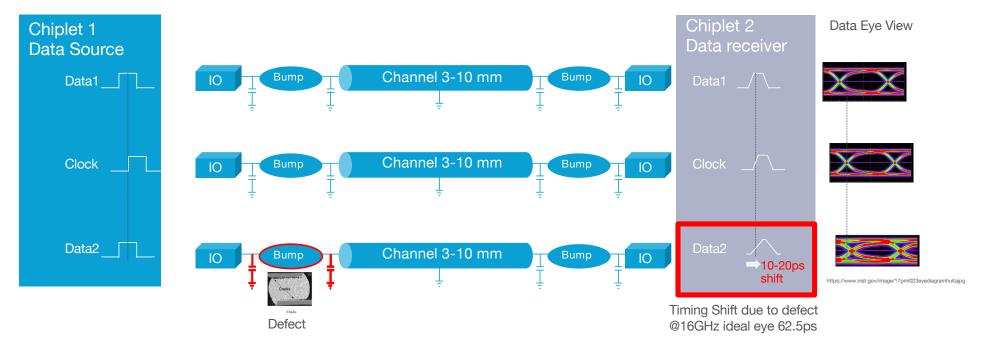

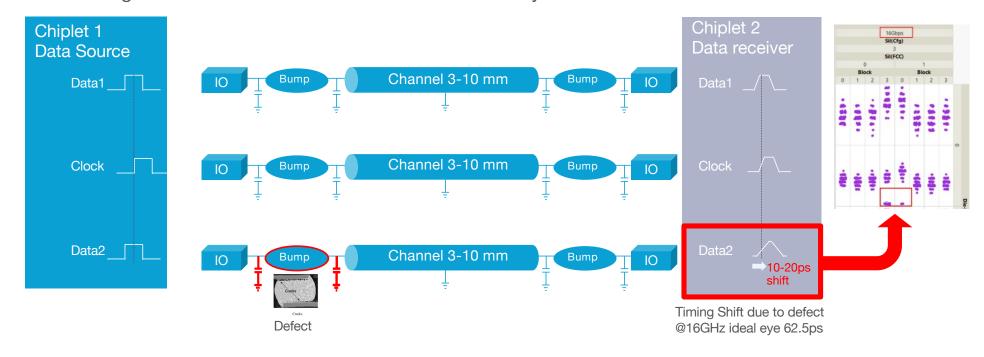

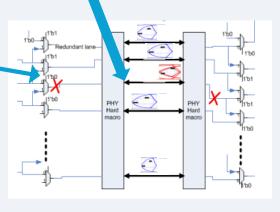

## **Latent Defect on D2D**

Example: 16 Gbps lane operation

Defect will get worse with thermal/electrical stress where eye closes further

## **Latent Defect on D2D**

Example: 16 Gbps lane operation

Defect will get worse with thermal/electrical stress where eye closes further

proteanTecs Agent + analytics enables ps level measurement and insights on device aging

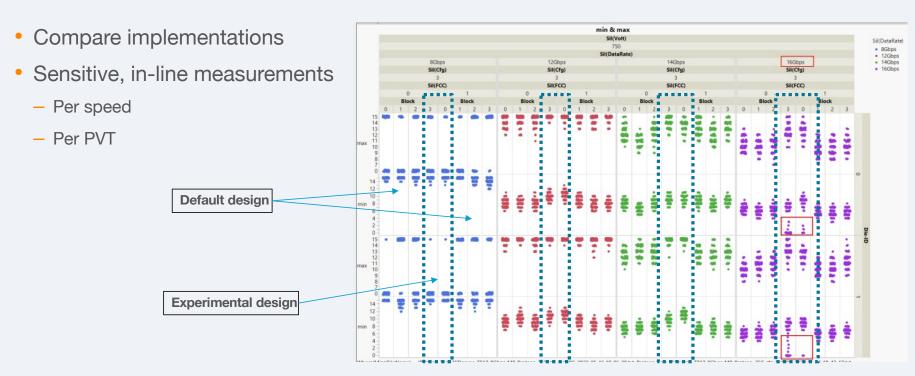

# **Characterization results: Implementation Comparison**

Design of experiment showed that "default design" had better performance at 16Gbps in red boxes

# **Deploying D2D insights into ATE**

## **ACS Solution Store – An Open Solutions Ecosystem**

- Online marketplace for applications from multiple partners

- Usable for adaptive test, outlier screening, others

- User manuals, app notes, data sheets

- More partners and applications being added continuously

http://acs.advantest.com

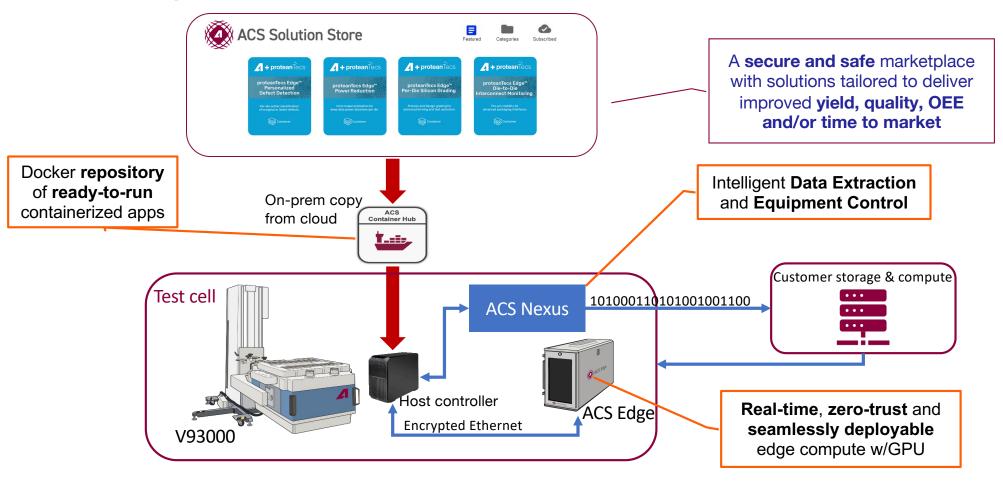

## **Deploying D2D Test Into Production on ACS Real-Time Data Infrastructure**

## **A Short List of Analytics Use Cases**

| Category                  | Use Case                                 | Benefit                   |

|---------------------------|------------------------------------------|---------------------------|

| Outlier detection         | Dynamic part average test at package     | Quality, reliability      |

|                           | Univariate, multivariate outliers        | Quality, reliability      |

| Adaptive test             | Adaptive scan-based diagnostics          | Yield                     |

|                           | Adaptive test time reduction             | Test cost, quality        |

|                           | Adaptive test flow (test or sensor data) | Test cost                 |

| Inferencing               | Shift left of tests                      | Test cost, throughput     |

|                           | Real-time predictive modeling            | Test cost, throughput     |

|                           | Stuck part detection                     | Quality, throughput       |

| Speed up test computation | RF demodulation                          | Test cost, yield, quality |

|                           | RF digital predistortion                 | Test cost, yield, quality |

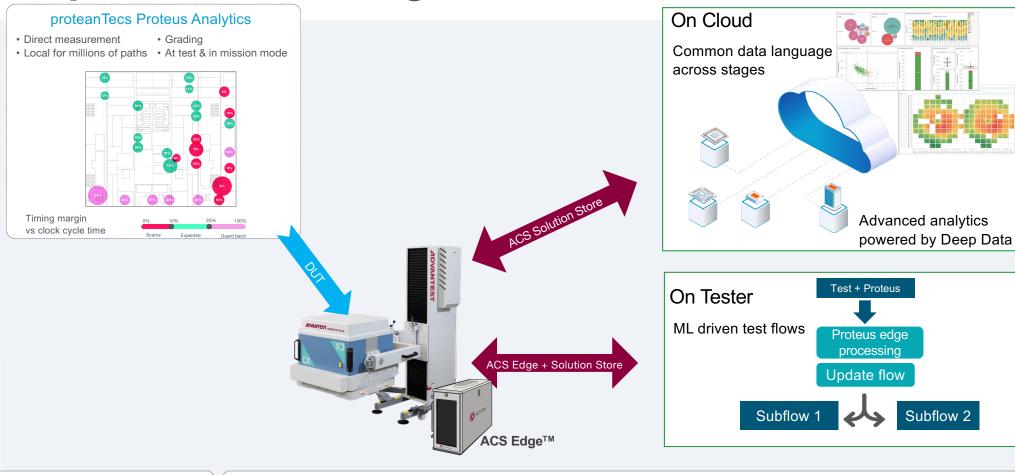

# proteanTecs Integrations with Advantest

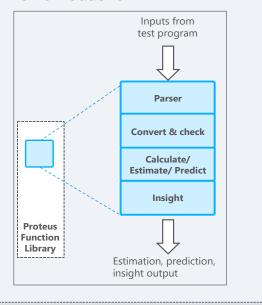

# **Containerization of proteanTecs Functions**

## Tester running Smartest

#### Data to container

Chip ID

Site ID

Agent config

Agent Data

Computation request

#### Insights from Container

Runtime information Insight generated

#### **Applications**

- Per-die silicon grading

- Personalized defect detection

- Power reduction

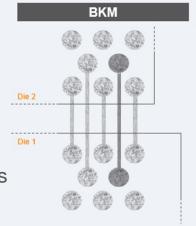

# **Deep Data Lane Repair**

Today Repair based on P/F functional test limiting visibility of robustness of repair

- Deep Data driven for parametric understanding of eye characteristics

- Enables lane shift and IO control repairs

- Diagnose fabrication and assembly faults

- Maximizes for peak operation –margin, performance, power,

# **Die-to-Die Applications Supported**

#### **Yield Learning**

- Per-lane parametric eye-width grading assessment including max, min, average and jitter

- Advanced characterization of eye parameters across manufacturing variability, speed grades, temperature and voltage

#### **High Volume Manufacturing**

- Outlier detection across lanes and pin group, across full population, reducing risk of RMAs

- Improved yield and test time by quickly and easily identifying weak lanes as candidates for spare lane swap during FT

- Improved repair algorithms for testing and aging in field

- Advanced alerts due to interconnect faults

## **Conclusions**

- Die to Die interface testing is vital for enabling System In Package applications

- Provides new level of device level visibility at Package

- Combining Agents, machine learning and analytics have enabled diagnosis of latent defects

- Additional benefit can be realized with Advantest ACS and proteanTecs Functions

## **Thank You**