# Universal Chiplet Interconnect Express $\Gamma$ (UCle $\Gamma$ )

Building an open ecosystem of chiplets for on -package innovations

# Moore Predicted "Day of Reckoning"

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected."\*

- Gordon E. Moore

<sup>&</sup>quot;Cramming more components onto integrated circuits," Electronics, Volume 38, Number 8, April 19, 1965

### Motivation

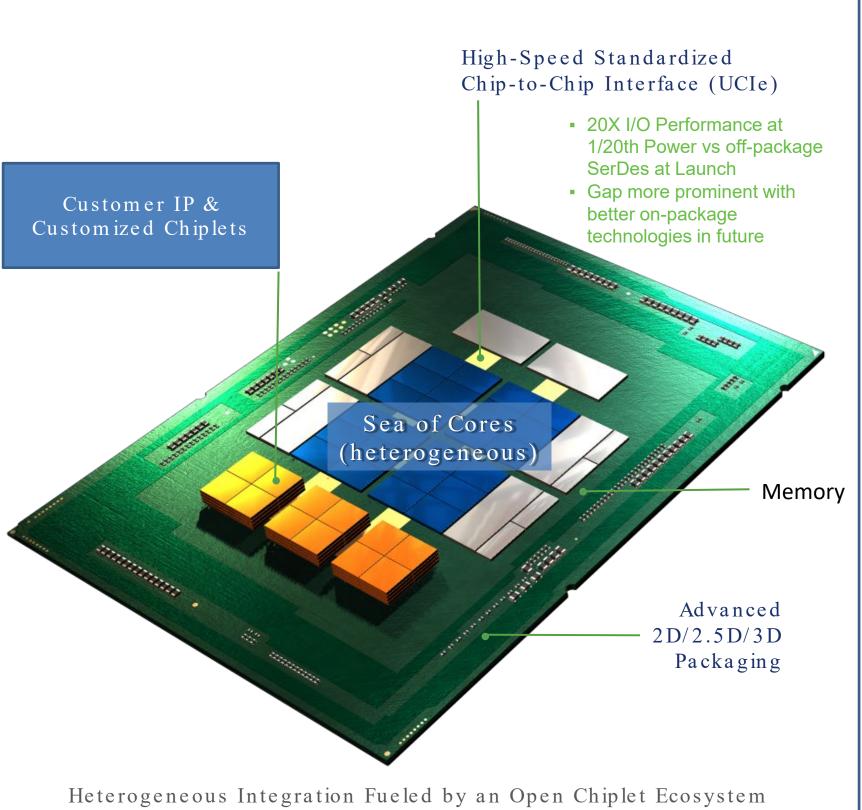

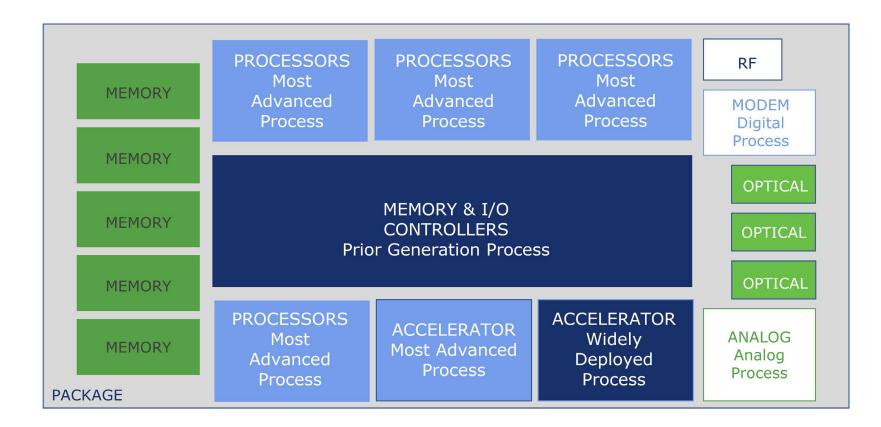

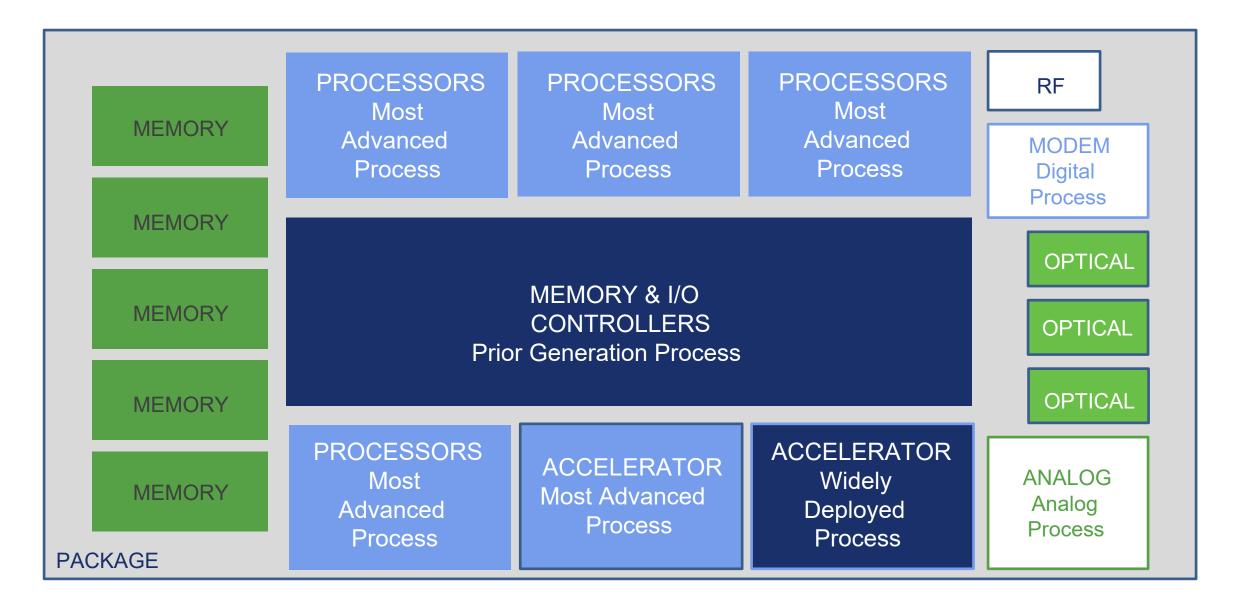

#### OPEN CHIPLET: PLATFORM ON A PACKAGE

Heterogeneous Integration Fueled by an Open Chiplet Ecosystem (Mix-and-match chiplets from different process nodes / fabs / companies / assembly)

# Align Industry around an open platform to enable chiplet based solutions

- Enables construction of SoCs that exceed maximum reticle size

- Package becomes new System-on-a-Chip (SoC) with same dies (Scale Up)

- Reduces time-to-solution (e.g., enables die reuse)

- Lowers portfolio cost (product & project)

- Enables optimal process technologies

- Smaller (better yield)

- Reduces IP porting costs

- Lowers product SKU cost

- Enables a customizable, standard-based product for specific use cases (bespoke solutions)

- Scales innovation (manufacturing and process locked IPs)

# Key Metrics and Adoption Criteria

#### **Key Performance Indicators**

- Bandwidth density (linear & area)

- Data Rate & Bump Pitch

- Energy Efficiency (pJ/b)

- Scalable energy consumption

- Low idle power (entry/exit time)

- Latency (end-to-end: Tx+Rx)

- Channel Reach

- Technology, frequency, & BER

- Reliability & Availability

- Cost

- Standard vs advanced packaging

# UCle - Architected and specified from the ground - up to deliver the best KPIs while meeting wide adoption criteria

#### Factors Affecting Wide Adoption

- Interoperability

- Full-stack, plug-and-play with existing s/w is+

- Different usages/segments

- Technology

- Across process nodes & packaging options

- Power delivery & cooling

- Repair strategy (failure/yield improvement)

- Debug controllability & observability

- Broad industry support / Open ecosystem

- Learnings from other standards efforts

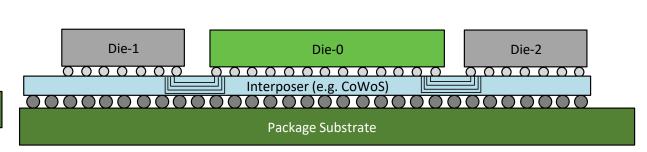

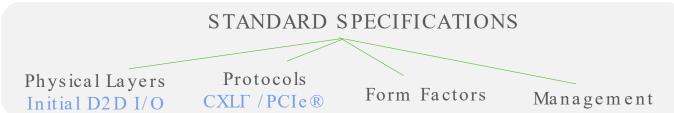

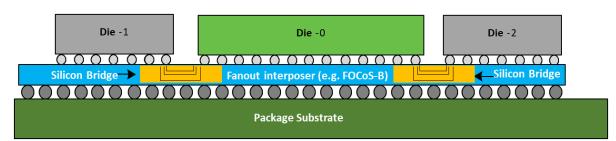

### Jumpstarting UCle Intel donates initial specification

- Focus of UCle 1.0 Specification

- Physical Layer: Die-to-Die I/O with industry-leading KPIs

- Protocol: CXL\(\Gamma\) / PCIe\(\mathbb{R}\) for near term volume attach

- SoC construction issues are addressed since CXL/PCIe is a board-toboard interface

- CXL/PCIe addresses common use cases

- I/O attach with PCIe/CXL.io

- Memory use cases: CXL.mem

- Accelerator use cases: CXL.cache

- Well defined specification : ensure interoperability and future evolution

- Future: the chiplet journey is just starting!!

Die-2

(e.g. EMIB)

- Other protocols

- Advanced Chiplet form-factors (e.g., 3D)

- Chiplet management

Die-0

Package Substrate

• More to come ....

#### PROTOCOL LAYER

DIE-TO-DIE ADAPTER

Die-1

ARB/MUX (when applicable) CRC/RETRY (when applicable) LINK STATE MANAGEMENT PARAMETER NEGOTIATION

#### RAW D2D INTERFACE (RDI)

LINK TRAINING LANE REPAIR (when applicable) LANE REVERSAL (when applicable) PHYSICAL LAYER SCRAMBLING/DE-SCRAMBLING (opt-in) SIDEBAND TRAINING & TRANSFERS ANALOG FRONT END **CLOCK FORWARD**

Package Substrate

(Standard Package)

(Different flavors of packaging options supported to build an open ecosystem)

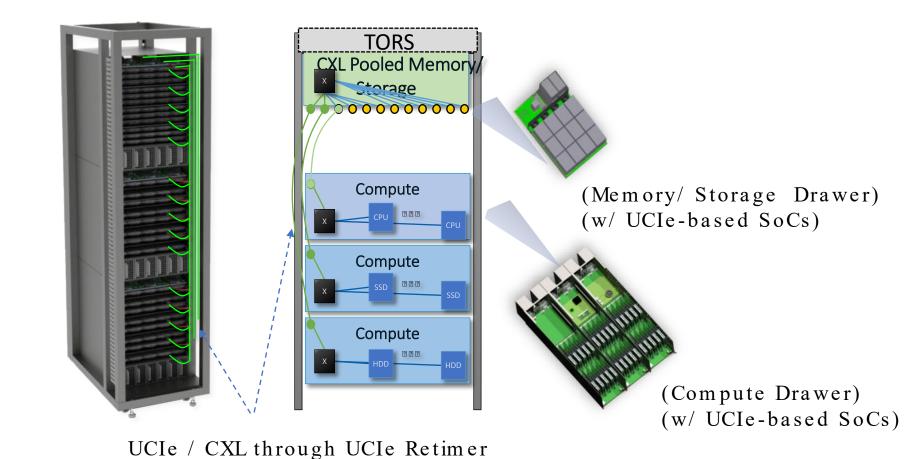

### Usage Models Supported by UCIe

SoC Package level construction for wide range of usages from Hand -held to high -end servers

✓ Mix and match dies from multiple sources with different packaging options

Provision to extend off-package with UCIe Retimers connecting to other media (e.g., optics, electrical cable, mm Wave)

UCIe 1.0 delivers the best KPIs while meeting the projected needs for the next 5-6 years. Wide industry leader adoption spanning semiconductor, manufacturing, assembly, & cloud segments.

## UCIe 1.0: Characteristics and Key Metrics

| CHARACTERISTICS      | STANDARD<br>PACKAGE  | ADVANCED<br>PACKAGE | COMMENTS                                                                |

|----------------------|----------------------|---------------------|-------------------------------------------------------------------------|

| Data Rate (GT/s)     | 4, 8, 12, 16, 24, 32 |                     | Lower speeds must be supported -interop (e.g., 4, 8, 12 for 12G device) |

| Width (each cluster) | 16                   | 64                  | Width degradation in Standard, spare lanes in Advanced                  |

| Bump Pitch (um)      | 100 - 130            | 25 - 55             | Interoperate across bump pitches in each package type across nodes      |

| Channel Reach (mm)   | <= 25                | <=2                 |                                                                         |

| KPIs / TARGET FOR<br>KEY METRICS    | STANDARD<br>PACKAGE                                                        | ADVANCED<br>PACKAGE | COMMENTS                                                                                 |

|-------------------------------------|----------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------|

| B/W Shoreline (GB/s/mm)             | 28 - 224                                                                   | 165 - 1317          | Conservatively estimated: AP: 45u; Standard: 110u; Proportionate to data rate (4G - 32G) |

| B/W Density (GB/s/mm <sup>2</sup> ) | 22-125                                                                     | 188-1350            |                                                                                          |

| Power Efficiency target (pJ/b)      | 0.5                                                                        | 0.25                |                                                                                          |

| Low-power entry/exit latency        | $0.5 \mathrm{ns} <= 16 \mathrm{G}, \ 0.5 - 1 \mathrm{ns} >= 24 \mathrm{G}$ |                     | Power savings estimated at >= 85%                                                        |

| Latency (Tx + Rx)                   | < 2 n s                                                                    |                     | Includes D2D Adapter and PHY (FDI to bump and back)                                      |

| Reliability (FIT)                   | 0 < FIT (Failure I                                                         | n Tim e) << 1       | FIT: # failures in a billion hours (expecting ~1E-10) w/ UCIe Flit Mode                  |

# Organizational Update

#### UCIe Consortium is now incorporated!

- 100+ member companies

- 6 working groups working on evolving technology

- Intellectual Property Rights (IPR)

protection is in place for members.

- Members include:

- Adopters: Companies interested in building products

- Contributors: Companies invested in helping to define future standards (working group participants)

- Promoters: Board of Directors and leadership

## Board Members

Leaders in semiconductors, packaging, IP suppliers, foundries, and cloud service providers are joining together to drive

The open chiplet ecosystem.

JOIN US!

Meta

### Summary

- Leaders in semiconductors, packaging, IP suppliers, foundries, and cloud service providers join forces to launch new Universal Chiplet Interconnect Express (UCle) technology to standardize the chiplet ecosystem today and future generations of chiplet technology.

- UCle 1.0 Specification ratified to provide a complete standardized die-to-die interconnect with physical layer, protocol stack, software model, and compliance testing that will enable end users to easily mix and match chiplet components from a multi-vendor ecosystem for System-on-Chip (SoC) construction, including customized SoC.

- New open standard establishes an open chiplet ecosystem and ubiquitous interconnect at the package level.

- Interested companies and institutions are encouraged to join. Learn more, including how to join: <a href="www.UCIexpress.org">www.UCIexpress.org</a>

# Thank You

www.UClexpress.org

# Backup Content

# Heterogeneous Integration and Open Chiplet Ecosystem

SoCs will consist of chiplets designed, manufactured and assembled by various companies.

Heterogeneous chiplet integration is the future of the semiconductor industry.