# High-throughput Printing of Micro and Nanoscale Interconnects, and Passive and Active Electronics Elements for Heterogeneous Integration and Advanced Packaging Applications

Ahmed Busnaina, PhD

Chief Technology Officer

Nano OPS, Inc.

www.nano-ops.net

# Outline

- > Introduction

- How does it work?

- Nanoscale Directed Assembly-based Processes

- > Electrophoretic Assembly

- Fast fluidic Assembly

- Crystalline and single crystal printing of metals and semiconductors

- Applications (Interconnects, Transistors, Diodes, display, Sensors)

- Scalable and fully automated Fab-in-a-Tool

- Summary

### Only Large Companies Can Wake Nahoscale Electronics

Can you input your design and materials on one end and have your electronics come out the other end on the same day using one machine?

> Can the cost be 10-100 times less than conventional fabrication?

> Can any small or mid size company can make their own chips on the same day?

## Yes!

# IMAPS 18th International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA HOW COES IT WORK

Nature uses bottom-up selfassembly, molecule by molecule, cell by cell.

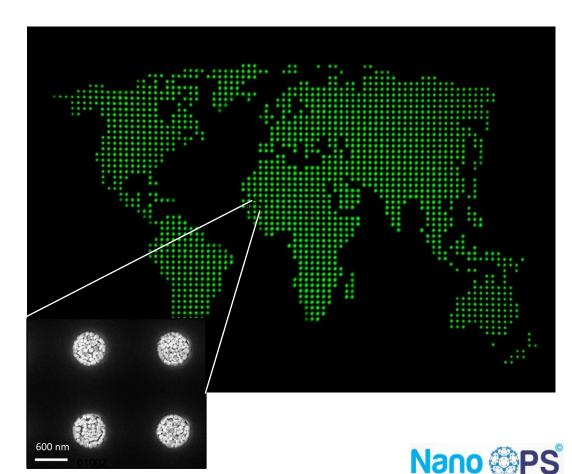

We directly assemble each nanoparticle to print a circuit pattern.

#### **Directed assembly-based printing**

#### The New Future of Electronics Wanufacturing is Here

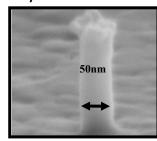

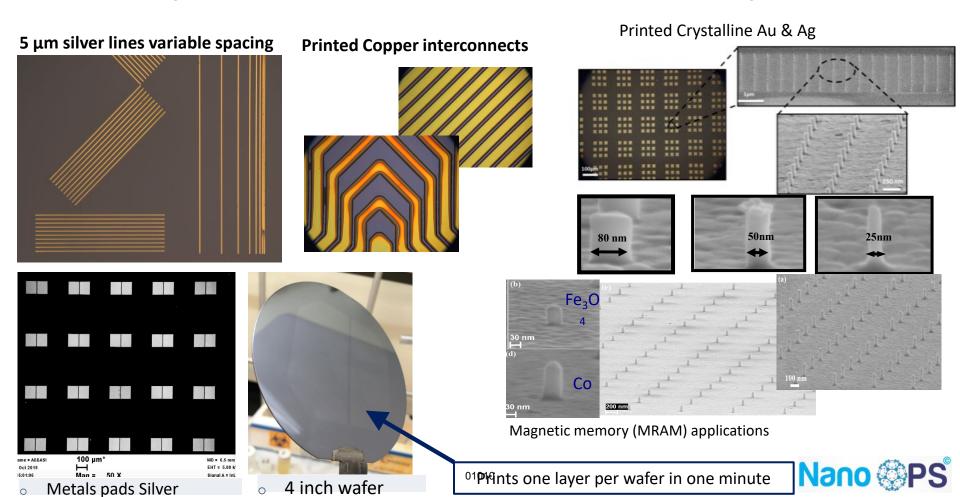

- Feature size down to 25nm

- > 10 100 times reduction in cost;

- 10 100 times faster;

- 1000 times reduction in materials use;

- Eliminates 100s of process steps;

- ➤ 1000 times faster than inkjet or 3D printing;

- Prints crystalline metal and semiconducting structures

# The Big Chasm in Manufacturing of Electronics

Microscale, low cost, and low throughput

Nanoscale, low cost and high throughput

Nanoscale, high cost, and high throughput

Additive Manufacturing of Electronics (Conventional Printed Electronics)

Inkjet and screen printing industry

Nanoscale Additive Manufacturing of electronics

Nano OPS, Inc.

Nanoscale Conventional Semiconductor Fabrication

Semiconductor Equipment industry

01004

#### **Electronics Manufacturing Landscape**

#### Microscale

- ✓ Low end & low throughput

- ✓ Low cost

#### Micro & Nanoscale

- ✓ High end & high throughput

- ✓ Low cost

#### Micro & Nanoscale

- √ high-end & high throughput

- ✓ High cost

Nano OPS, Inc.

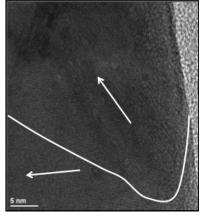

## Process and Printed Circuit Structures

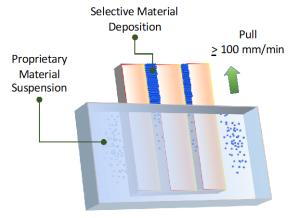

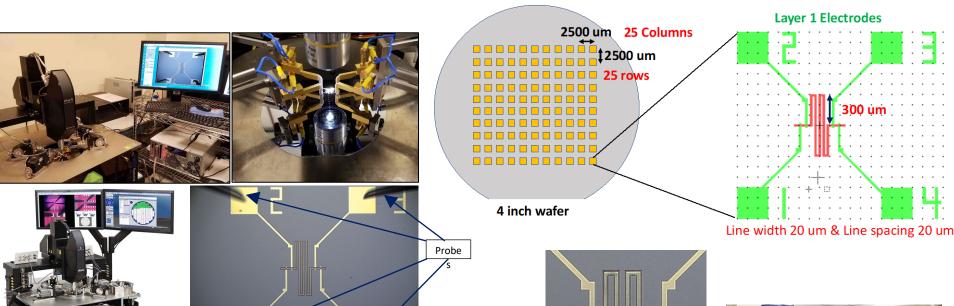

# Electrophoretic Directed Assembly Printing Process – EPx Platform

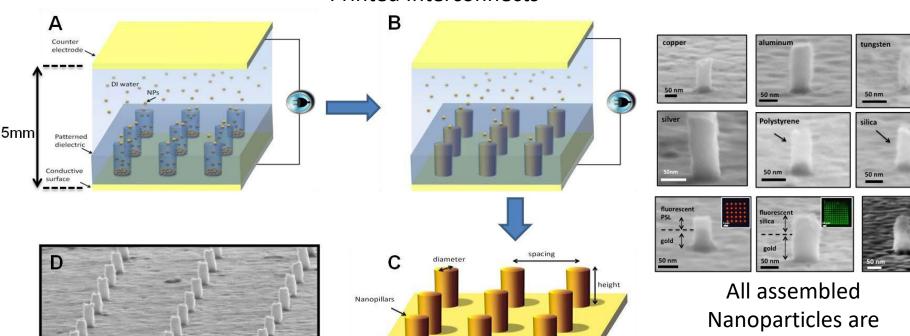

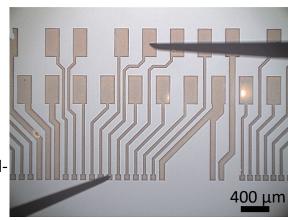

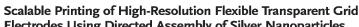

#### **Printed Interconnects**

ACS Nanopol (5), 2014.

completely fused insitu.

### IMAPS 18th Intended to proceed the Catalogue of the Catal

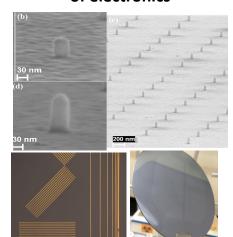

Probe 200 nm

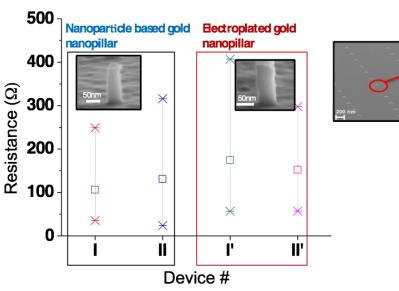

Resistance of assembled interconnects is the same as bulk (electroplated interconnects).

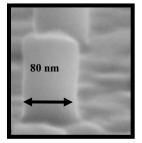

Crystalline Au Pillars

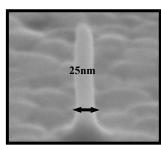

Directly assembled structures properties are equivalent to electroplating, CVD and PVD fabrication.

Directly assembled metallic structures (Cu, Ag, Al, Au, and W, etc.) in addition to semiconductors and dielectrics were demonstrated.

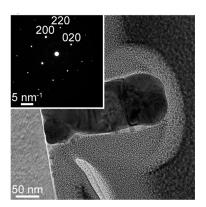

- ➤ TEM shows that NPs completely fuse without any voids.

- Nanopillars have polycrystalline nature.

ACS Nanopole (5), 2014.

### Fasta Finite Assembly Aprocess 10.20 F Fxta Platform

**Fast Fluidic Process**

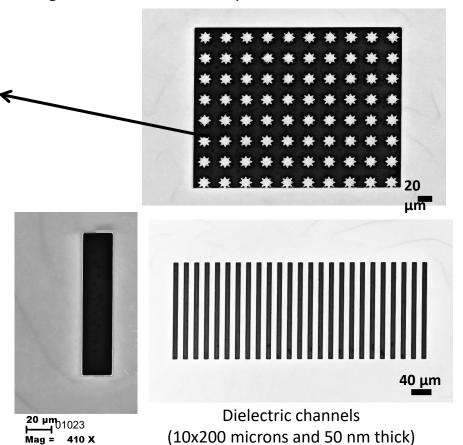

SiO<sub>2</sub> substrate – 10 μm spacing

**Versatile Process**

### Print any Material at the Nano or Wicro Scale on any Substrate

#### Printing of Single Printing of S

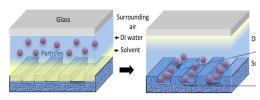

# Convective Interfacial Assembly

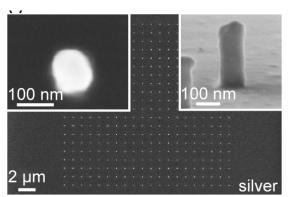

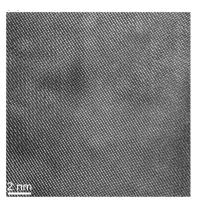

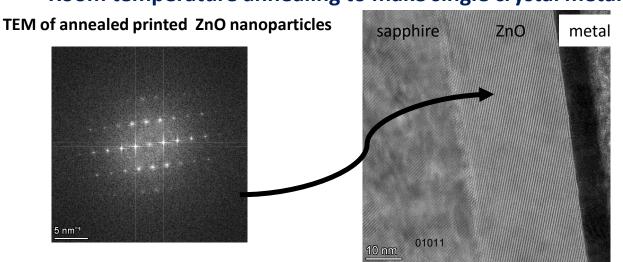

#### Room temperature annealing to make single crystal metal (Ag) nano structures

RTP annealing of II-VI nanoparticles on sapphire gives a single crystal structure throughout.

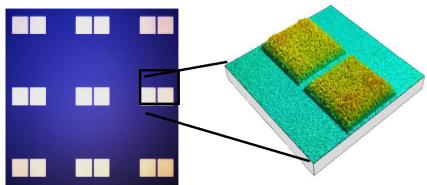

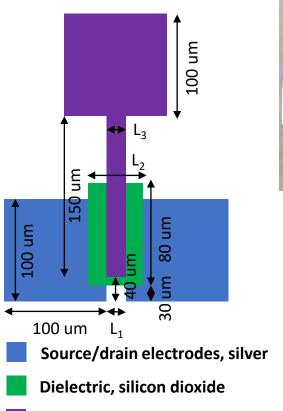

### Printed Three Aligned Layers on Silicon Wafers

Gate electrode, silver

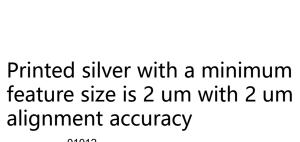

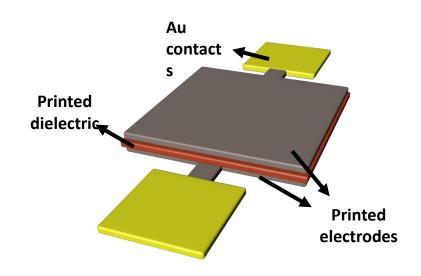

### Electrophoretic Assembly (EPx Platform) for Flexible Electronics

- **►** Additive

- > High throughput

- Prints down to 20nm

- Room temperature and pressure

- Prints on flexible or hard substrates

- ➤ Multi-scale; nano to macro

- Material independent

- Very low energy consumption

- > Very low capital investment

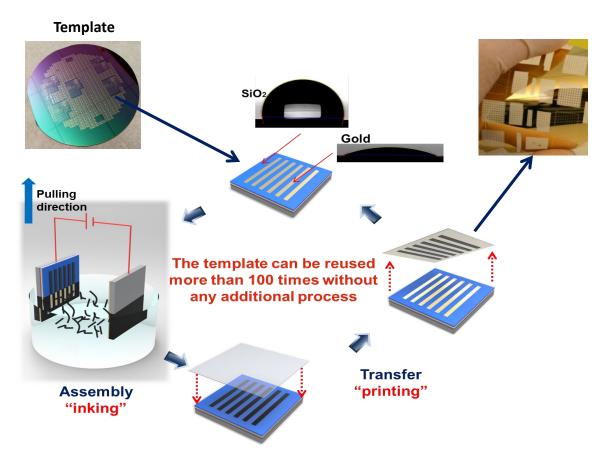

### Printed Two aligned tayers on Flexible Substrates (Polyurethane)

Aligned metal (silver) light color and polymer (dark color) on Polyurethane minimum feature size is 5 um with 2 um alignment accuracy

# Applications

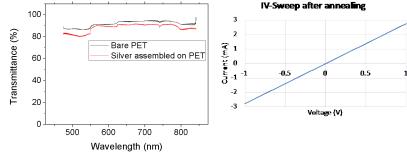

### The Resistivity of Printed Metal cutines (Silver)

01016

- Resistivity measurements of 3,125 printed patterns over five different substrates.

- ➤ It shows that the resistivity is about 2X of the bulk resistivity.

Nano @PS

### IMAPS 18th International Professor To PACKAGIN VI are 1323 | Fountain Hills, AZ USA

> Different materials has been optimized and printed on flexible and rigid substrates on large scale:

Platinum metal printing

Source: nanoComposix (Aqueous based Pt ink)

Gold metal printing

Source: nanoComposix (Aqueous based Au ink)

Copper metal printing

Source:

Novacentrix

(Organic based Cuink)

Silver metal printing

Source:

Novacentrix

(Diethylene glycolbased Ag ink)

01017

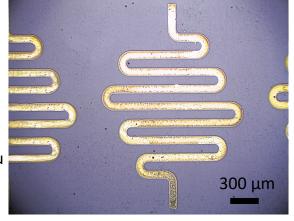

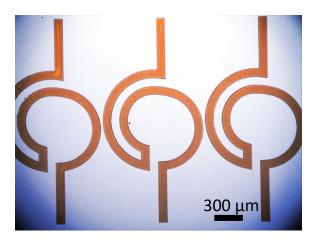

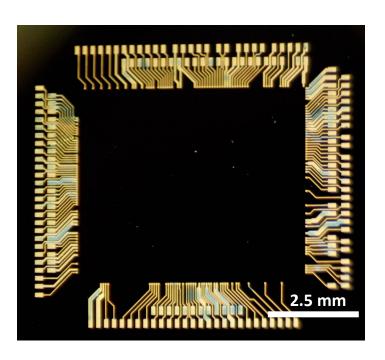

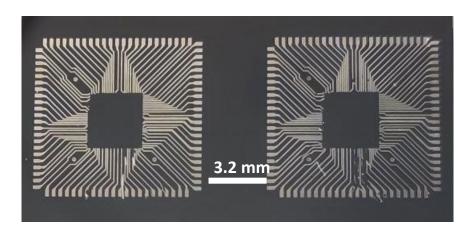

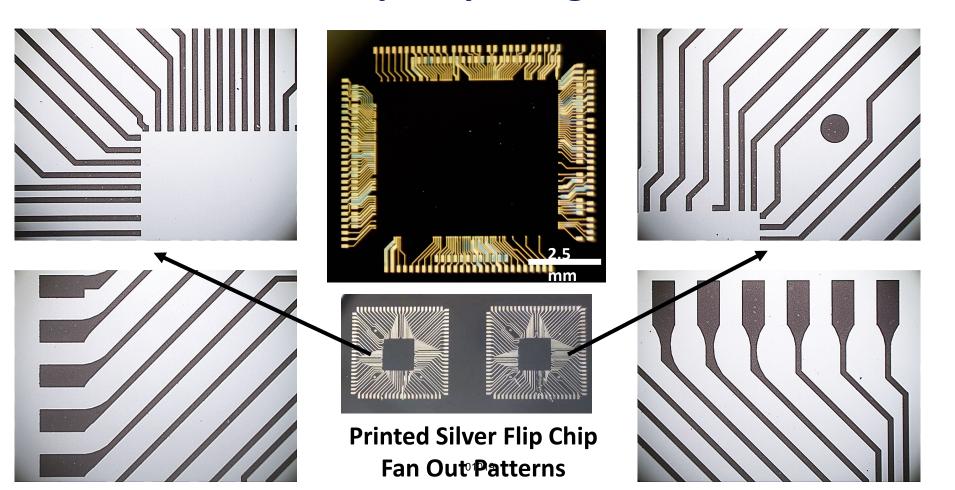

# Photo Martage of Flip Achip Fan Out Pattern

#### **Printed Silver Flip Chip Fan Out Patterns**

# IMAPS 18th International Conference on DEVICE PASKASING LMarch 740 2023 Fountain Hills, AZ USA

### IMAPS 18th International Conference on DEVICE PACKAGING March 7-10, 2022 | Fountain Hills, AZ USA

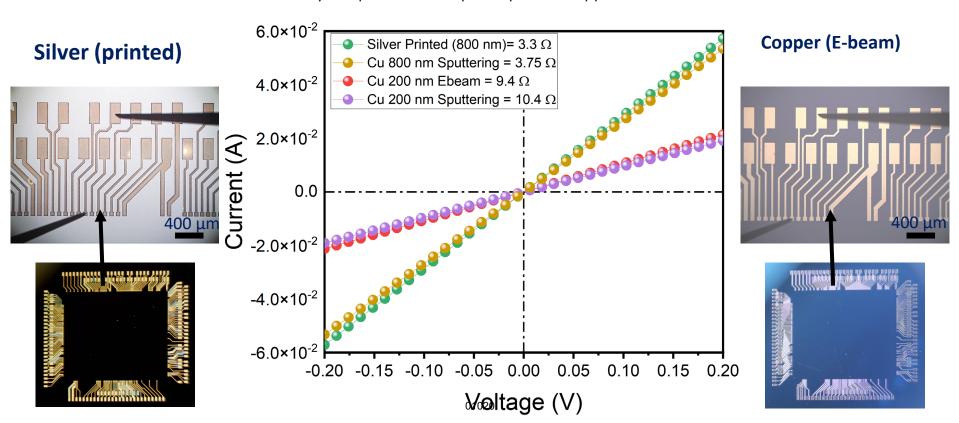

- > The Flip chip pattern was printed using silver.

- > The tracks conductivity is equivalent to vapor deposited copper at the same thickness.

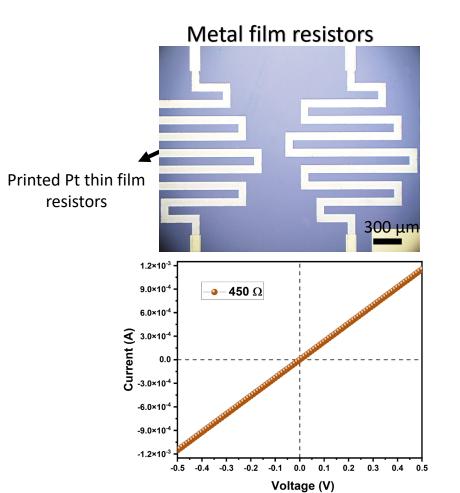

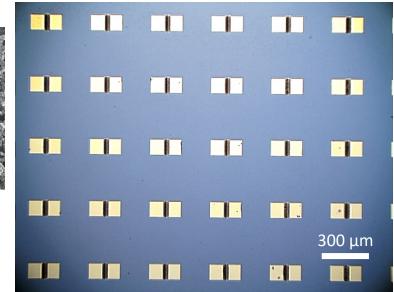

### Dewices Characterization: Resistors

#### Metal film resistors

### IMAPS 18th International Confedence on DEVICE PACKAGING March 7 19 2022 Fountein Hills, AZ USA

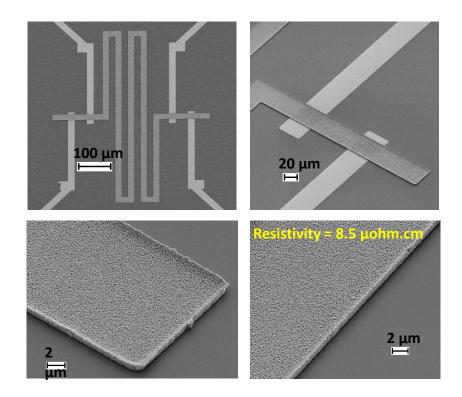

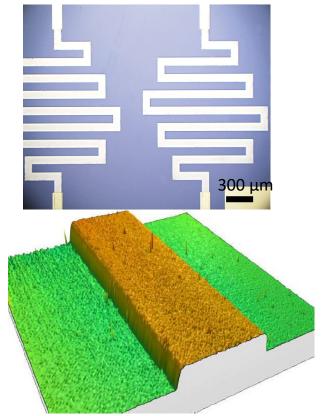

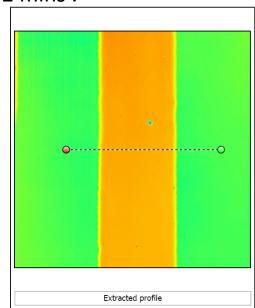

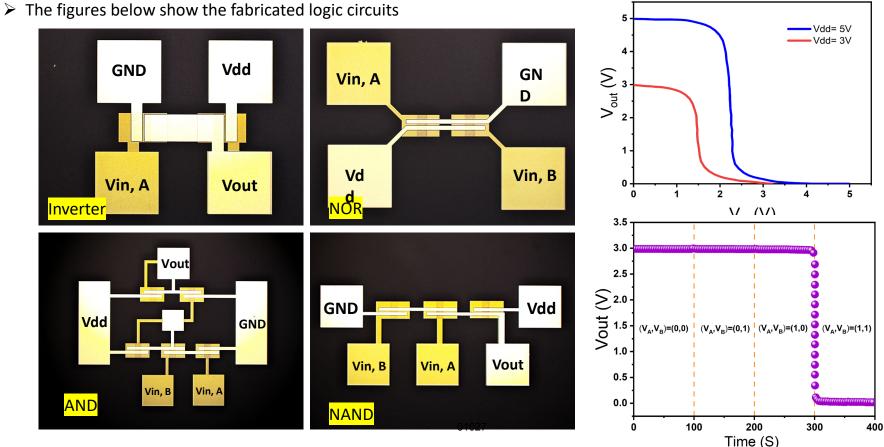

➤ Confocal microscope measurements show an average thickness of 250 nm after annealing using RTP at 800 °C for 2 mins .

The printed pattern shows uniform and homogeneous surface morphology.

## IMAPS 18th Internalisma Conference on BEVICE FACHAGING March 7-10-2022 Fountain Hills, AZ USA

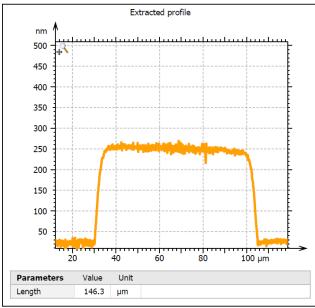

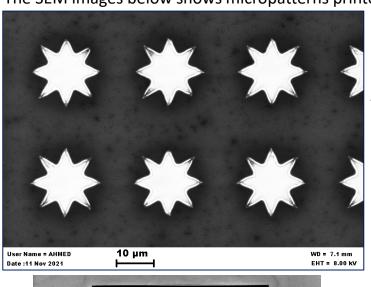

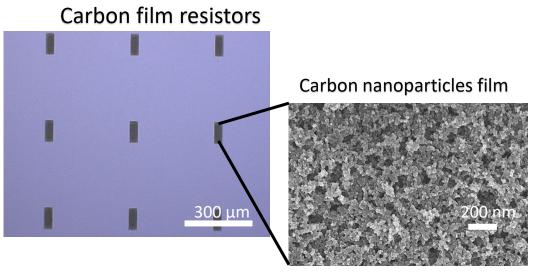

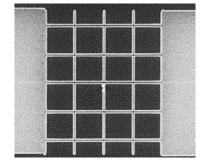

> The SEM images below shows micropatterns printed using directed fluidic assembly.

### IMAPS 18th International Conference on DEVICE PACKICHNG March 110, 2020 Fountain Hills, AZ USA

Carbon film resistors after

Au contact

10 K Ohm Printed Carbon thin film resistors (40x100 microns and 0.3 micron thick)

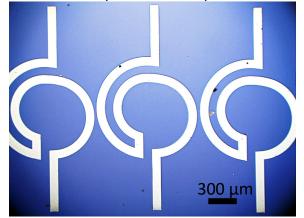

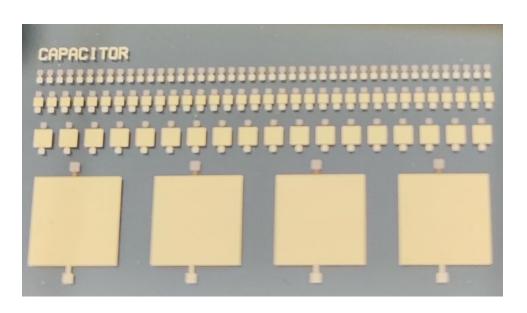

### IMAPS 18th International Conference on DEVICE PACKAGING | March 7-10, 2022 | Fountain Hills, AZ USA Printing of Capacitors

> The optical image below shows the printed capacitor after Printing.

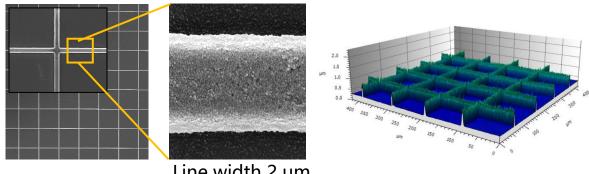

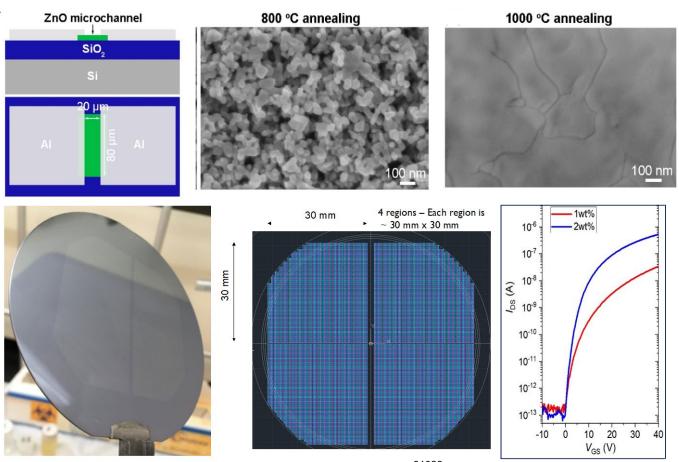

### Printed Touch Screen with High Fidelity at the Witte and Nanoscale

#### Printed Ag grids for touch display applications

Line width 2 um

Line width 300 nm

#### COMMUNICATION

Transparent Electrodes

**Electrodes Using Directed Assembly of Silver Nanoparticles**

**Excellent Line edge roughness** 3.7 nm **Using large nanoparticles**

Salman A. Abbasi, Zhimin Chai, and Ahmed Bushand\*

### IMAPS 18th International Conference on BENCE PAC AGING MORTA 7,10, 2022 Fountain Hills, AZ USA

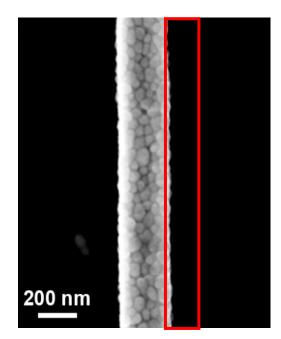

➤ Logic gates such as Inverters, AND, NAND, and NOR were fabricated based on SWCNTs FETs

Euglic gates such as inverters, AND, NAND, and NON were labricated based on Swen

### Field Effect Transistor (FETS) Using 11-1/1 Semiconductors

Wafer level printing of 37,000 transistors exhibiting an on/off ratio higher than 10<sup>6</sup> after annealing.

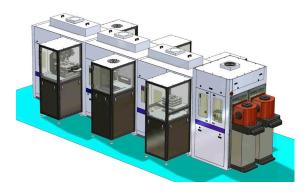

#### Scalable Fully - automated Fab - Fn-a-Tool

- ➤ Nano OPS has licensed exclusive rights to 35 inventions.

- ➤ Nano OPS is introducing two fully-automated a Fab-in-a-Tool platforms:

- > FLEX RD: designed to print flexible electronics at sub-micron scale.

- FFx RD800: Can take a CAD file and deliver a completed product at sub-micron scale.

- Turnkey device fabrication incorporating transistors, inverters, capacitors, diodes, inductors, photonic devices, and sensors for IoT, 5G, wearables, etc.

- ➤ Secure (trusted) foundry service for feasibility studies and production (from zero trust to full trust).

Fab-in-a-Tool

### The Future of Electronics Manufacturing

Any Material

Any Substrate

Minimum Feature Size 20 nm

High throughput 10 – 100x Faster

**Cheaper 10 – 100x**

#### Fab-in-a-Tool: A Fully Automated Nanoscale Electronics Manufacturing Platform

01030

### The Future of Electronics Manufacturing

#### **Fab-in-a-Tool Platform Advantage:**

- ✓ Feature size comparable to advanced electronics manufacturing technology at 20nm.

- ✓ 5 10x reduction in capital equipment cost as compared to current factories;

- ✓ 10 100x reduction in manufacturing cost compared to current technology;

- ✓ 10 100x faster as compared with current technology;

- √ 1000x reduction in materials use compared to current technology;

- ✓ More than 1000x faster than inkjet or 3D printing;

- ✓ Prints crystalline metal and semiconducting structures at room temperatures.

- √ eliminating 100s of process steps;

- ✓ expanding material choices for specific design needs.

- ✓ Patented technology for printing nanometers to several hundred microns.

- ✓ From zero trust to full trust.