#### High-density Fan-Out Chip on Substrate using M-Series™ and Adaptive Patterning® Technology

Robin Davis, Director of Business Development at Deca Benedict San Jose, Principal Materials, Process & Integration Engineer at Deca John Hunt, Senior Director of Engineering, Marketing & Technical Promotion at ASE Chia-Pin Chen, ASE Bumping Engineering – New Product Development Group Senior Department Manager at ASE

### Agenda

- Introduction

- Industry Perspective

- Challenges & Solutions

- Design Study

- Conclusion

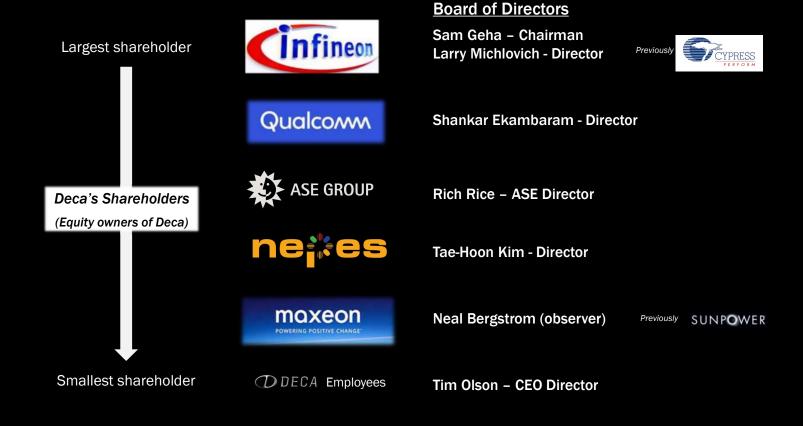

### **DECA** Company introduction

- Deca was born of a passion to transform electronic interconnect with inspiration from SunPower's advanced solar wafer fab

- Our name describes our culture of 10X thinking, inspired by Greek déka (δέκα)

- Deca created 10X breakthroughs with M-Series<sup>™</sup> & Adaptive Patterning<sup>®</sup>

SUNPOWER

Now the industry's #1 fan-out technology

Over 3.5 million devices shipping per day in Q1'22

Note: Deca holds > 100 issued and pending patents on M-Series, Adaptive Patterning and related technology

## Agenda

- Introduction

- Industry Perspective

- Challenges & Solutions

- Design Study

- Conclusion

The future is now...

"...Ponte Vecchio Xe-HPC GPU, Over 100 Billion Transistors & 47 XPU Compute Tiles"

Intel's Ponte Vecchio

"AMD Radeon... with Chiplet Design"

AMD's Radeon

Chiplets are happening

Deca released for IMAPS DPC 2022

00105

## Agenda

- Introduction

- Industry Perspective

- Challenges & Solutions

- Design Study

- Conclusion

## Challenge - Pitch Limitations

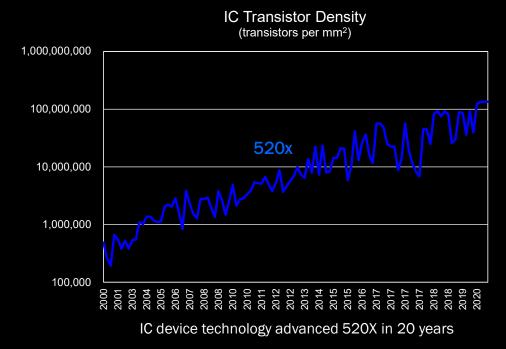

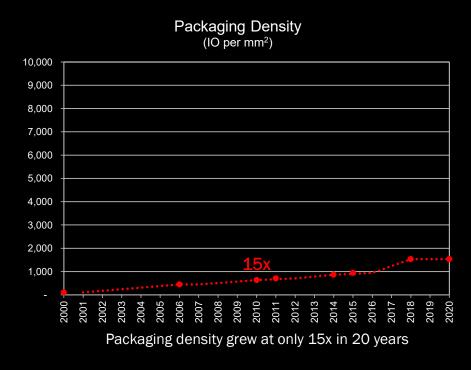

Packaging severely lagging semiconductor device technology (15x vs. 500x density increase in past 20 years)

Source: Multiple industry sources compiled at en.wikipedia.org/wiki/Transistor\_Count

Sources: 1. Chip scale Review: March-April 2020, IO/mm<sup>2</sup> derived from die pad pitch data 2. Tech Search Intl, Advanced Packaging Update, Vol 2, 2020

Packaging interface density orders of magnitude behind ICs

### **Challenge - Pitch Limitations**

Industry leaders at 40µm to 45µm die pad pitch

TSMC InFO-R M-Series Gen 1 Intel EMIB (Chips First Fan-out) (Chips First Fan-out) (Hybrid chips in substrate) Die pad pitch: 40 µm Die pad pitch: 45 µm Die pad pitch: 45 µm\* IO per mm<sup>2</sup>: 10 per mm<sup>2</sup>: 10 per mm<sup>2</sup>: \*40µm pitch reference; Tom Dillinger, Introduced in 2016 \*45µm pitch reference: David Schor, Intel Unveils SemiWiki.com, Highlights of the TSMC Foveros Omni And Foveros Direct; Leveraging Technology Symposium, 9/7/2020 Hybrid Bonding, WikiChip Fuse, July 26, 2021

density

Die pad pitch: 20 µm

Deca's Gen 2 delivers breakthrough 20µm die pad pitch thru Adaptive Patterning

2,518

IO per mm<sup>2</sup>:

M-Series Gen 2

(Chips First Fan-out)

5X interface density increase

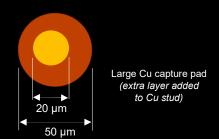

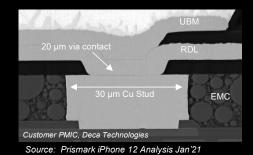

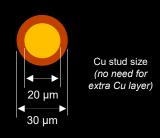

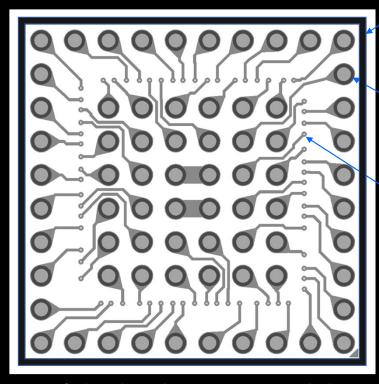

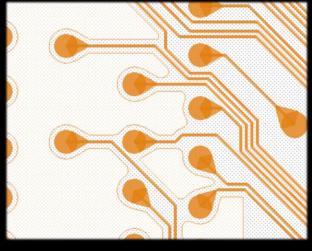

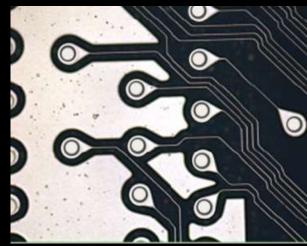

### Solution - Eliminating the Capture Pad

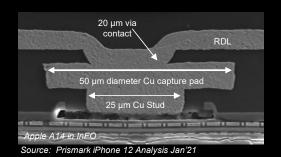

#### **Example – TSMC InFO**

Via connection without Adaptive Patterning

#### M-Series™ with Adaptive Patterning

Via connection with Adaptive Patterning

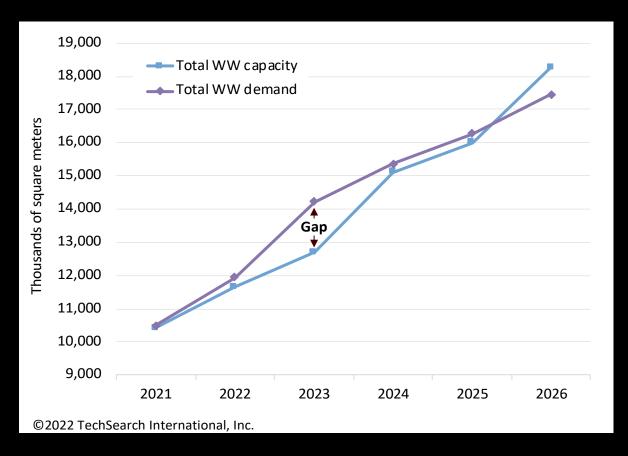

### Obstacles - Substrate availability

Significant shortfall in advanced substrate capacity is forecasted to persist

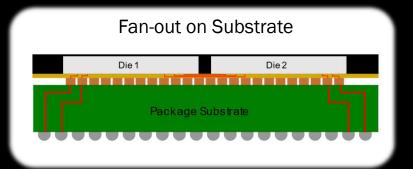

## Solution – Simpler Substrates

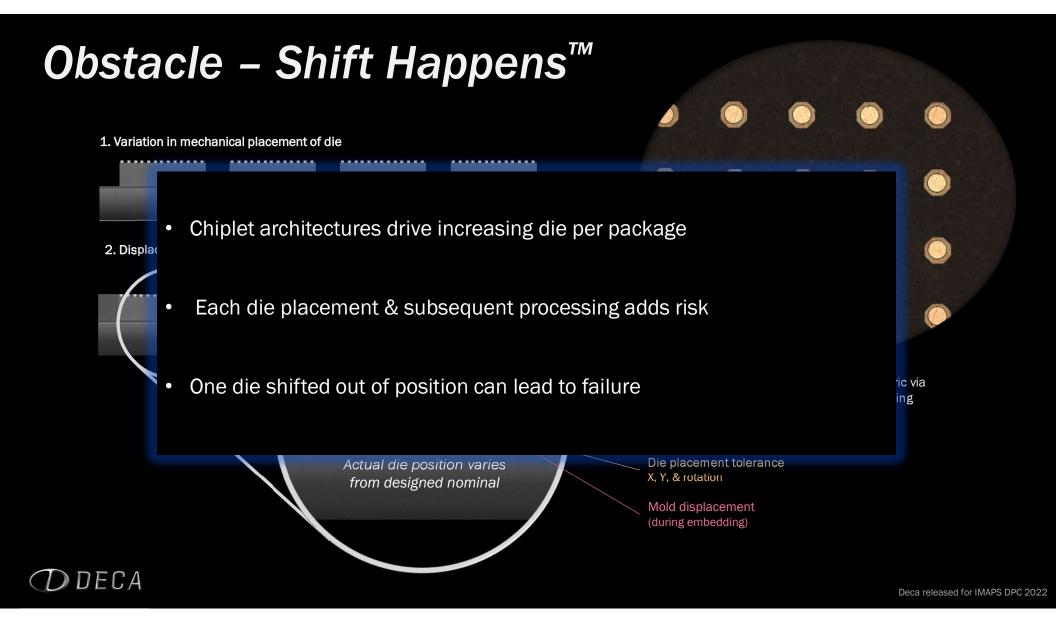

## Adaptive Patterning Methods™

#### **Adaptive Alignment**

Translate & rotate entire RDL pattern to the measured die position

#### **Adaptive Routing**

Dynamically adapt small portion of RDL to the measured die position (s)

RDL pattern moving per unit for precision alignment

Fixed package outline

Fixed UBM & solder balls

BGA array fixed to package outline – precise RDL pattern to die alignment

BGA array fixed to package outline – ideal for multi-die routing

Note: Multiple patents issued & pending covering all facets of Adaptive Patterning

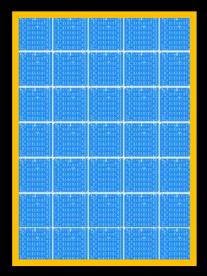

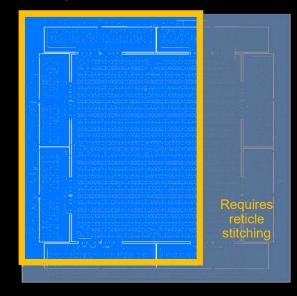

#### **Obstacles - Reticle Size**

- Reticle limits typically ~850mm<sup>2</sup>

- Chiplet based devices often 36mm x 36mm (1,296mm²) and larger

- Reticle stitching required technically feasible, commercially unattractive

5x5 mm Device

Devices within reticle

36x36 mm Device

Beyond reticle size

#### Solution - Eliminate the Reticle

Mask-less LDI lithography system

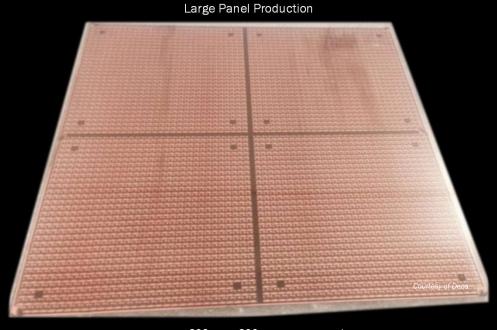

600mm x 600mm square panel

Adaptive Patterning utilizes fully digital lithography - no glass photomasks are used

Entire 300mm round or 600mm square panel is a single exposure field

#### **Obstacles - Cost**

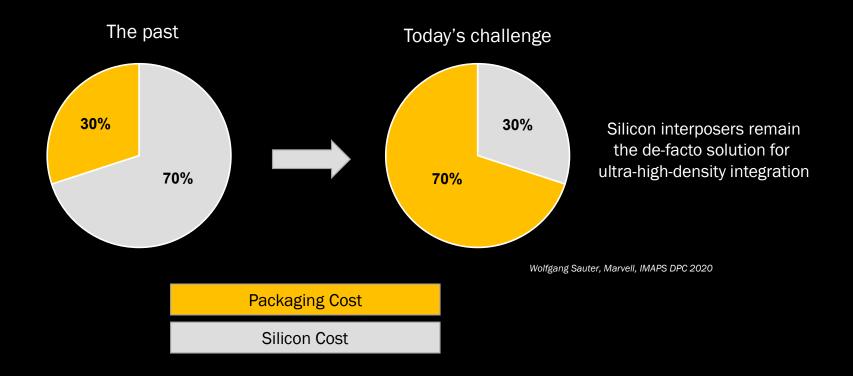

Next generation packaging technologies demand costly materials and processes

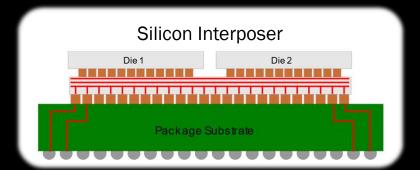

### Solution – Eliminate the Si Interposer

Ultra-high-density organic solutions are positioned to replace Si interposers

### **Obstacles – Emerging Proprietary Solutions**

Established independent supply chain for semiconductor packaging through the OSATs

However, latest advanced packaging technologies emerging from proprietary sources

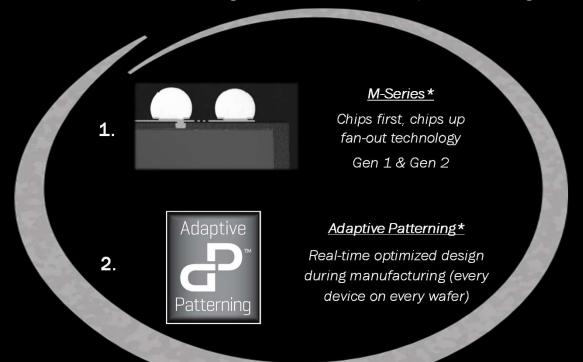

### Solution – Independent Advanced Technology

Ready access to advanced packaging technology - Deca's proven solutions

M-Series Fan-out

Chips first, chips up

fan-out technology

Gen 1 & Gen 2

Adaptive Patterning\*

Real-time optimized design during manufacturing (every device on every wafer)

#### Deca's current licensees

And growing...

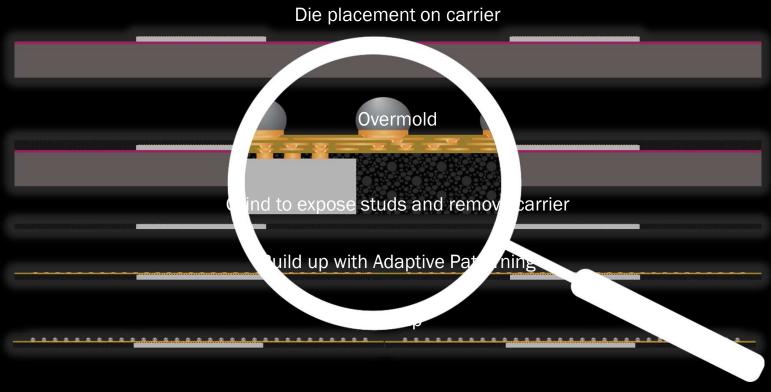

## Solution - A Simple Process

M-Series chips first face up advanced fan-out technology

O DECA

### Agenda

- Introduction

- Industry Perspective

- Challenges & Solutions

- Design Study

- Conclusion

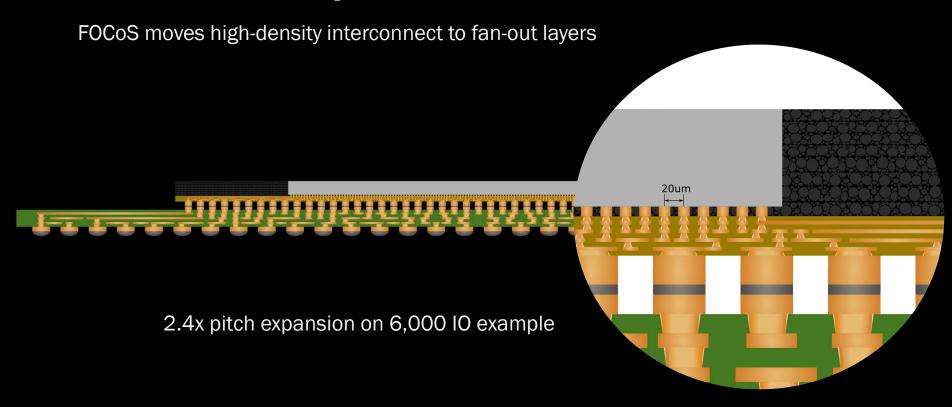

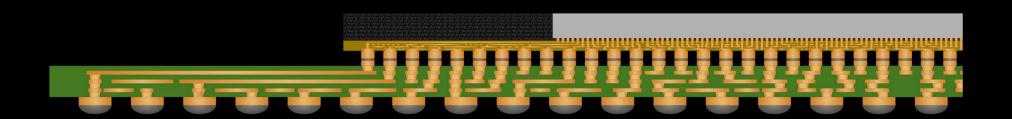

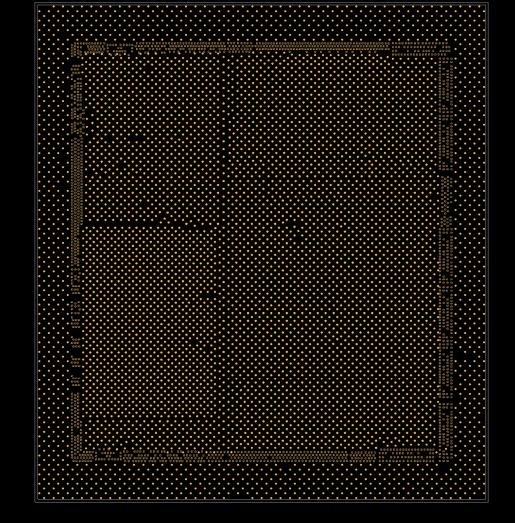

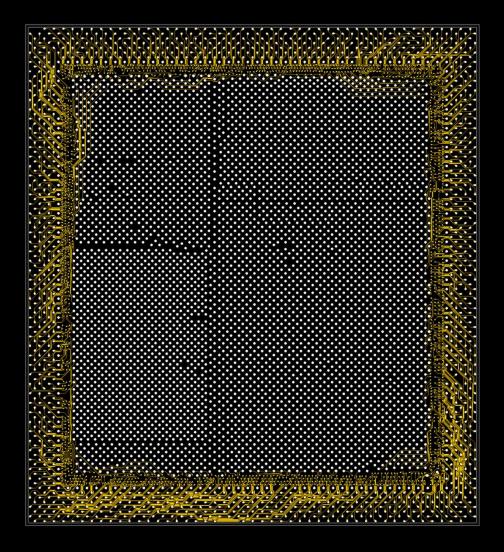

FOCoS moves high-density interconnect to fan-out layers

- 14mm x 16mm finished device

- 6,000 die pads with 2.4x expansion

#### Die specifications

- 4nm silicon

- 12mm x 13 mm

- 4500 core pins 150 µm pitch

- 1500 periphery pins 90 µm pitch

Die

#### Molded M-Series Package

- 5 µm minimum trace & space

- 14 x 16 mm

- 1 routing layer

- 4500 core pins 150 µm pitch

- 1500 periphery pins 212 µm pitch

FOR = 1.44 Fan-Out Ratio

Adding RDL

- Achieved full routing in single layer

- 5 µm minimum trace & space

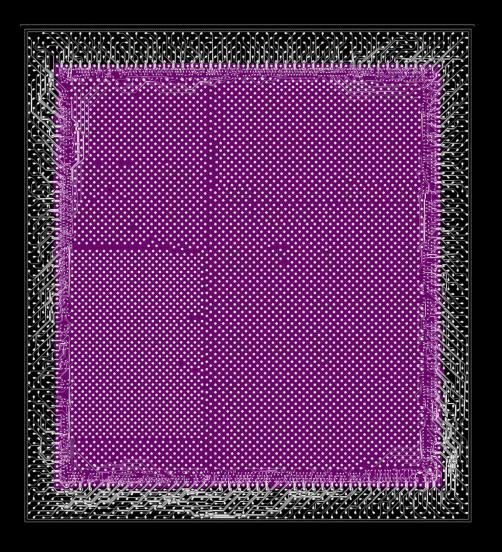

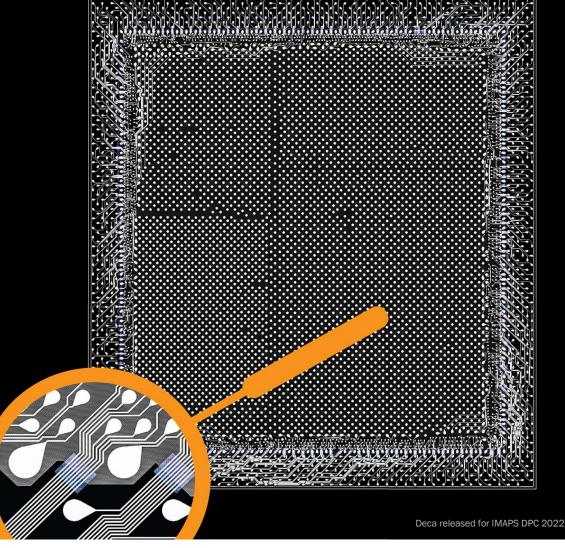

Adaptive Patterning

#### **Adaptive Alignment**

Translates & rotates pattern precisely to measured die location (vias & RDL)

**Adaptive Patterning**

#### **Adaptive Routing**

Dynamically adapt small portion of RDL to precisely complete the connection

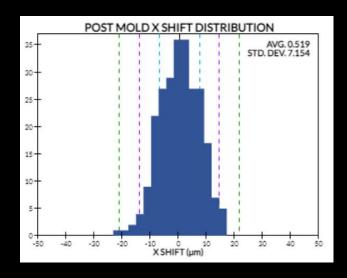

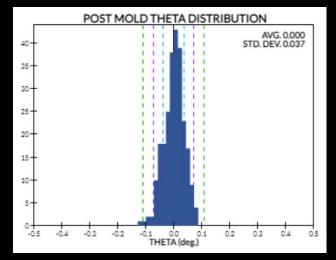

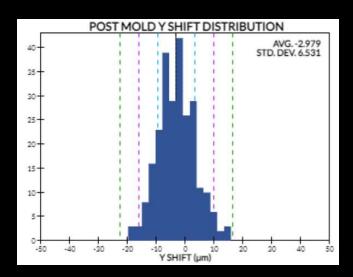

Simulated natural variation of  $\pm 20 \mu m$  XY and  $\pm 0.1^{\circ}$  rotation at  $3\sigma$  (typical production values)

Simulated die displacement histograms

Simulation results

100% yield across all die shifts

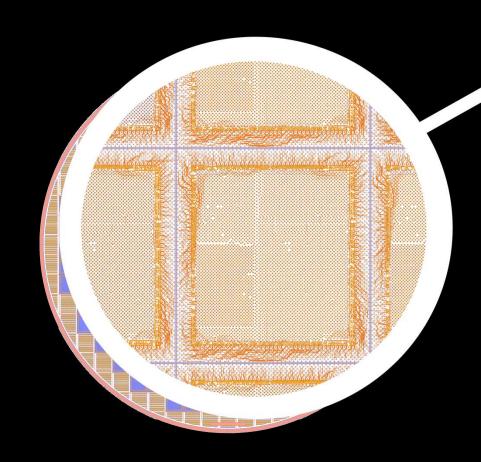

Physical trace variants across the simulated die shift range

Actual RDL variation is negligible

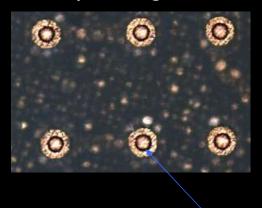

Actual customer device build

#### **Adaptive Alignment**

Vias aligned to Cu stud centers

#### **Adaptive Routing**

#### Conclusion

- Chiplets are now

- Multiple barriers currently exist for mass adoption

- M-Series & Adaptive Patterning provide powerful solutions

- Proven capability through actual FOCoS customer designs

The technology is ready