# Development of Passives on Sapphire Backside

Cherish Bauer-Reich

Mike Reich

Layne Berge

Fred Haring

Oliver Boeckel

Kevin Mattson

Greg Strommen

Justin Vignes

Syed Sajid Ahmad

Aaron Reinholz

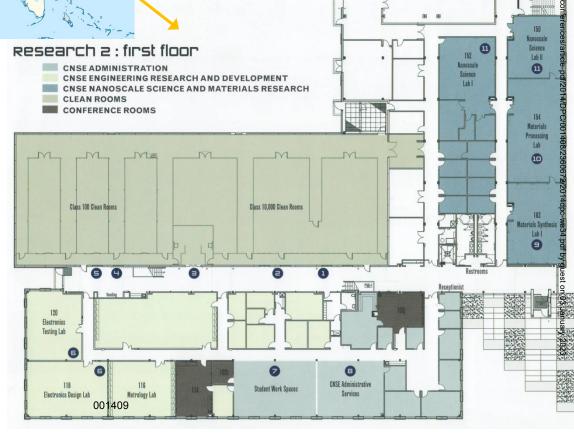

- CNSE: 75,000 sq. ft. facility

- 3 class 100 cleanrooms (MicroFab):

2,300 sq. ft.

- 3 class 10,000 cleanrooms (Pkgg/SMT): 4,000 sq. ft.

- Staffed by full time trained and experienced employees.

- Service chase, gowning area, etc: 5,850 sq. ft.

- Total 12,150 sq. ft.

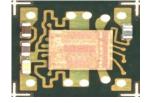

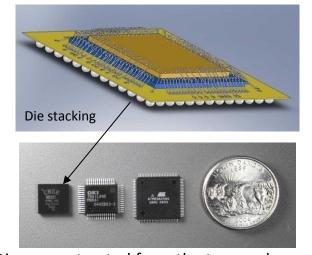

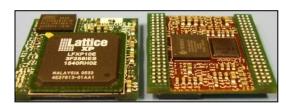

### Examples of CNSE/NDSU Packaging | March 10-13, 2013 | Fountain Hills, AZ USA Examples of CNSE/NDSU Packaging/SMT Products

Top Substrate-**Matching Network**

Package-on-Package

**Bottom Substrate-RF Die**

Cu Pillars on Si and sapphire

Micro-Hotplate

**SRAM**

8051 uC Chip Scale Packages

Dice are extracted from the two packages on right and integrated into the package on left.

3D Package

**Digital SiP**

**Transceiver Module**

System-in-Package

# Sapphire provides unique opportunities for system densification

|                             | Sapphire                                          | Silicon                                                                  |

|-----------------------------|---------------------------------------------------|--------------------------------------------------------------------------|

| Conductivity                | Insulator                                         | Semiconductor                                                            |

| Through Via Insulation      | Does not require insulation of through-vias       | Requires insulation of through-vias                                      |

| Backside<br>Insulation      | Circuitry on backside will not require insulation | Circuitry on backside will require insulation                            |

| Backside<br>Micromachining  | Laser can be used for sapphire micromachining     | Wet processes are necessary for the silicon which are slow and hazardous |

| Laser-Via<br>Cleaning       | Laser vias are clean                              | Silicon's crystal structure necessitates laser-vias cleaning             |

| Laser-Via Wall<br>Condition | Sapphire micromachining yields clean even cuts    | Crystal structure renders laser- cut features raggedy after cleaning     |

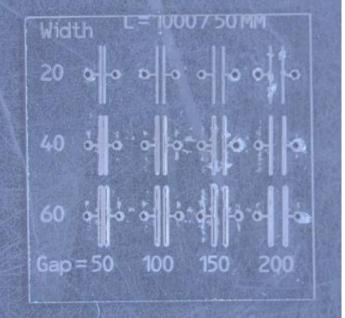

#### Electronics Applications of Sapphire Micromachining

- Through-sapphire vias for

- Chip stacking

- Wafer stacking

- Interconnect to circuitry or components on the backside

- Chip backside interconnect to substrate

- Pockets or trenches for adding passive components to the back of die or wafer.

- Backside grooves for

- circuitry

- antennas

- micro-mixing or dispensing channels for use with nanomaterials or liquids.

- nano-imprinting of inks and other liquids on the backside.

- Laser pattern metal circuitry on back

Vias

**Passives**

Pattern produced on the back of sapphire by filling laser etched grooves with conductive ink

Passives in pockets on the back of sapphire

Sputtered metal laser etched to produce a pattern on sapphire

001412

Examples of developments at CNSE/NDSU

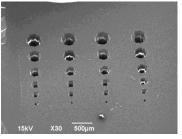

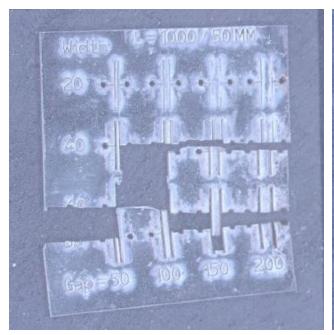

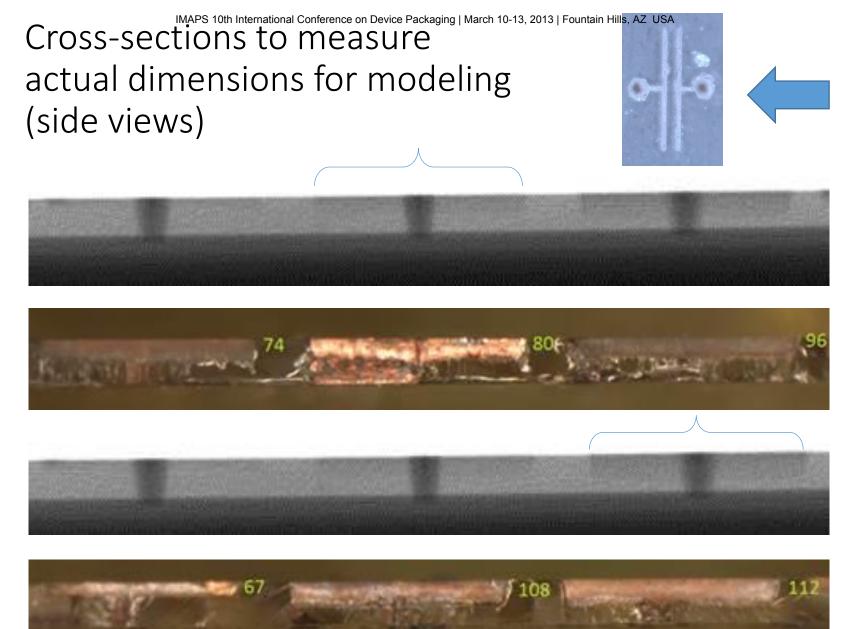

#### Trenches for parameter capacitor

Batch drilling al patterns at once caused chip to crack.

Sequential drilling provided better results.

After Cu sputter

Actual

width

26

45

67

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2014/DPC/001408/2360672/2014dpc-wa34.pdf by guest on 03 January 2023

# Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2014/DPC/00140B/2360672/2014dpc-wa34.pdf by guest on 03 January 202:

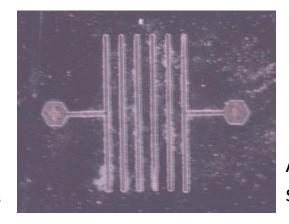

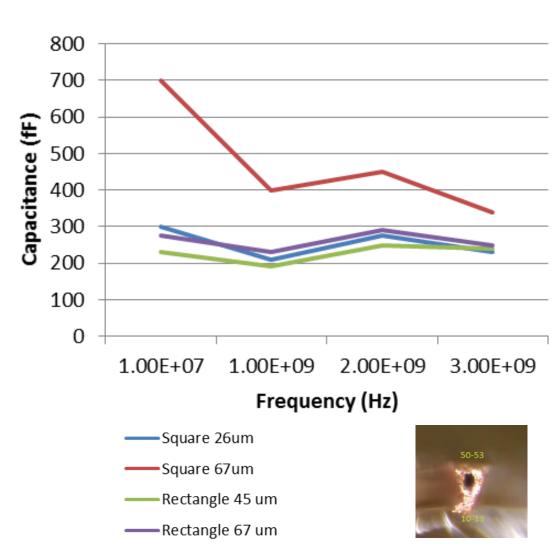

## Capacitor fabrication and Conference on Device Packaging March 10-13, 2013 | Fountain Hills, AZ USA capacitance measurement

- Capacitor trenches were fabricated with laser.

- Trenches were filled with electroplated Cu on sputtered Cu seed layer.

- Plate widths were approx. 26, 45, and 67 μm at the top.

- Dice were fixed to square and rectangular aluminum blocks.

- Capacitance was measured on a microprobe station with Agilent E4991A impedance analyzer.

#### IMAPS 10th harmations conserved in Differ race in Diagram 1430151 consistents, AZ USA

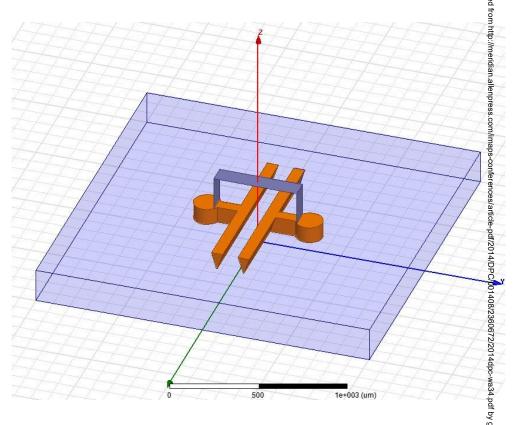

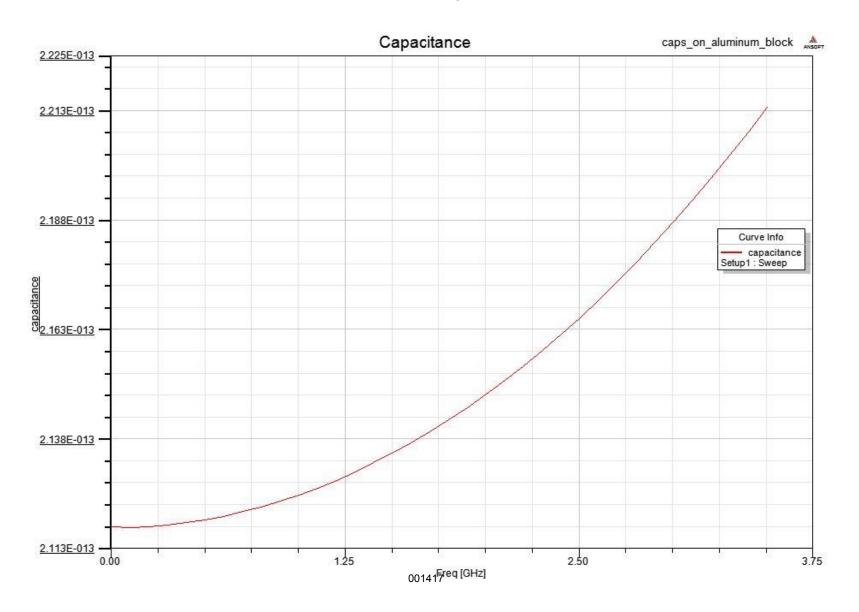

- A model of the parallel plate capacitor was developed in Ansys HFSS.

- The capacitor plate was designed as a trapezoid with the base at the surface being 67 μm wide and the other base, inside the sapphire, was 5 μm wide.

- The grey band going from the pads and above the capacitor is simply a simulation construct to measure the capacitance between the measurement points.

Ansys HFSS model of parallel plate capacitor

## Modeled capacitance

#### Simulation results

- Simulation indicated that, without the aluminum block, capacitances of 153 to 158 fF could be expected.

- The model with the aluminum plate was fairly close to the measurements of three of the four capacitors.

- Measurements were still somewhat higher than simulation for most frequency points.

- Differences in the actual geometry of the capacitors versus the simulated model likely will account for a significant portion of the differences.

- Surface roughness and voids may also play a role in this and will need to be explored.

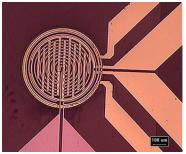

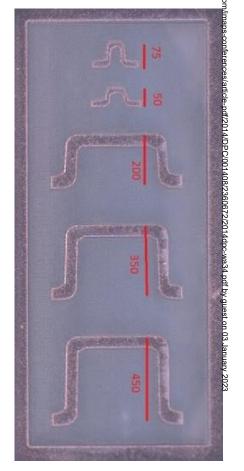

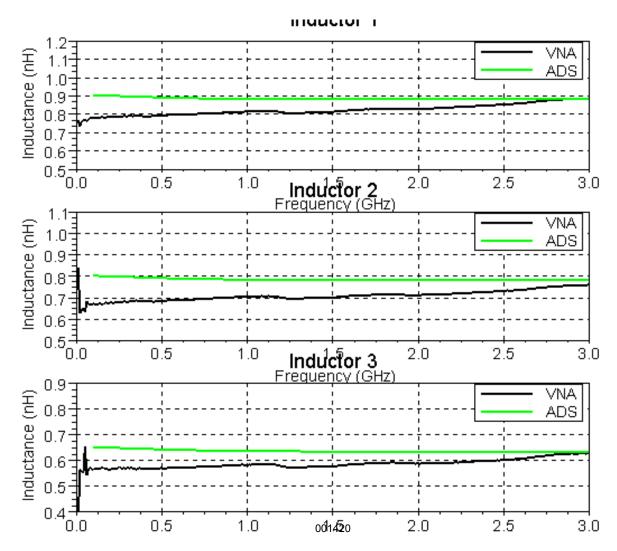

#### Meander Inductor Patterns Made by Isolating Etch on Copper Sputtered Sapphire Die

- 3,000Å sputtered Cu was ablated to create meander inductor patterns.

- modelled in Agilent ADS Momentum

- The largest three inductors were measured using a vector network analyzer (VNA) connected to a microprobe station

- While the VNA measurement showed a slightly lower inductance, particularly at lower frequencies, the measurement matched with simulation at the upper end of the frequency range.

#### IMAPS 10th International Conference on Device Packaging | March 10-13, 2013 | Fountain Hills, AZ USA

# measured versus simulated inductance of largest three meander inductors

#### Conclusions

- This work demonstrates the possibility of fabricating passive elements on the back of sapphire devices.

- Particularly, capacitor and inductor design could be fabricated on the back of a sapphire substrate.

- Passive quality and consistency will depend on the process used to make it.

- Element design and its integration into a device will depend upon the device requirements and the equipment used for the purpose.