# Reliability and Performance Improvement of 3D System-in-Packages in Fan-Out Wafer Level Packaging

Scott Hayes, Tony Gong, Doug Mitchell, Michael Vincent, Jason Wright, Yap Weng Foong Freescale Inc.

Freescale, the Freescale logo, AlliVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, 1 he Energy Efficient Solutions logo, mobiled: PowerOUICC, Oorlo, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Edg. U.S. Pat. & Tim. Off. Beekif, Beeklack, ColdFire, CorreNet, Flexis, Kinelis, MXC, Platform in a Package, Processor Expert, Oorlo Converge, Oorlova, OuliCC Engine, SMARTMOS, TurboLink, VoriOa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

## **Outline**

## SiP/3D Packaging

- Motivation

- Current SiP approaches and 3D enablers

## SiP in Fan-out Wafer Level Packaging

- The Redistributed Chip Package (RCP) Technology

- SiPs in RCP

- Critical RCP SiP Structures

## The RCP Through Package Via (TPV)

- Process and Reliability

- Electrical Characteristics

# System in Package (SiP) Motivations

- Performance

- Die/system performance improvements

- Size/Volumetric Efficiency

- Smaller footprint, thinner packages

- Heterogenous Integration

- Die of different nodes/thickness, SMT, discrete components, MEMS...

- Differentiating Solutions

- SiPs increase opportunity/accessibility for unique systems

# Standard Package and SiP Approaches

## **Multi-Chip Modules**

(WB, FC, SMD)

-Agilent

-Freescale

## **Stacked Die**

(WB, FC, SMD)

-STATSChipPAC

-Toshiba

-ECN

## Package on Package

(WB, FC, TSV, SMD)

-STATSChipPAC

-ESCATEC

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# Some Additional SiP/3D Technologies

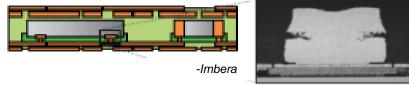

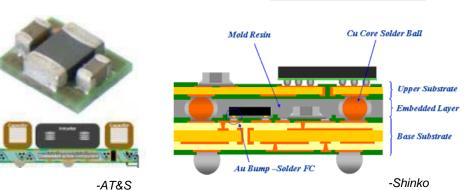

#### **Double Sided Flex**

-Starkey

#### **Embedded Substrates**

## TSV/Si Interposer

-Samsung

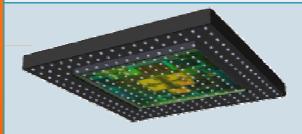

# Freescale Redistributed Chip Packaging (RCP)

- Freescale proprietary technology.

- Scalable, fan-out chip scale package.

- A technology solution for:

- Small form factor packages

- High performance.

- Multi-die, heterogeneous integration.

- 2D, 3D System in Package (SiP) solution.

- Key Applications

- Medical

- Defense

- Migrate to Consumer, Industrial & Auto

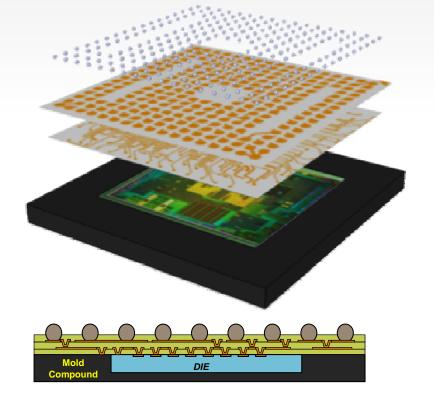

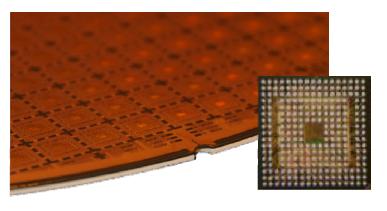

# Freescale's Redistributed Chip Package (RCP)

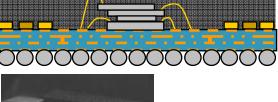

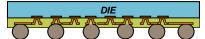

## Fan in vs. RCP Fan out packaging

## Fan-in Wafer level CSP

## Fan-out single die RCP

## Fan-out multi die RCP (SiP)

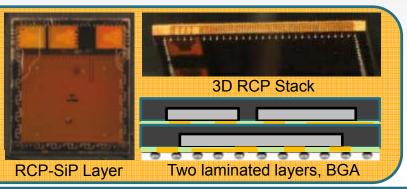

## Fan-out 3D RCP (SiP)

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, OorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beeklit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, OorlQ Onverge, Corivva, QUICC Engine, SMARTMOS, Turbotlink, VortiQa and Xtinnsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

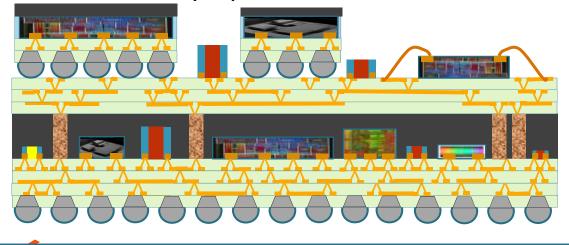

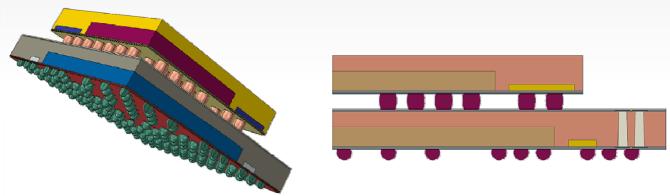

# **RCP and RCP SiP Manufacturing**

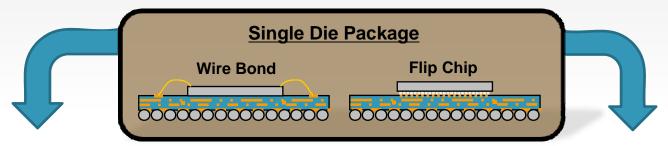

## Single Die Package

XY: pkg. size: die size + 0.5mm + Z: Low profile ~ 125-760µm

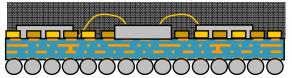

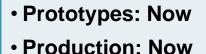

## 2D Multi-die Package

XY: Fine die-die spacing rules

Z: Low profile ~ 125-760μm

Embedded components

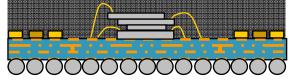

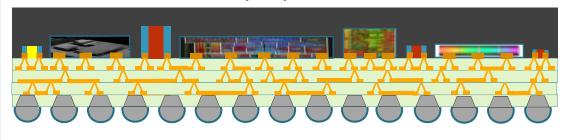

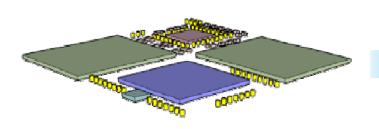

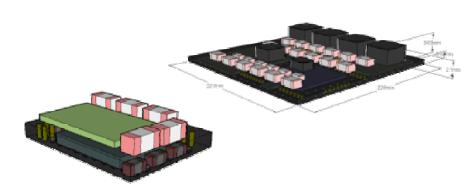

## 3D System-in-Package

XY: Fine die-die spacing rules Z : SMT dependent

Prototypes: Now

• Production: Q2'13

Prototypes: Now

Production: Q4'13

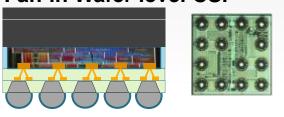

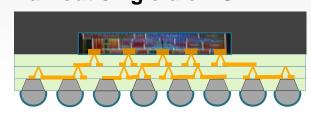

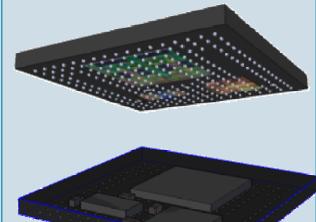

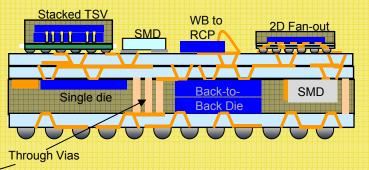

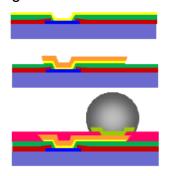

## Methods of Achieving 3D in RCP

## Stacking

- Edge connections

- Very thin

- Routing constraints

## **Pre-placed vias**

- Lower cost

- Good use as PoP solution

- Simplified process

- Limited double sided build up

## Through package vias

- Minimal routing constraints

- Double sided buildup

- •Use of RCP as a 'PCB'

- Most flexible solution

PPV with Solder Bal

Enables 3D SiP solutions for unique medical, defense and consumer applications

# **RCP SiP/3D Integration**

## **Integrated Elements**

Processor, uController, PMIC, ASIC

RF (baseband, transceiver)

FET, IGBT, RGT, SCR

Film Battery

Memory (DDR, Flash, SDRAM)

MEMS (accelerometer)

IPD, SMD (R, L, C)

Oscillator

mmWave (Tx-PA, Rx, VCO)

Thin Film Resistors

Shielding, Thermal management

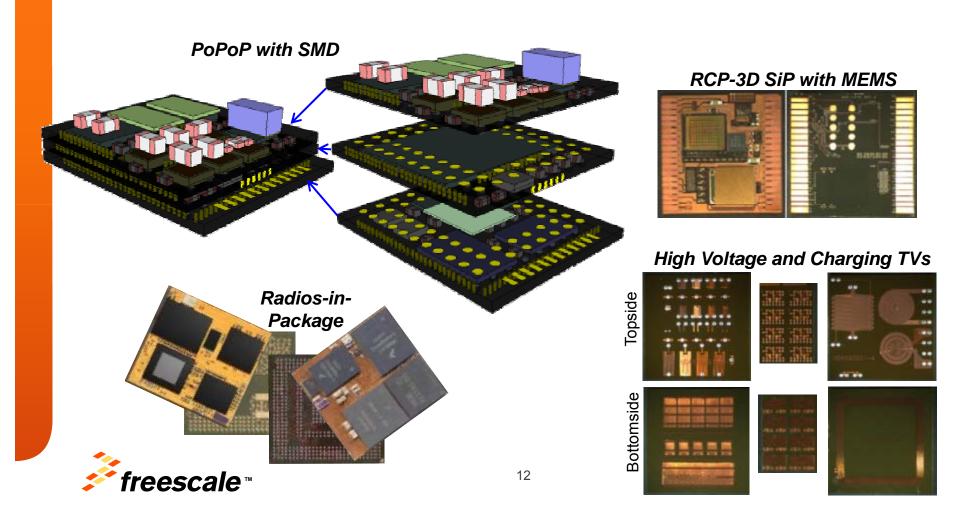

# Demonstrated Applications/Constructions

Low Voltage applications

High Voltage applications (~1kV)

Single Die, 2D Multi-die, 3D SiP, Stacked SiP packages.

BGA, micro-BGA, Flex connectors, wirebond.

Ultra thin packages

High density packages (>100 units in BoM)

Contactless, remote functions

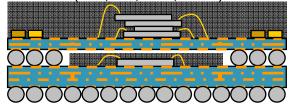

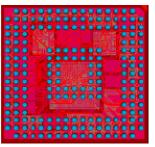

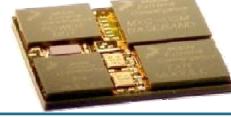

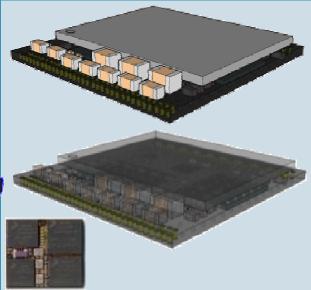

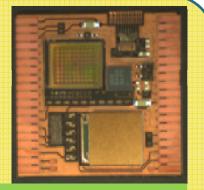

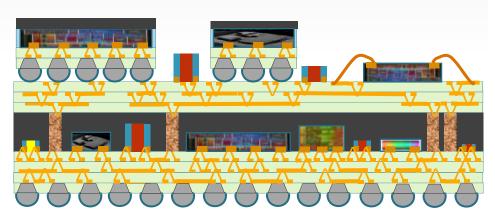

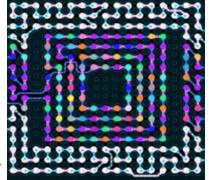

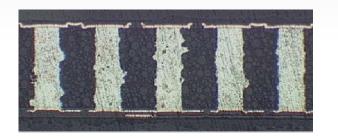

# A Few Applications Enabled by RCP TPVs

- Applications include TPVs and double sided build up.

- SiP BoM counts range from 2 to >100.

- Common systems include processor, memory, ASIC, MEMS, discretes.

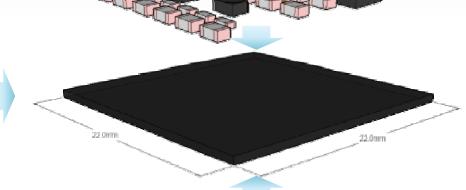

**Example 3D RCP SiP using TPV**

## **Components including in SiP:**

- Freescale MCU, PMIC, Memory die (5 die total)

- 68 discrete passives

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S., Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, Oorl Q Converge, Oorlwa, QUICC Engine, SMARTMOS, Turbolink, Vortica and Kirissic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

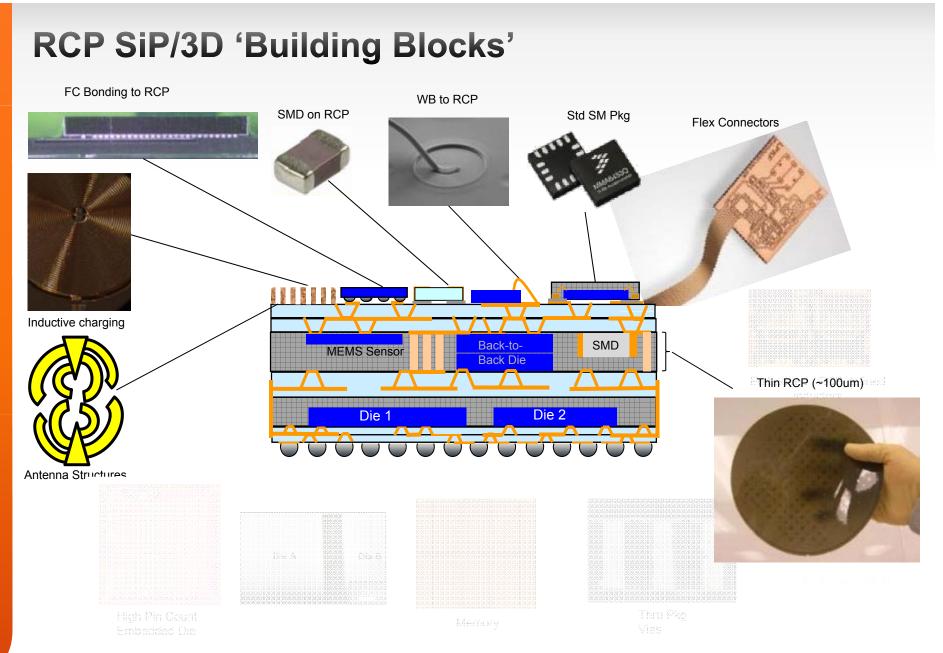

## RCP SiP/3D 'Building Blocks' **Embedded Sensors** Multiple layers of signal routing including power, ground, and signal isolation M1 M2 M3 M4 Ultra Thin Pkg Stacking with Side Connections **SMD MEMS Sensor** Embedded, RCP defined inductors Die 2 Die 1 (unitmun) 0.15 max. in thickness Die A Die B Embedded SMD Through Package Vias **High Pin Count** Memory Embedded Die

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U. S. Pat. & Tm. Off, BeeKit, BeeStack, ColdFire-, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Ktrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

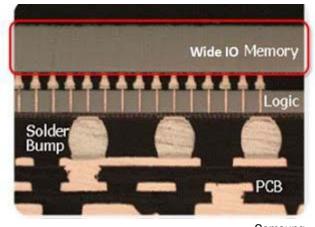

# **TSV and TPV: Complementary 3D Enablers**

## Through Silicon Via

# Die #3 - Die #4 Die #2 - Die #5 Die #5 Silicon interposer SiP Substrate Circuit board -EETimes

-P.S. Andry, et. al., IBM Journal of Research and Development

- •Fine geometry possible (~10µm dia)

- High aspect ratio possible (>10:1)

- •Low resistance possible ( $<50m\Omega$ )

- •Typical uses: 2.5D, 3D-die stacking, high I/O, high bandwidth

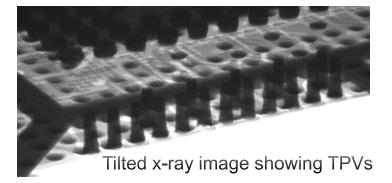

## Through Package Via

-Freescale

- •Coarse geometry (~100-200µm dia)

- •Lower aspect ratio (3:1 5:1)

- •Low resistance typical ( $<50m\Omega$ )

- •Typical uses: 3D SiP, true heterogeneous integration

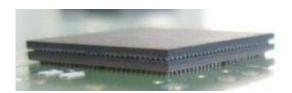

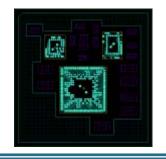

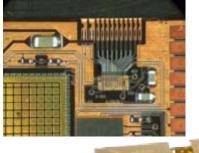

# **RCP TPV – Reliability Vehicle**

3D RCP PoP TV

Test Loops on 3D RCP PoP TV

### **3D RCP PoP Test Vehicle**

- •Base Pkg: 12x12mm, P0.4mm, 2ML/1ML Double Sided RCP, TPV

- •Top Pkg: 9x9mm, P0.5 mm, 2ML RCP

## **Reliability Plan**

- •Pre-con (MSL3/260C)

- •AATC (-40 to 125C)

- •uHAST

JEDEC: JESD22-A104 JEDEC: JESD22-A118

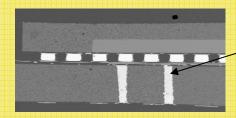

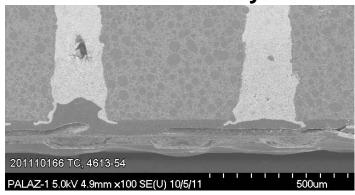

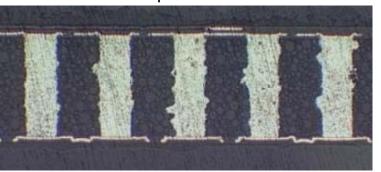

TPVs before optimization

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beeklit, BeeSlack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, Vortica and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. 9 2011 Freescale Semiconductor, Inc.

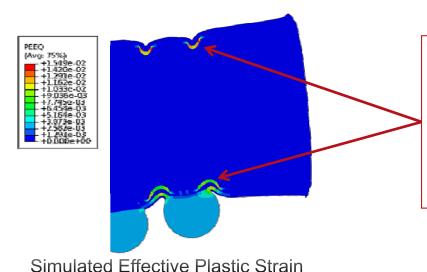

# **RCP TPV – Predictive Modeling**

Quarter and cross sectional models used for simulation of thermomechanical behavior of through package via structures

in RCP TPV resulting from AATC

Regions of elevated stress/strain resulting from simulated AATC.

Potential areas of concern through temperature cycling.

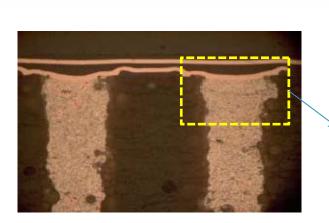

# **RCP TPV – Reliability Findings**

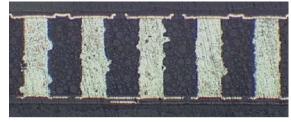

- •Electrical test indicated a failed net after 1000 cycles (-40 to 125C).

- •Cross section and SEM indicated discontinuity within a TPV near a build up interface.

- •Failure noted on 2/80 units.

- •Structural optimization continued.

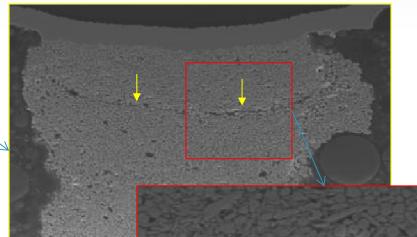

# **Through Package Via - Challenges**

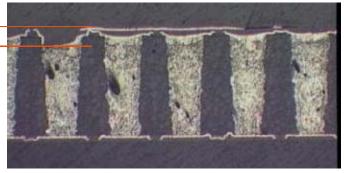

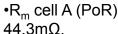

**Pre-Optimization TPV**

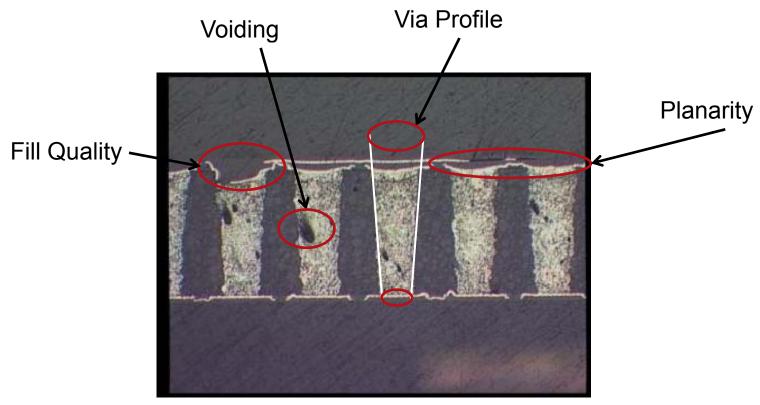

# Through Package Via – Structure Optimization

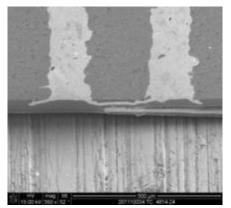

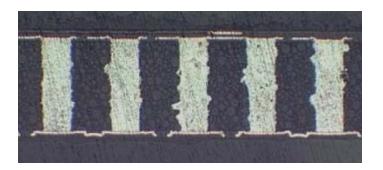

## **Via Fill Quality**

- Voiding

- Incomplete fill

- Improved yields

- More reliable interface

### **Via Profile**

- >50um difference via top to bottom

- •Process implications, variance.

- <25um difference via top to bottom</li>

- •Improved yields, deviation.

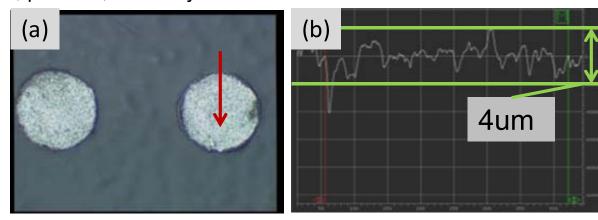

# **RCP TPV – Structure Optimization**

## **Via Planarity**

**Pre-Optimization**

>25um planarity typical, significant varianceYield, process, reliability Post-Optimization

~4um planarity

# **RCP TPV – Electrical Characterization**

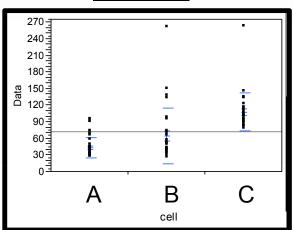

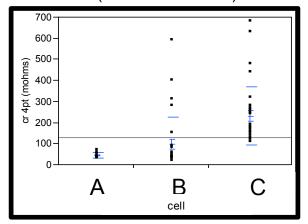

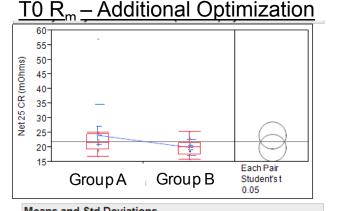

## Time Zero

Post 2000 Cycles

(AATC -40 to 125C)

- • $R_m$  cell A (PoR) 42.8 $m\Omega$ .

- •N=30

- •STD~18.1mΩ.

- •No significant increase in TPV resistance.

- •Each net contains 2 vias

- •Typical TPV resistance <25mΩ.

| iviean | s and St | d Deviati | ions    |         |           |           |  |

|--------|----------|-----------|---------|---------|-----------|-----------|--|

|        |          |           |         | Std Err |           |           |  |

| Level  | Number   | Mean      | Std Dev | Mean    | Lower 95% | Upper 95% |  |

| Center | 12       | 24.1750   | 10.6467 | 3.0734  | 17.410    | 30.940    |  |

| Edge   | 12       | 20.0083   | 2.7054  | 0.7810  | 18.289    | 21.727    |  |

•Further optimization of TPV structure shows average net resistances  $<25m\Omega$ .

- •N=30

- •STD~12.8m $\Omega$ .

\*Four point probe structure used for measurement

Freescale, the Freescale logo, Allfvec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, OorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beeklit, BeeSlack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, OorlO Converge, Oorliva, OUICC Engine, SMARTMOS, Turbolink, VoriGa and Xtinsics are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# RCP TPV - Reliability Results Post-Optimization

- Optimized process yields 99.4%

- Optimized structure surviving AEC Grade 0 (2000AATC, -50°C to 150°C)

## RCP 3D PoP – Reliability Results

|  | Cell A (-40/125)      | MSL3/260 | 250 cycles | 500 cycles | 1000 cycles | 2000 cycles |

|--|-----------------------|----------|------------|------------|-------------|-------------|

|  | Lots 6160, 6164, 6166 | 0/40     | 0/40       | 0/40       | 0/40        | 0/40        |

|  | Cell B (-50/150)      | MSL3/260 | 250 cycles | 500 cycles | 1000 cycles | 2000 cycles |

|--|-----------------------|----------|------------|------------|-------------|-------------|

|  | Lots 6160, 6164, 6166 | 0/40     | 0/40       | 0/40       | 0/40        | 0/40        |

| $\mathbf{q}$ | Cell C (uHAST,130C/85RH) | MSL3/260 | 96hrs | 144hrs |

|--------------|--------------------------|----------|-------|--------|

|              | Lots 6160, 6164, 6166    | 0/40     | 0/40  | 0/40   |

JEDEC: JESD22-A104 JEDEC: JESD22-A118

# **Summary**

- 3D RCP with TPV structure demonstrated reliable passing:

- MSL3 (260°C)

- 144 hours uHAST (130°C, 85%R.H.)

- 2000 cycles AATC (-40°C to 125°C)

- 2000 cycles AATC (-50°C to 150°C) AEC Grade 0

- Average measured TPV net resistance <25mΩ.</li>

- RCP with TPVs enables SiP & 3D packaging solutions for:

- ✓ Heterogeneous integration

- ✓ System miniaturization

- ✓ Enhanced system performance

## **RCP Contact**

Scott Hayes (Development Manager)

s.hayes@freescale.com

480-413-4608

Navjot Chhabra (Program Manager)

navjot.chhabra@freescale.com

512-895-6470

Tony Gong (Business Development)

t.gong@freescale.com

480-413-5325

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. Freescale is licensed by EPIC Technologies Inc. to make and sell packages that include Epic's "Chips First" technology and related patents.

© 2010 Freescale Semiconductor, Inc.

## WLCSP vs. RCP

**WLCSP**

- · Blind assembly directly on a wafer

- Pkg size = die size

- · Build up process based on bumping technology

- Single RDL (Redistribution Layer)

- · Exposed back side and edge of die

- · Wafer reconstitution with KGD

- Space creation to accommodate more IOs and sophisticate routing

- Build up process with "Fan-out" routing

- Multiple RDLs (Redistribution Layer)

- · Physical protection for die