# TSV Market Drivers, Demand & Product Readiness

義

RELIABILITY

R. Huemoeller SVP, Adv. 3D Interconnect Platform Develop March 6, 2012

- TSV Platform Drivers

- Interposer Supply Chain Logistics

- Product Offerings & Timing

- Conclusion

## TSV Platform Drivers "Technology Convergence"

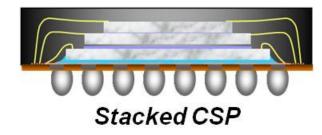

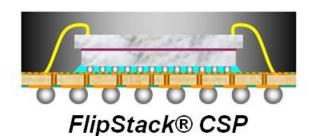

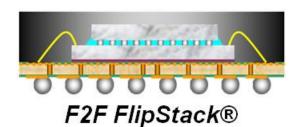

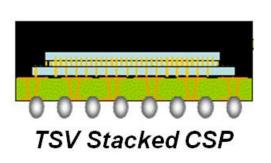

# Stacked CSP (SCSP) – Migration to TSV

TSV Stacked CSP

Performance Driven

## Compared to POP Memory

- 8x performance in bandwidth

- 50% power savings

Courtesy of Samsung

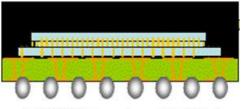

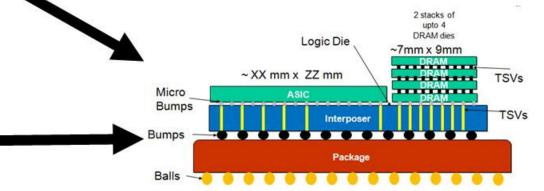

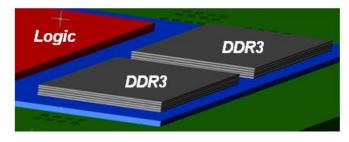

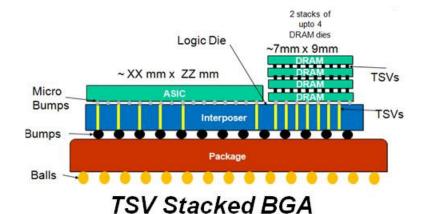

# FCBGA – Migration to TSV

Logic with Embedded Memory

Logic and Memory in Same Module

Logic and Memory in Separate Packages

TSV Stacked BGA

Performance & System Level Cost Driven

Amko

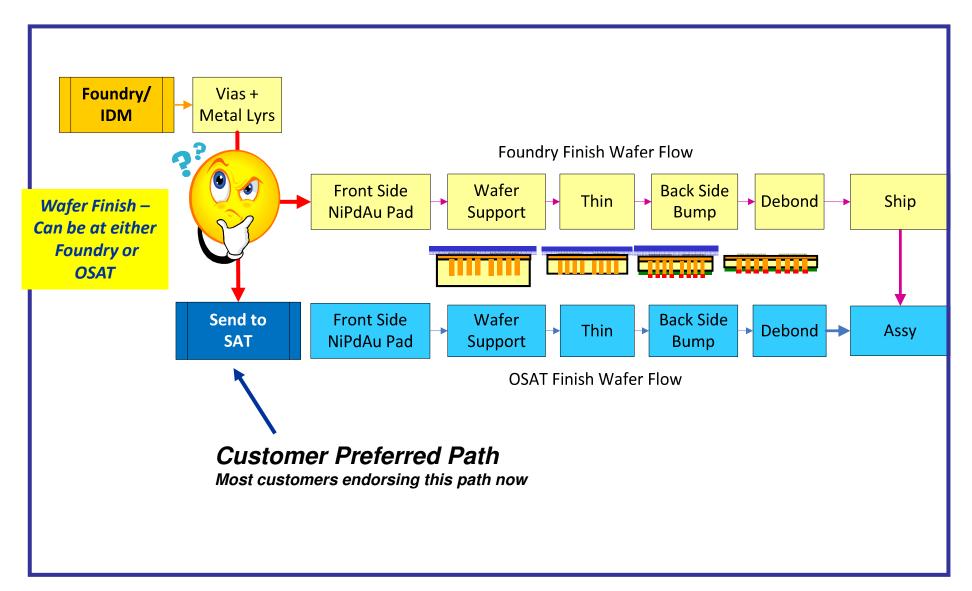

# **TSV Product Segments**

## 3D Vertical Stacking

- Memory and Application Processor Driven

- Today CSP focused on 28nm CMOS... scaling to 20/22nm

- Application Processors almost exclusively moving to OSAT finished wafer process flows

## 2.5D Interposer – Side by Side Stacking

- Network, GPU and CPU driven

- All large package body focused

- All large silicon interposer focused (near retical size)

- Both Foundry finished and OSAT finished wafer process flows being used

000462

6

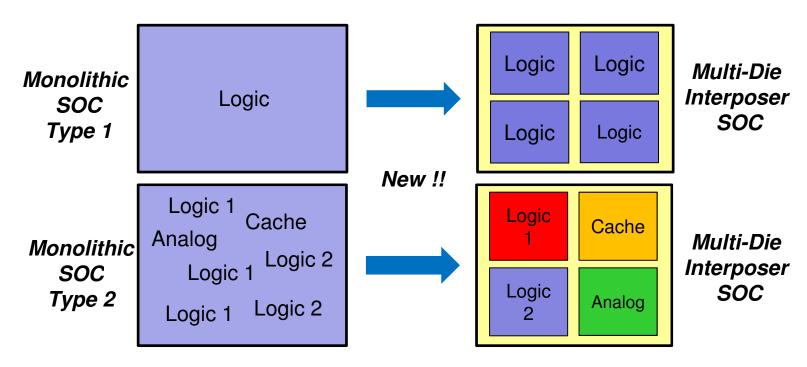

# **3DIC TSV Product Opportunities**

- Focus process node development on specific application functionalities

- ✓ Reduces complexity and mask layer count of process node

- ✓ Reduces advanced process node 'Time to Market'

- ✓ Improves wafer yield

- ✓ Reduces wafer start cost

- Improves performance, power, and area of each application functionality

# allenpress.com/imaps-conferences/article-pdf/2012/DPC/000334/2260706/2012dpc-ta11.pdf by guest on 03 January 2023.

# **Primary Drivers for Interposers**

|                                                   | Memory Bus<br>Speed        | Lower Power                                  | Fab Yield                          | Cost                                        | Stress<br>Reduction in<br>Top Die |

|---------------------------------------------------|----------------------------|----------------------------------------------|------------------------------------|---------------------------------------------|-----------------------------------|

| Si Interp <sup>T</sup> + DDR <sup>T</sup> + Logic | Wide<br>Parallel<br>Busses | Wide<br>Parallel<br>Busses                   | Departition<br>Fewer<br>SoC Layers | System<br>Level<br>Reduction                | <b>✓</b>                          |

| Si Interp <sup>T</sup> + Logic                    |                            | Gate to<br>Gate<br>Routing<br>between<br>Die | Deconstruct<br>into<br>Smaller Die | Fab Yield<br>Improve<br>= Cost<br>Reduction | <b>✓</b>                          |

| Si Interp <sup>T</sup> + Logic + SERDES           |                            |                                              | Departition<br>(e-DRAM)            | System<br>Level<br>Reduction                | ✓                                 |

# Interposer Supply Chain Logistics

# **Potential Interposer Technologies**

## Laminate (Organic)

- Delivered in large panel format (500x500mm typ.) with film based dielectrics

- Several elite substrate manufacturers investigating today

## Glass

- Can be delivered in panel (large) or wafer (8") format at target thickness

- Several companies investing in applicable capability to support packaged semiconductor products

## Silicon

- Can be delivered in 8" or 12"

- Several companies supporting this product space & a few others investigating

- Leveraging idle foundry space on legacy node technologies

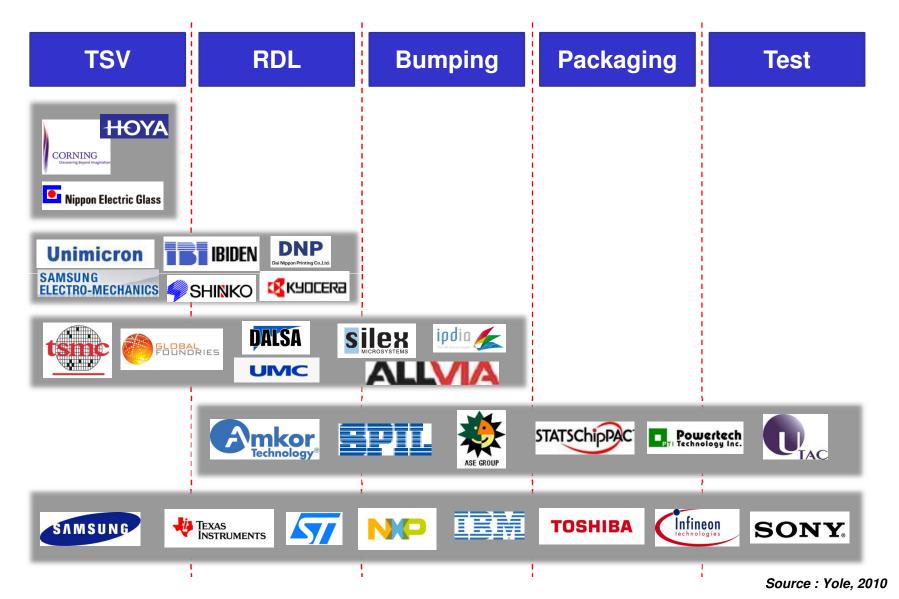

# Who is Doing What?

Amkor Info for Controlled Release at IMAPS DPC 11

Mar-12, R.Huemoeller

# **Interposer Supply Chain Challenges**

## Glass

- Panel format is strongest asset; leveraging panel display market

- Panel format presents challenges for CMP based activities (i.e. damascene processing)

- More compatible with polymer dielectrics and ≥ 5μm line/space

- Large panel plating process & Cu thickness variation

- Via creation still very expensive in glass

## Laminate (organic)

- Elite '5' substrate suppliers targeting this space

- Limited to ≥ 8μm line/space today and 40μm vias on 85μm pads

- Development targeted at 5µm line/space ....but several years away

- 5µm line/space requires stepper, and special resist technology

- Via size/pad consumes too much space; latency issues will limit adoption

000468

12

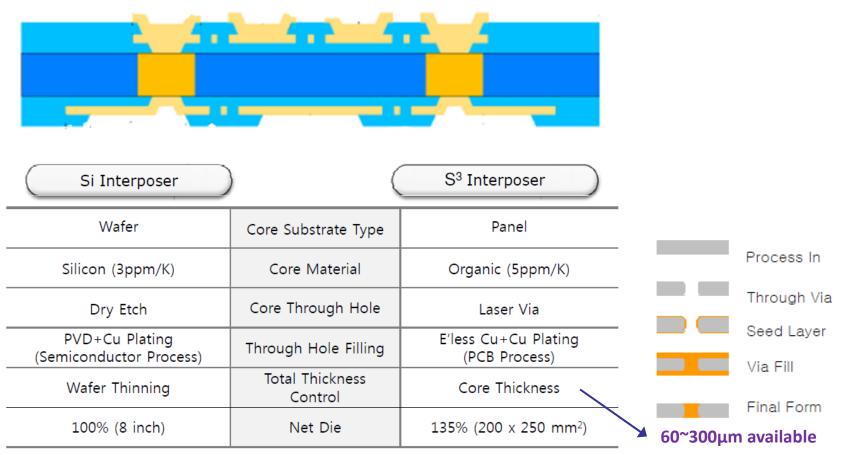

# Laminate vs Silicon Interposer

Through via by laser drilling or mechanical punching

12 inch = primary path

**Source : Samsung Electro-Mechanics**

# Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/DPC/000334/2260706/2012dpc-ta11.pdf by guest on 03 January 2023

# Silicon Interposer as Substrate

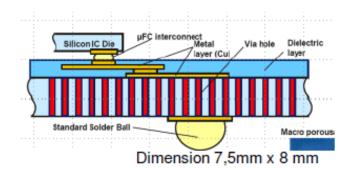

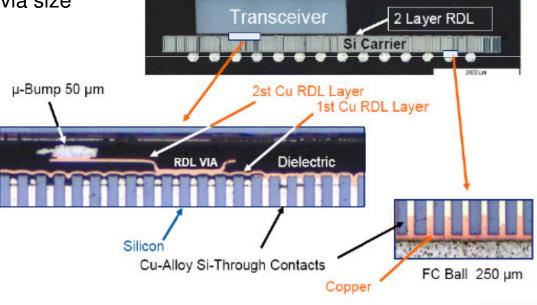

## **RF Module – Mobile Transceiver**

- RDL at 20µm line/space

- ~8µm dia. & 300µm deep TSV

- Laminate could play ...but via / pad?

- Glass a better fit due to via size

© Fraunhofer IZM

# Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/DPC/000334/2260706/2012dpc-ta11.pdf by guest on 03 January 2023

## Interposer Supply Chain Issues – Silicon

# **Predominant Interposer Designs**

# Silicon Interposer Supply Chain

## Sources

- Several foundry sources interested in manufacturing silicon interposers

- A couple of sources already delivering fully functional wafers

## Activity

- Significant activity underway

- General target is 100μm as finished thickness with some backside RDL

- Some with passive components on top side of interposer

- Both heterogeneous and homogeneous die layouts

## Challenges

- Design rules are aggressive < 2μm line/space with up to 5μm vias</li>

- Design rules fit low technology node BEOL silicon very well

- Copper damascene (dual) & 300mm wafer requirement don't necessarily match up with idle capacity

## **Interposer Supply Chain Summary**

## General

Need to strengthen supply chain; must entertain many alternative solutions

## Laminate (Organic)

- Several companies reviewing cost add allowance & volumes to justify investment

- Current limitations in via/pad design rules will limit market scope / application

## Glass

- Panel size is best attribute; LCD / flexible display in broad use

- Via generation cost and plating distribution challenges will limit adoption

## Silicon

- Foundries dominating supply chain, but only '3' real players today

- Ultimately, cost needs to be in-line with market pricing to allow broad adoption

# TSV Products Entering Market "Over Next Few Years"

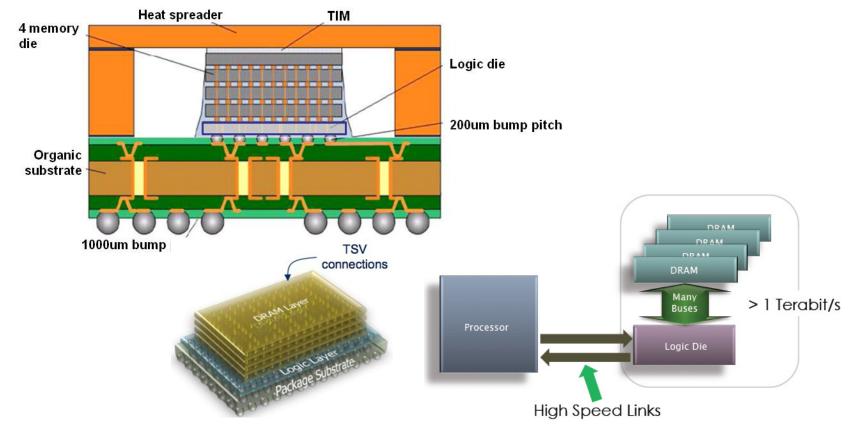

## **3D CSP Based Vertical Stacks**

## Memory

- Very high bandwidth at > 1 Tb/sec

- Used for high performance server & super computer (HPC)

- Eventually, Wide I/O DDR

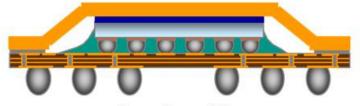

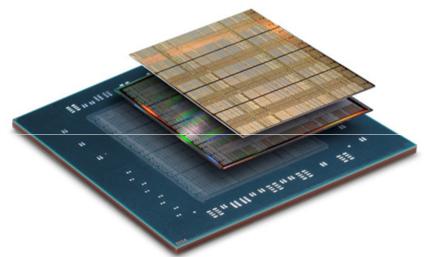

# 2.5D Silicon Interposer Based Product

## FPGA Package Build Structure

- Design increases logic capacity while reducing power

- √ 100X improvement in inter-die bandwidth / watt

- √ 50% power reduction from 40nm

- √ 5x reduction in latency

- √ 20x denser wire pitch

- FPGA ~ 8mm x 24mm

- > 50,000 μbumps per die

- > 200,000 total μbumps per package

- Interposer ~ 31mm x 25mm

- ~20,000 C4 bumps per interposer

- minimizes heat flux issues

- Substrate

- 45mm body with ~ 2000 BGA balls

Ramping into production Today !!

Xilinx's Virtex-7® 2000T device showing from top to bottom the packaging substrate, the silicon interposer & 4 FPGA die (courtesy of Xilinx)

21

# Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/DPC/000334/2260706/2012dpc-ta11.pdf by guest on 03 January 2023

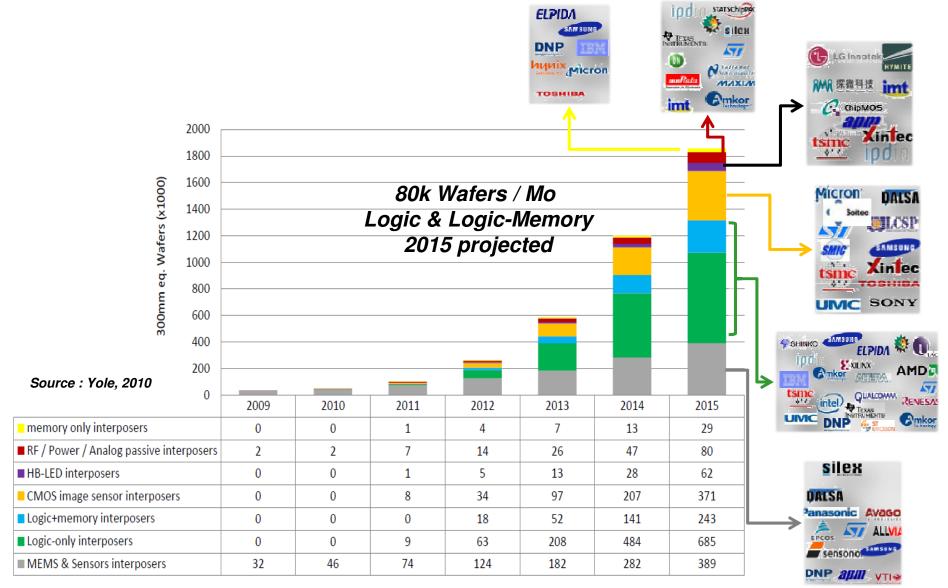

## 2.5D Interposer Wafer Forecast by Application white the constant of the consta

Expect compound annual growth > 80% over next 3 years through 2015 (300mm eg.)

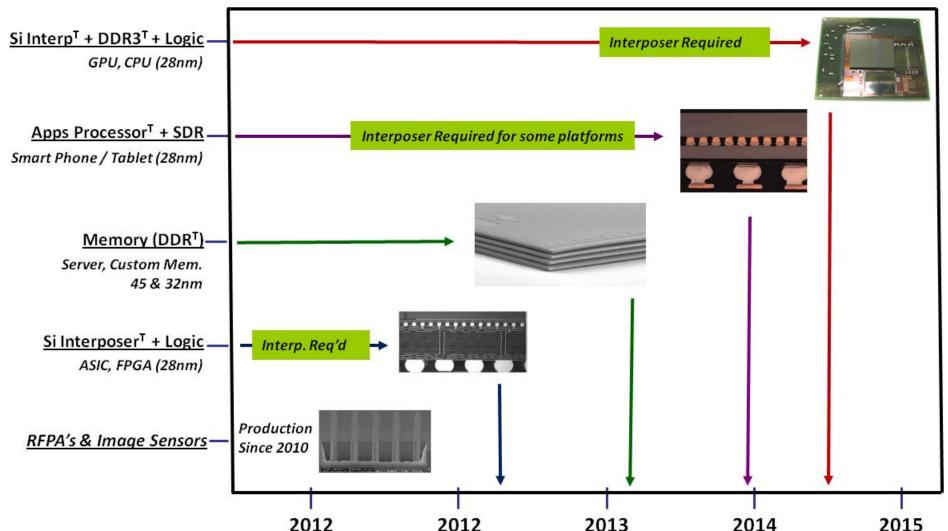

## **TSV General Production Intercepts**

Die with TSV indicated by = T

- Interest and activity accelerating

- 3D CSP Form Factor Improvement

- 2.5D Reduces Complexity

- ✓ Reduces mask layer count of process node

- ✓ Reduces advanced process node 'Time to Market'

- ✓ Improves wafer yield

- ✓ Reduces wafer start cost

- Both Improve Performance & Reduces Power Requirement

RELIABILITY & TRUST