## NCP (Non Conductive Paste) for Narrow Gap Flip Chip Package and TSV Package

**Tomoya Masuda, Yuko Kondo,

Hiroshi Takahashi, Hidenori Abe**

**Hitachi Chemical Co.,Ltd.**

- 1.Hitachi Chemical and MSS**

- 2.FC and TSV roadmap and Underfills**

- 3.NCP development**

- 4. Summary**

1. Hitachi Chemical and MSS

2. FC and TSV roadmap and Underfills

3. NCP development

4. Summary

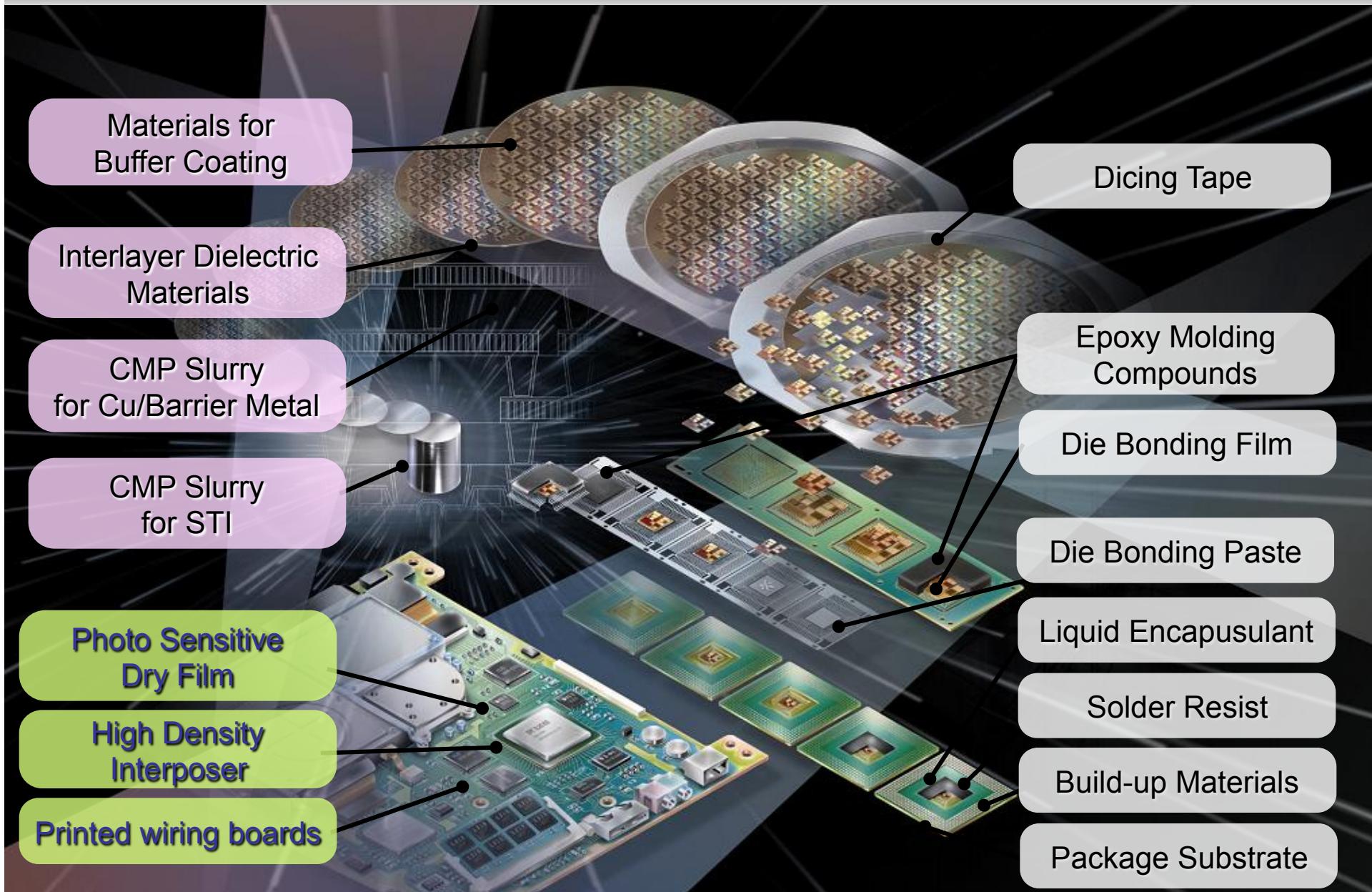

# Hitachi Chemical materials lineup

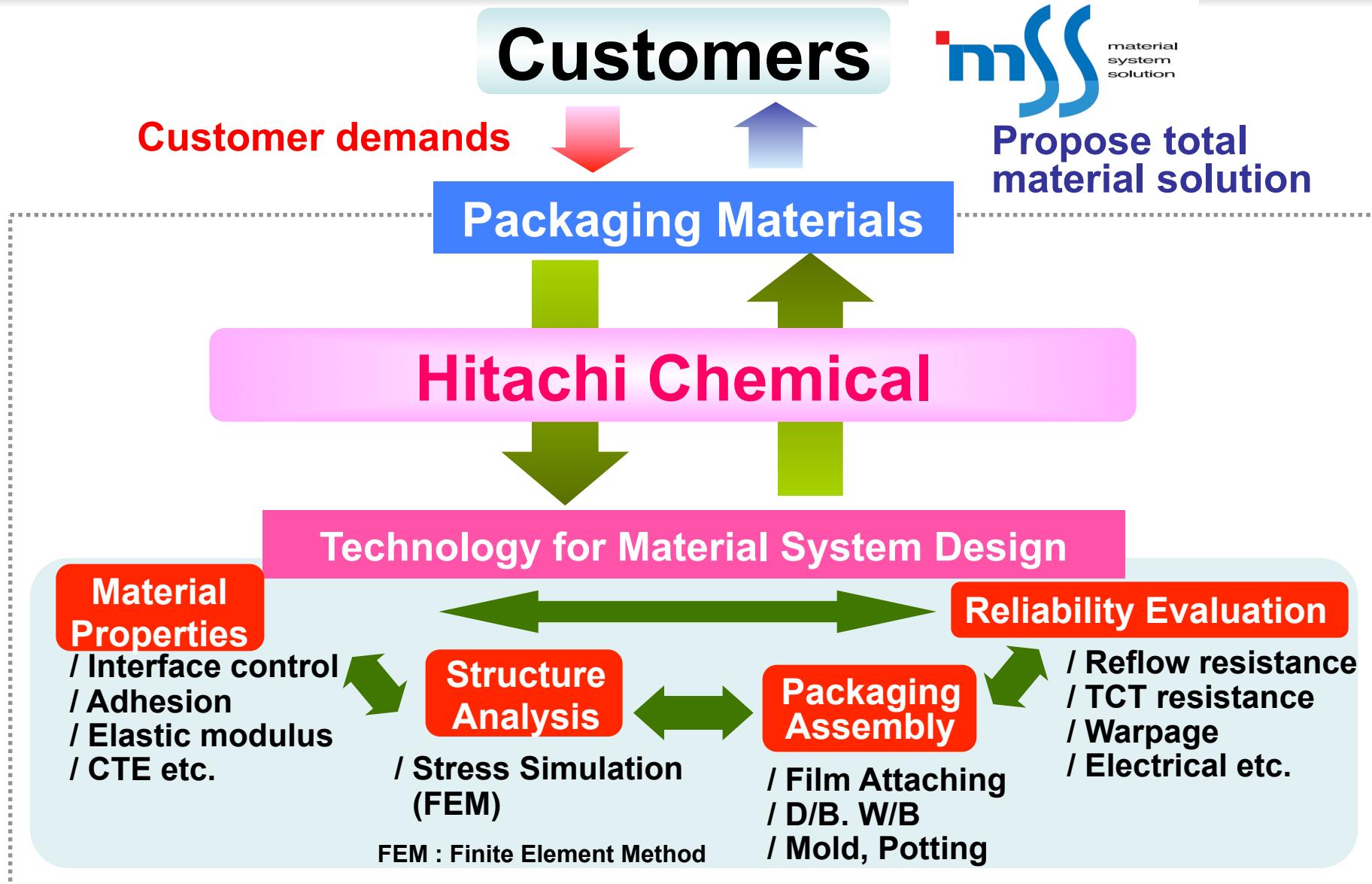

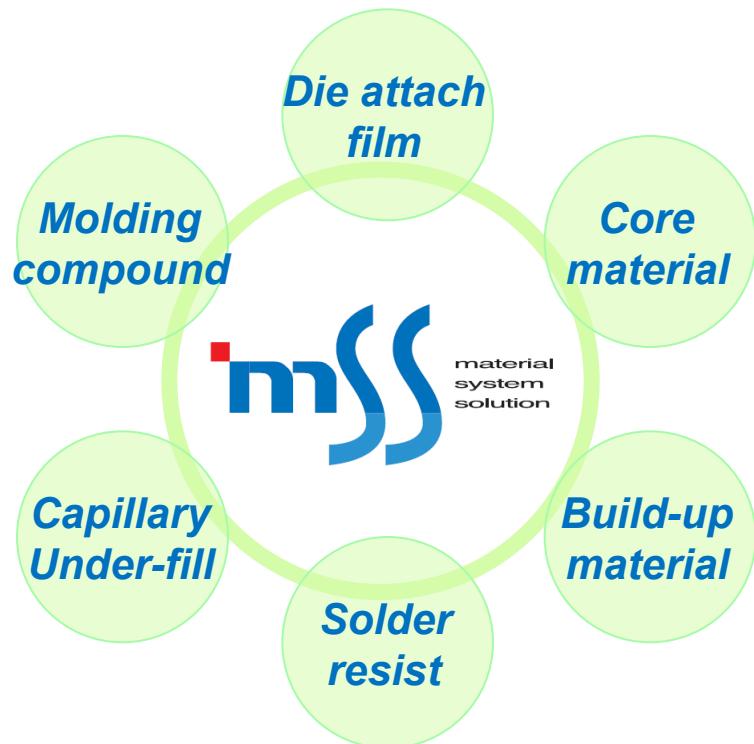

# Material system solution (MSS)

# Material system solution (MSS)

## 2011 (available)

- a) FC-BGA ( Chip size : ~ 20mm )

- b) FC-CSP ( Bare Die, Std. TMV )

- c) Stacked-CSP

## Next generation

- a) FC-BGA ( Chip size : 20 ~ 25mm )

- b) FC-CSP ( Exposed-Die TMV )

- c) WLFO

- d) 2.5D-PKG ( Silicon interposer )

- 1. Hitachi Chemical and MSS**

- 2. FC and TSV roadmap and Underfills**

- 3. NCP development**

- 4. Summary**

# FC package roadmap

| Item             | unit      | 2010                                  | 2012              | 2014              | 2016              | 2018              | 2020              |

|------------------|-----------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Chip - Substrate | um        | Pad pitch<br><b>40 *</b><br>(150-200) | 40<br>(135-200)   | 40<br>(120-180)   | 35<br>(110-150)   | 30<br>(110-150)   | 30<br>(90-150)    |

|                  |           | Chip thickness<br>70<br>(200)         | 50<br>(100)       | 50<br>(100)       | 50<br>(90)        | 50<br>(90)        | 35<br>(80)        |

|                  |           | Bump diameter<br>20<br>(90)           | 17<br>(80)        | 17<br>(80)        | 17<br>(80)        | 15<br>(70)        | 15<br>(70)        |

|                  |           | Bump height<br>10<br>(75)             | 9<br>(65)         | 9<br>(65)         | 9<br>(55)         | 8<br>(55)         | 8<br>(45)         |

|                  |           | Gap<br><b>15</b><br>(50)              | <b>12</b><br>(40) | <b>12</b><br>(40) | <b>12</b><br>(35) | <b>10</b><br>(35) | <b>10</b><br>(30) |

| Chip – Chip      | Pad pitch | <b>40</b>                             | <b>40</b>         | <b>40</b>         | <b>20</b>         | <b>20</b>         | <b>20</b>         |

\*Top:Peripheral, (Bottom):Area array

Source ; Japan Jisso Gijyutu Roadmap 2011

➤Finer pad pitch and narrow gap is expected

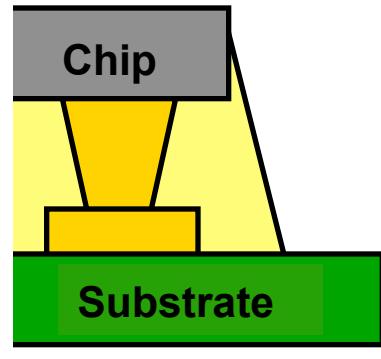

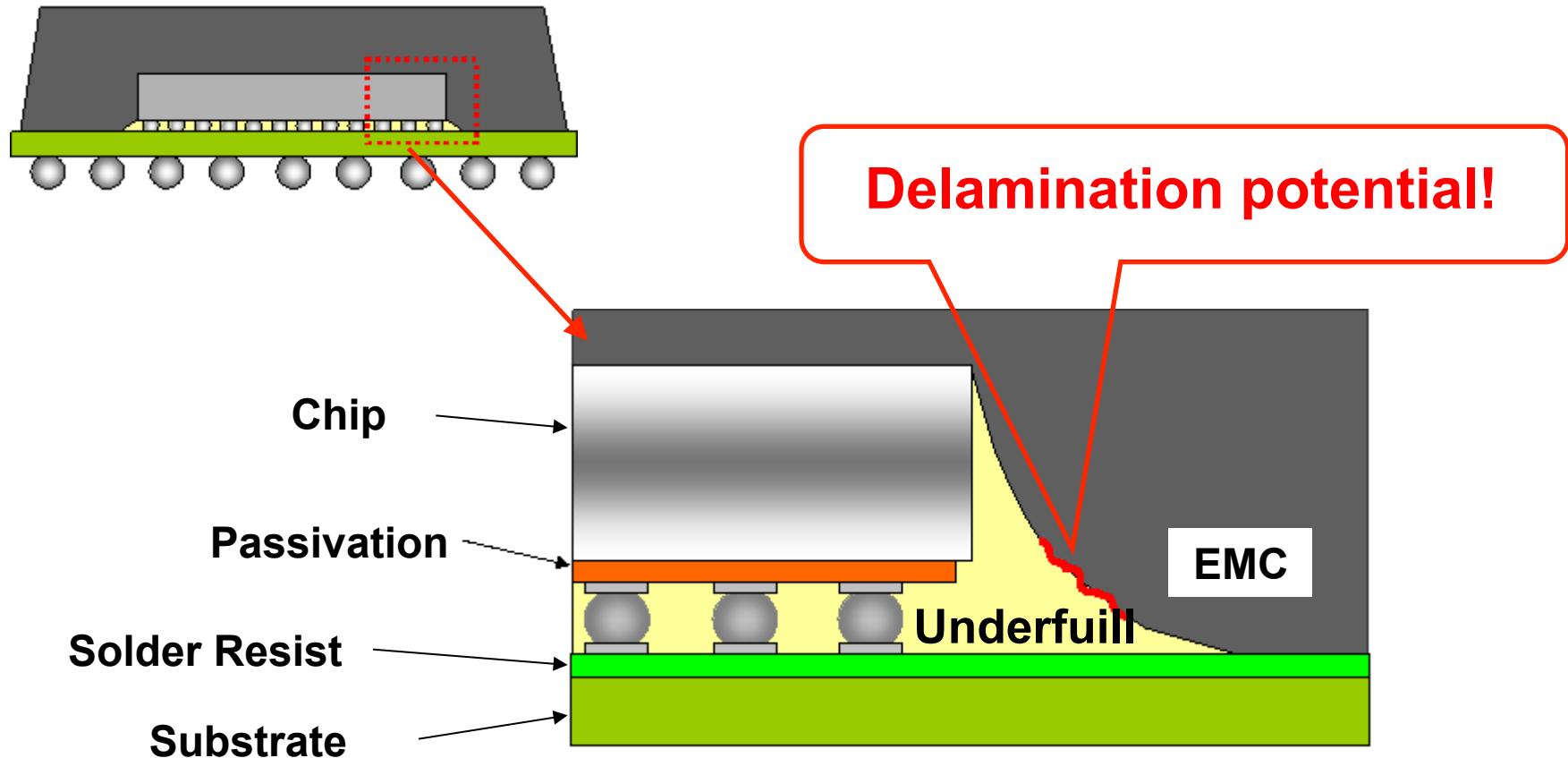

# Pros and Cons for FC structures

| Item      | Solder balls                                                                                                                      | Au stud / plated                                                                                                | Cu pillar with solder cap                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Structure |  <p>Chip</p> <p>Solder ball</p> <p>Substrate</p> |  <p>Chip</p> <p>Substrate</p> |  <p>Chip</p> <p>Cu pillar</p> <p>Solder</p> <p>Substrate</p> |

| UF        | CUF / MUF                                                                                                                         | CUF / NCP / NCF                                                                                                 | CUF / MUF /<br>NCP / NCF                                                                                                                        |

| Pros      | High reliability<br>Existing platform                                                                                             | Less oxidation                                                                                                  | Finer pitch<br>Lower cost                                                                                                                       |

| Cons      | Challenging<br>finer pitch                                                                                                        | Challenging fine pitch<br>Higher cost                                                                           | Difficult filling                                                                                                                               |

➤ To meet higher pin count requirement, more Cu pillar is expected with finer pitch.

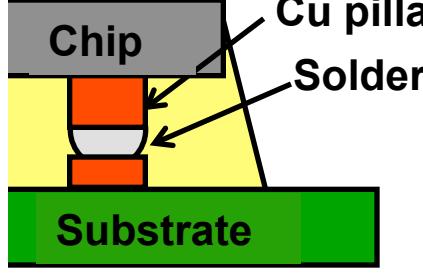

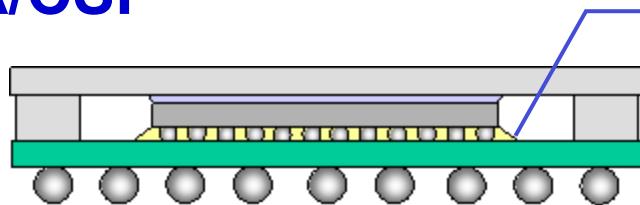

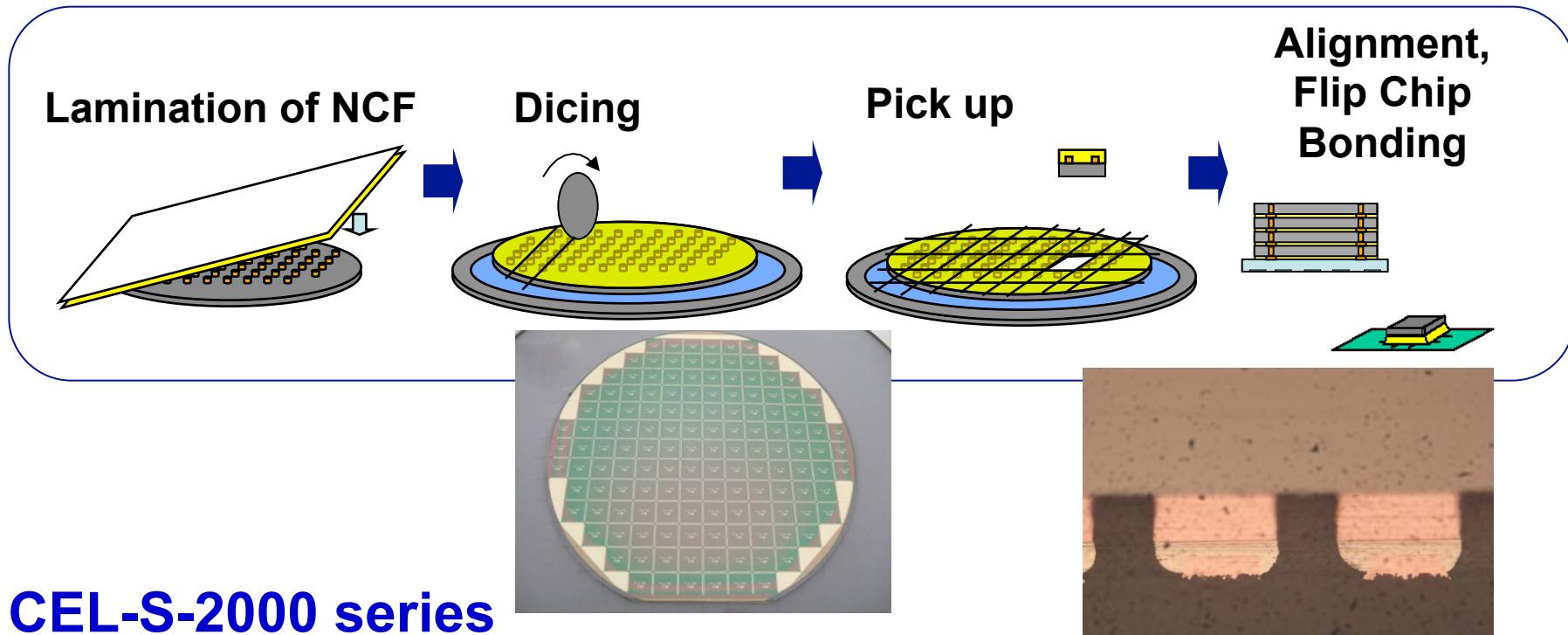

- **Mas Reflow then CUF**

Mass Reflow

- ✓ Substrate is heated to reflow temp

- ✓ Flux residue to cause voids and delamination

- ✓ Stress on low-k

- ✓ Warpage

- ✓ Stress relaxation is after CUF

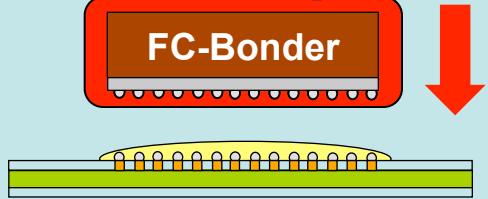

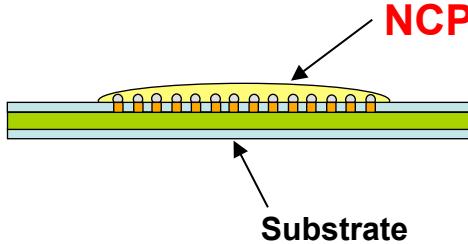

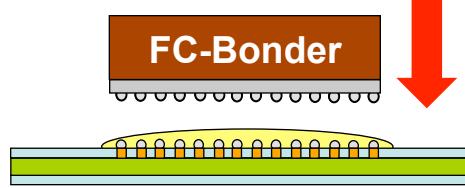

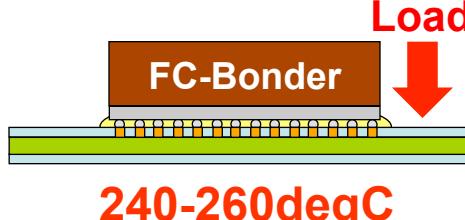

- **Thermal Compression Bonding with NCP or NCF**

FC-Bonder

- ✓ Substrate could be less heated.

- ✓ No additional flux is needed.

- ✓ Instant stress relaxation with underfill

- ✓ Low stresss on low-k

- ✓ Low warpage

➤ **Thermal compression bonding with NCP/F would reduce stress on low-k less than Mass Reflow.**

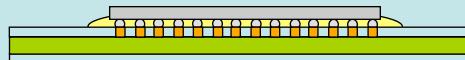

## •FCBGA/CSP

CUF, MUF, NCP, NCF

MUF : Mold Underfill

NCP : Non Conductive Paste

NCF : Non Conductive Film

## •2.5D TSV

CUF, NCP, NCF

## •3D TSV

CUF, NCP, NCF

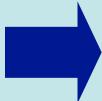

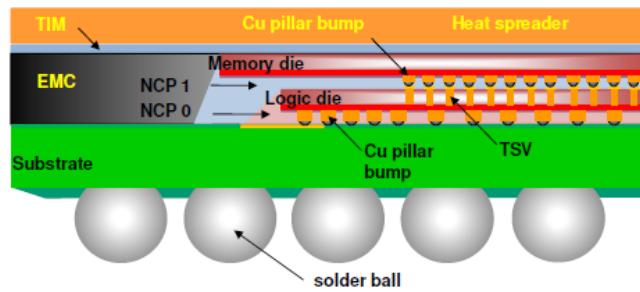

# Examples of NCP for TSV

## •Mobile applications

### Mobile Applications

Wide I/O memory die (~1200ubumps, no TSV)

28nm (Cu pillar, 10um dia. TSV)

Substrate (14 x 14 /12 x 12 mm)

Die 2 Substrate interconnection : TCNCP

Die 2 Die interconnection : TCNCP

Heat spreader attach (exposed die molding) :optional

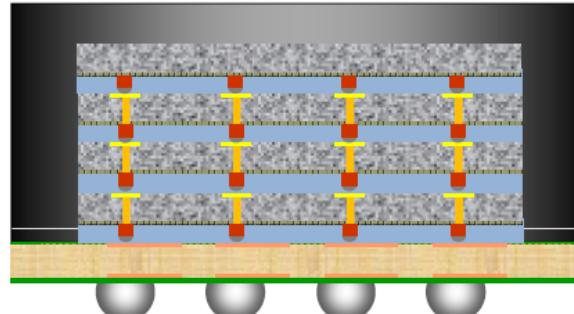

## •Memory stacking

### Process Flow – Memory Stacking

NCP dispensing and TC bonding 1

TC bonding 2, 3 and 4

Mold

Solder ball attach

## ➤NCP x 2 + Mold

## ➤NCP x 4 + Mold

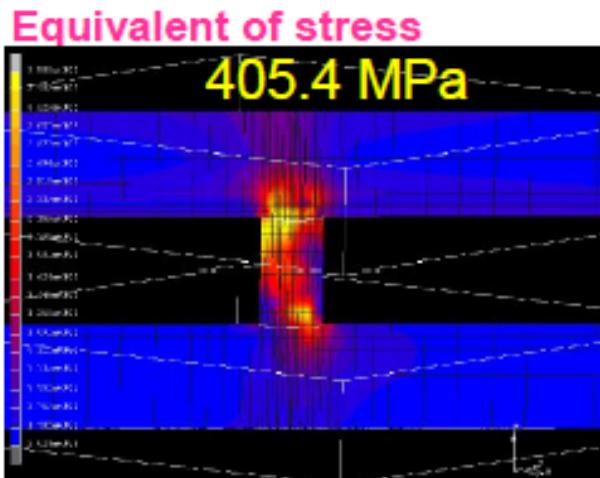

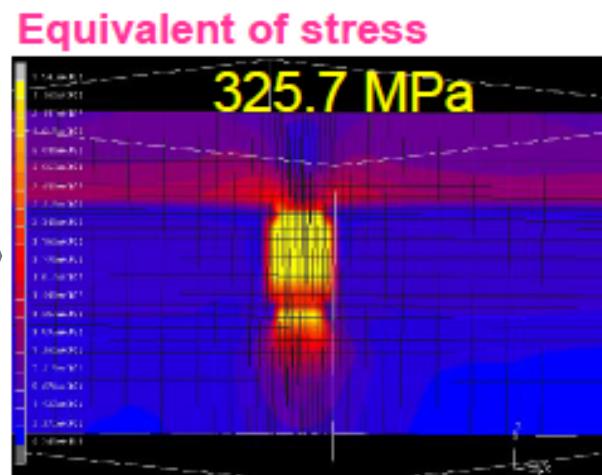

# CUF (Capillary underfill)

## ◆ Stress distribution before underfill

## ◆ Stress distribution after underfill

Underfill

can

reduce

stress

For micro bump & 2.5D

**CEL-C-3730S Narrow gap filling type**

For large die 28nm

**CEL-C-3730S Lower stress type**

- Lower warpage

- Better bump protection

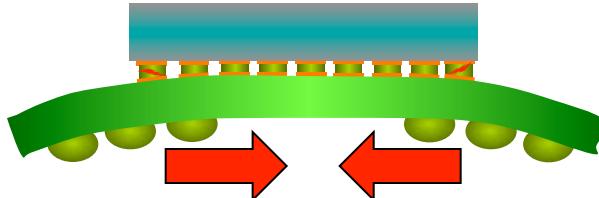

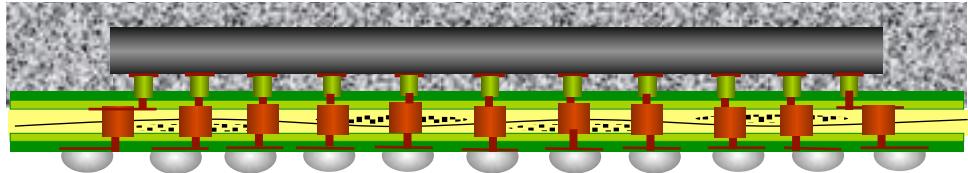

# MUF (Mold underfill)

Overmold and underfill

at the same time

with transfer mold

(exposed die is optional)

## CEL-9700HF&ZHF/9740HF/1800HF series

- Good gap filling by filler top cut and average control

- Warpage control

- Lower material cost than CUF

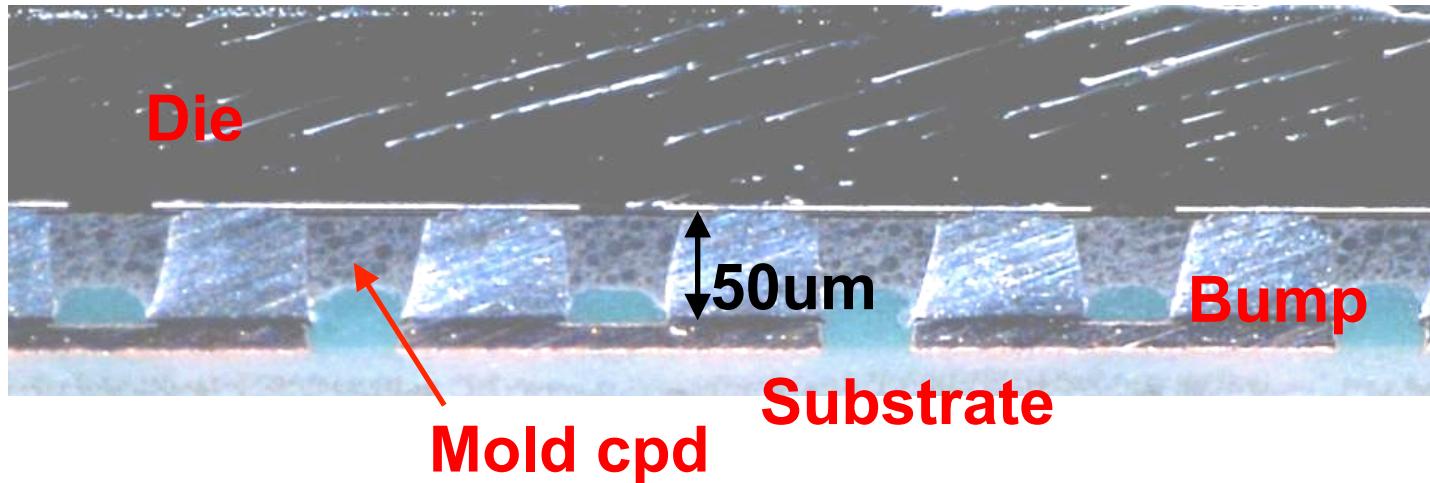

# NCP (Non Conductive Paste)

## CEL-C-8200 series

- Applicable for finer pitch and narrower gap

- Lower stress caused by connection

- Applicable for Cu pillar and TSV

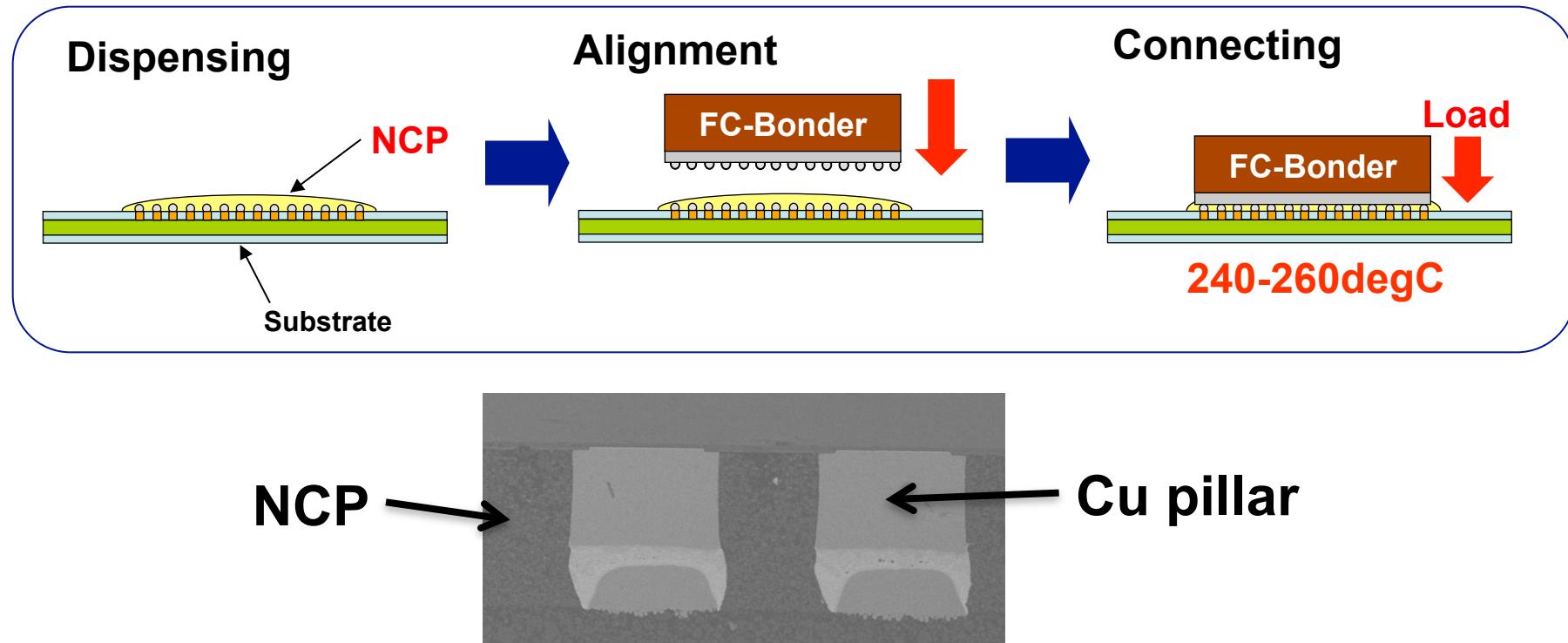

# NCF (Non Conductive Film)

## CEL-S-2000 series

- Applicable for finer pitch and narrower gap

- Lower stress caused by connection

- Applicable for Cu pillar and TSV

- Applicable for wafer base process

- Back grinding compatibility (optional)

# Over molding

- Over molding is optional.

- Appropriate combination of underfill and over molding materials needs to be selected.

- 1. Hitachi Chemical and MSS**

- 2. FC and TSV roadmap and Underfills**

- 3. NCP development**

- 4. Summary**

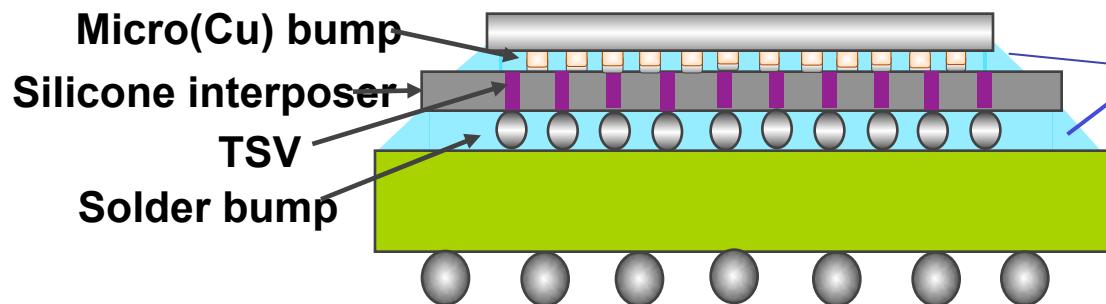

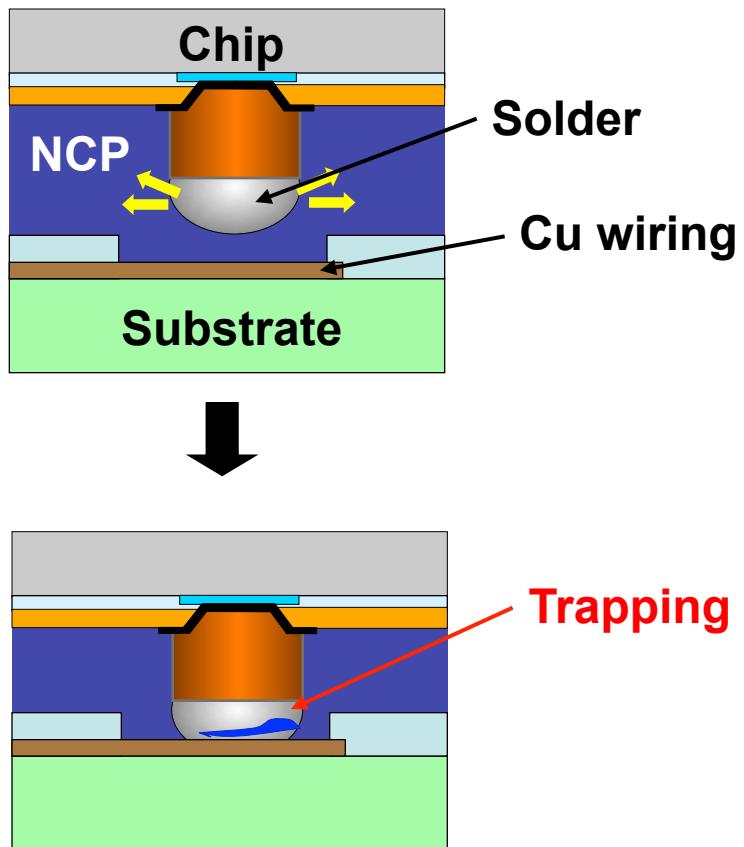

# NCP process and requirements

| Process                                                                                                  | Requirement                                                                                            | NCP Properties                                                                                          |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <b>Dispensing</b><br>   | <ul style="list-style-type: none"><li>▪ Dispensability</li></ul>                                       | <ul style="list-style-type: none"><li>▪ Viscosity</li><li>▪ Thixotropic index</li></ul>                 |

| <b>Alignment</b><br>   | <ul style="list-style-type: none"><li>▪ Wettability</li><li>▪ Voidless</li></ul>                       | <ul style="list-style-type: none"><li>▪ Viscosity</li><li>▪ Thixotropic index</li></ul>                 |

| <b>Connecting</b><br> | <ul style="list-style-type: none"><li>▪ Voidless</li><li>▪ Connectivity</li><li>▪ Curability</li></ul> | <ul style="list-style-type: none"><li>▪ Few volatile</li><li>▪ No trapping</li><li>▪ Gel Time</li></ul> |

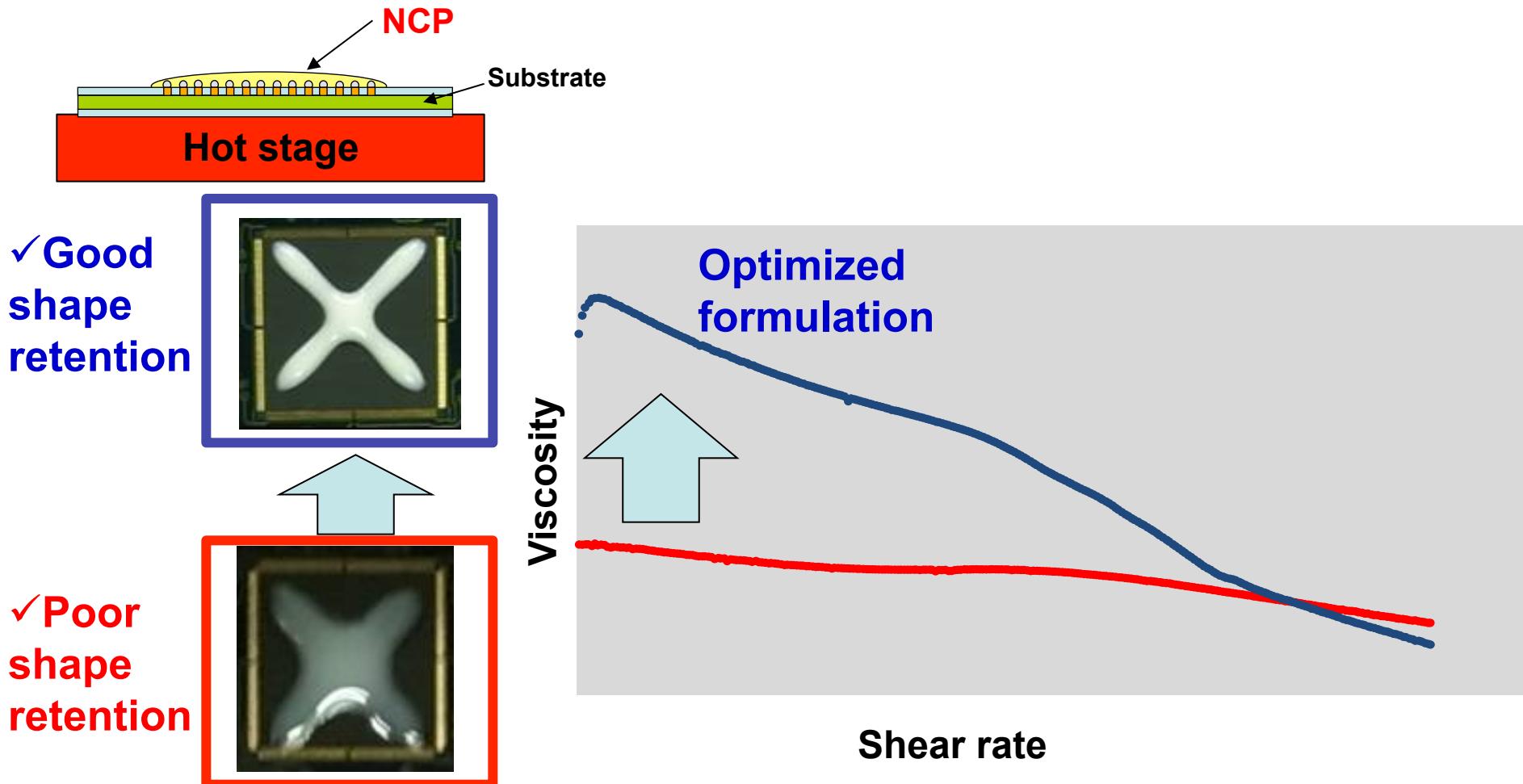

# Shape retention

➤ High thixotropy at hot stage temp is needed to have good shape retention

## Source of voids

1. Outgas

2. Moisture

3. Trapped air

✓ Different types of voids

✓ No voids

➤ Formulation and process needs to be optimized to eliminate voids.

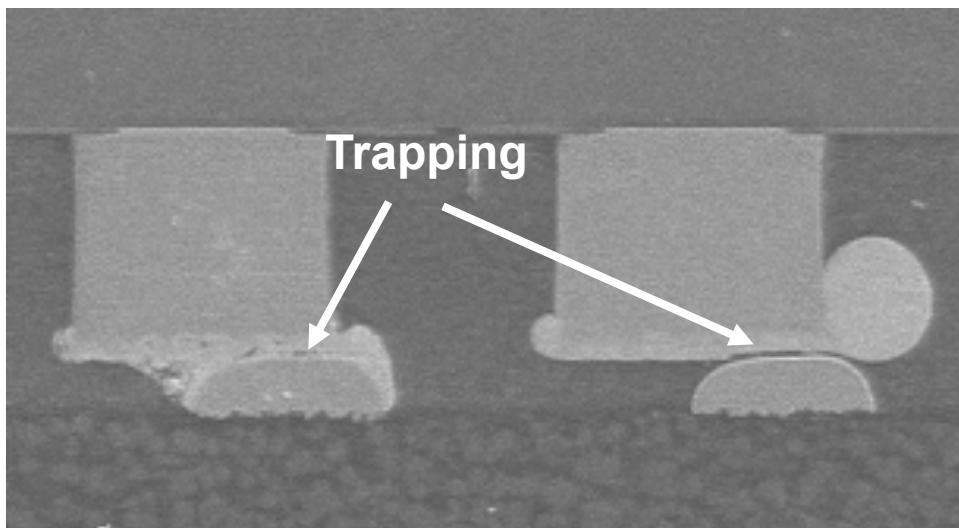

## Trapping mechanism

**Trapping consists of silica mainly.**

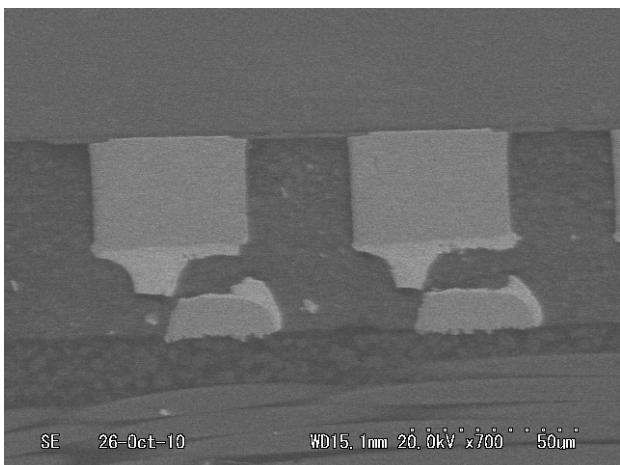

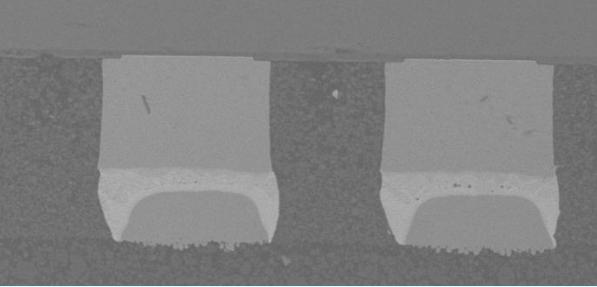

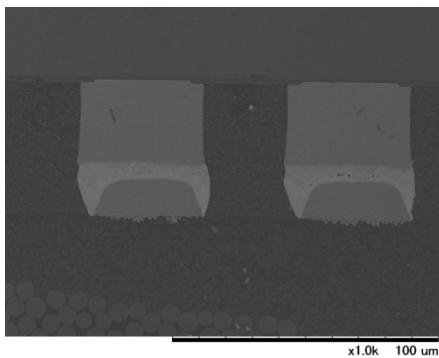

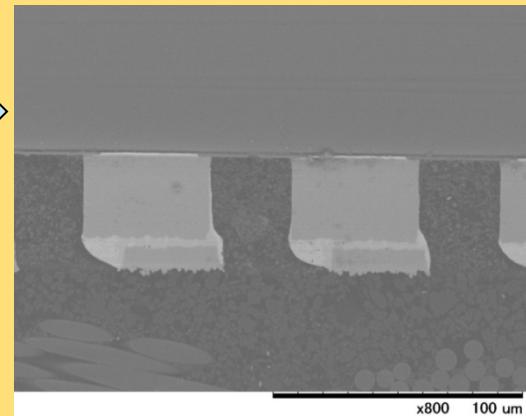

# Connectivity and Trapping

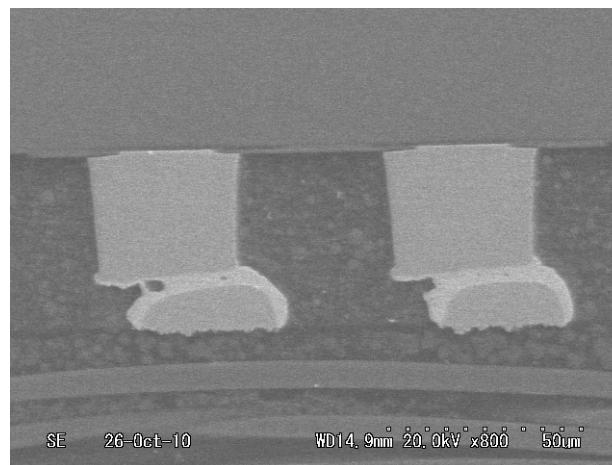

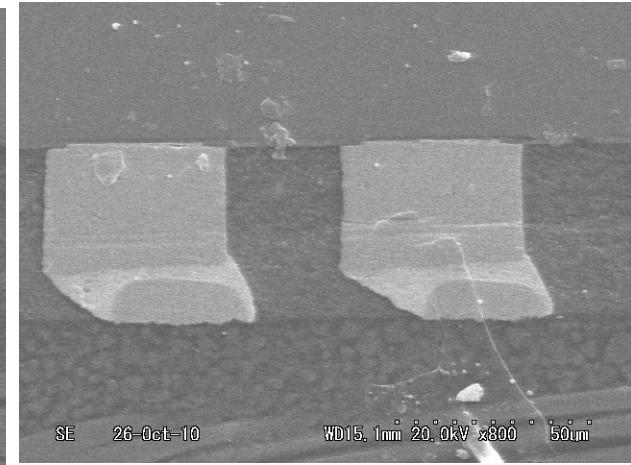

## ➤ Standard CUF

SE 26-Oct-10

WD15, 1mm 20.0kV x700 50µm

## ➤ Old NCP Formulation

SE 26-Oct-10

WD14, 9mm 20.0kV x800 50µm

## ➤ Optimized NCP Formulation

SE 26-Oct-10

WD15, 1mm 20.0kV x800 50µm

✓ **No connectivity due to poor fluxing capability**

✓ **Poor connectivity and trapping**

✓ **Good connectivity and no trapping**

➤ **Formulation selection improved connectivity without trapping thanks to good fluxing capability.**

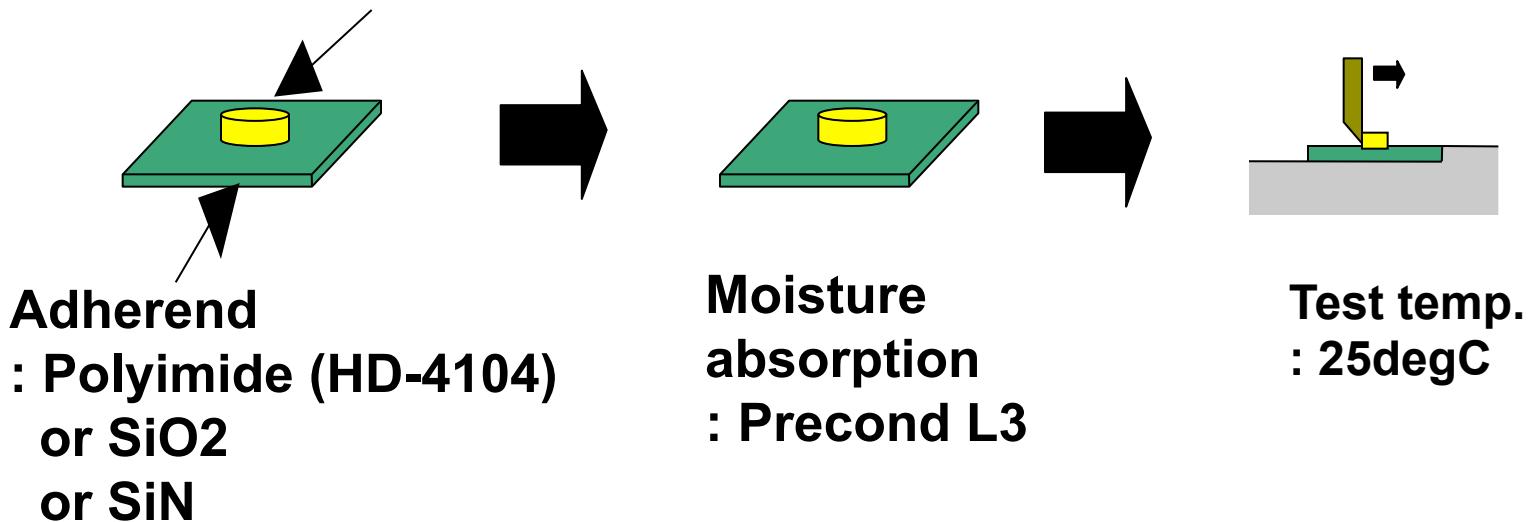

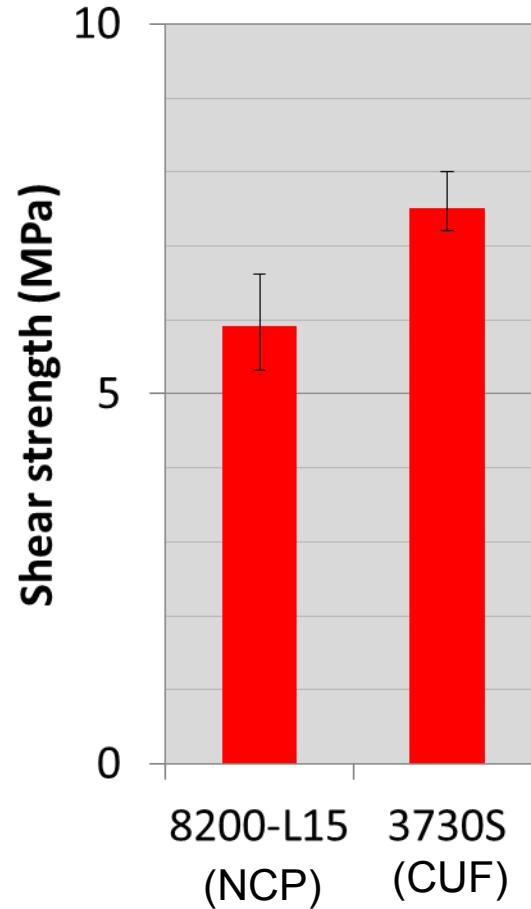

# Shear strength test method

- CEL-C-8200-L15(NCP)

- CEL-C-3730S(CUF)

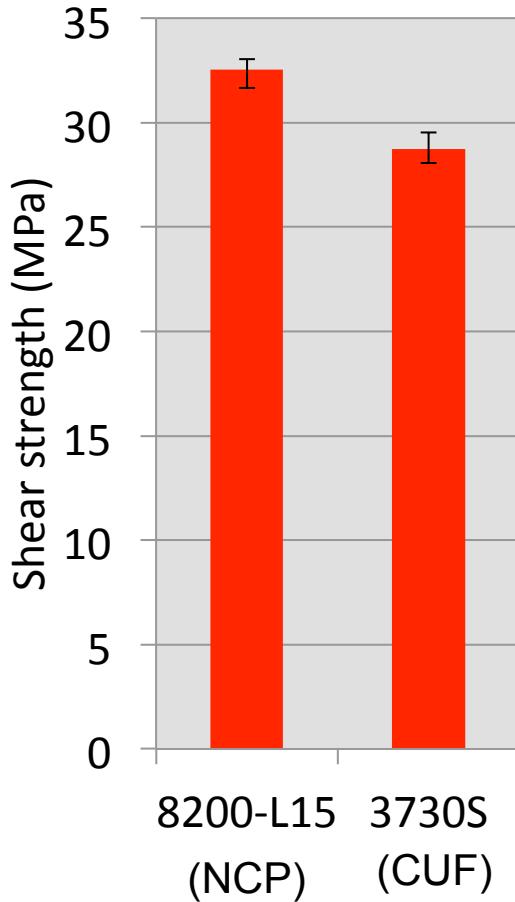

# Shear strength

## Adherend=PI

## Adherend=SiO<sub>2</sub>

## Adherend=SiN

➤CEL-C-8200-L15 showed good adhesion to PI, SiO<sub>2</sub> and SiN.

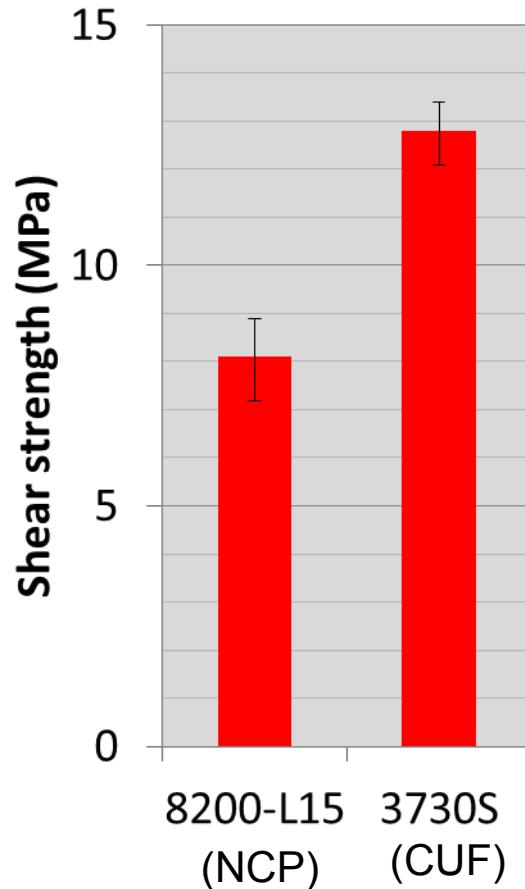

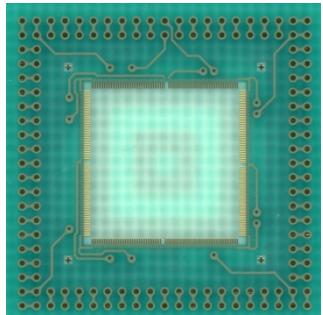

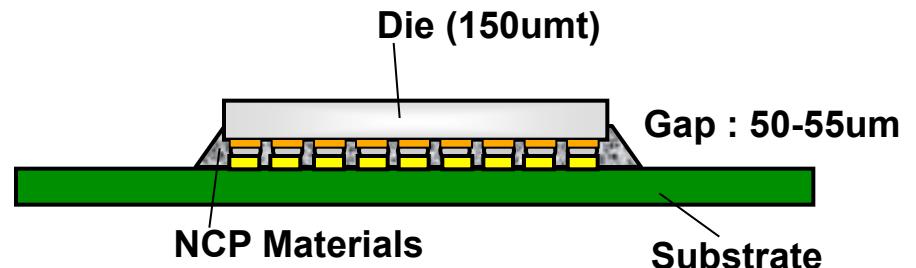

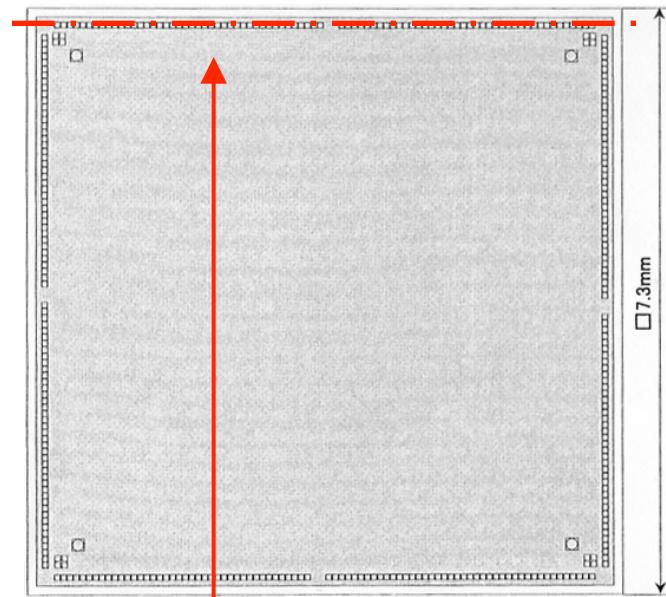

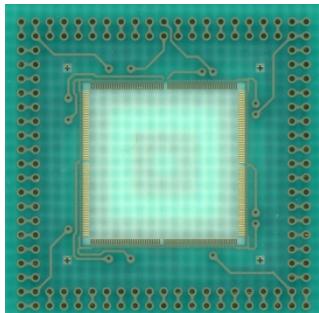

# Specification Substrate & Die

## Specification of Substrate

- Size : 14 x 14mm

- Thickness : 300um

- Core material : E-679FG

- Solder resist : SR7200G(10-15um)

- Bump materials : Cu + Ni(5.0um) +Pd(0.3um) +Au(0.35um)

- Substrate Size : 60mmx140mm

- 9pcs(3X3pcs)x 2blocks

## Specification of Die

- Size : 7.3mm x 7.3mm

- Thickness : 150um

- Bump materials : Cu Pillar(30um) + SnAg(15um)

- Bump pitch : 80um

- Number of pad : 328 (82 x 4 lines)

- Passivation layer : Si3N4

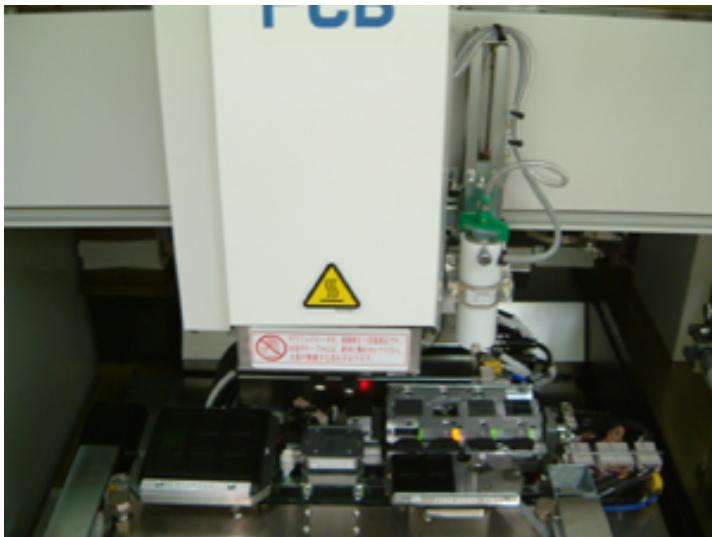

# Flip Chip Bonder

## Flip Chip Bonder Specification

| Item                | Specification                                                 |

|---------------------|---------------------------------------------------------------|

| Substrate Size (mm) | 100mm×100mm max                                               |

| Die Size (mm)       | 3mm~20mm                                                      |

| Accuracy            | ±3um/3σ                                                       |

| Load                | 5N~490N                                                       |

| Temperature         | Max 500degC                                                   |

| Die supply          | <input type="checkbox"/> 2"、 <input type="checkbox"/> 4" Tray |

# Bonding results

| Items        | CEL-C-8200-L15                                                                       |

|--------------|--------------------------------------------------------------------------------------|

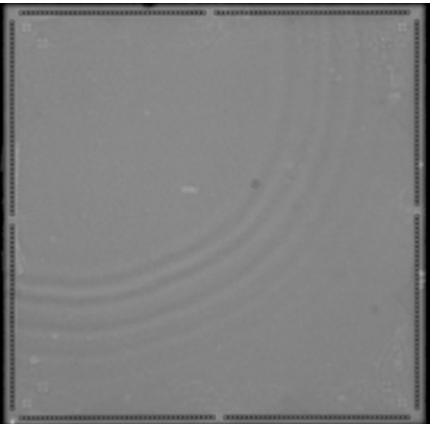

| C-SAM        |    |

| Connectivity | <b>Good</b>                                                                          |

| Trapping     |  |

***No trapping and Good interconnection!***

# Reliability evaluation results

| Items               | Test condition                                                     | CEL-C-8200-L15 |

|---------------------|--------------------------------------------------------------------|----------------|

| MSL                 | <b>Level 3 (30degC / 60%RH / 192h)<br/>IRR 260degC x 5 times</b>   | <b>Pass</b>    |

| TCT                 | <b>Condition B (-55degC ⇄ 125degC)<br/>(air to air each 15min)</b> | <b>1000cyc</b> |

| HAST<br>(unbiased)  | <b>135degC / 85%RH</b>                                             | <b>200h</b>    |

| HAST<br>(with bias) | <b>135degC / 85%RH / 1.3V</b>                                      | <b>200h</b>    |

# Reliability evaluation results

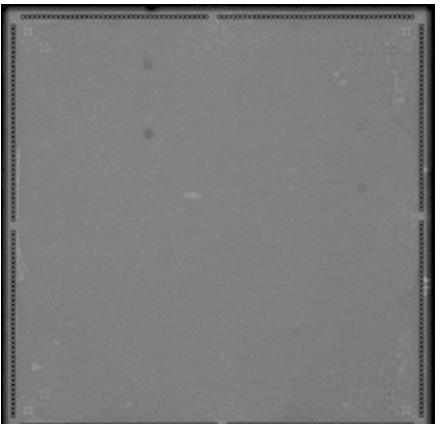

| Item      | SAM                                                                                 |

|-----------|-------------------------------------------------------------------------------------|

| Time 0    |   |

| After MSL |  |

➤C-8200-L15 showed good performance of MSL.

# Influence of pad finish

## ➤ Cu/Ni/Pd/Au

✓ Good connection

## ➤ Cu-OSP (Cu-Organic Solderability Preservative)

✓ Worse connection

Optimization

✓ Good connection

- Cu-OSP is more difficult to have good connection

- CEL-C- 8200-L15 showed good connection even with Cu-OSP

- 1. Hitachi Chemical and MSS**

- 2. FC and TSV roadmap and Underfills**

- 3. NCP development**

- 4. Summary**

- 1. MSS (Material System Solution) would be needed to meet requirements of challenging advanced packages.**

- 2. NCP (Non Conductive Paste) could be potential solution for fine pitch and 28nm device at Flip chip and TSV packages.**

- 3. Hitachi Chemical developed NCP material, CEL-C-8200-L15 with good shape retention, good underfilling and good connectivity.**

- 4. Cu-OSP is more difficult to have better connection.**

*Thank you for your attention*

*Please contact

Hidenori Abe*

*[abe@hitachi-chemical.com](mailto:abe@hitachi-chemical.com)*

**Hitachi Chemical**

*Working On Wonders*

◎日立化成工業株式会社

(製品領域) (エレクトロニクス関連製品) (機能性材料関連製品)

<http://www.hitachi-chem.com>