# Packaging Tradeoff for SIP Integration Targeting High Speed PAM-4 **Applications**

Haentjens,  $B^1$ . Desruelles,  $G^1$ . Chrétien,  $G^1$ . Leborgne,  $A^1$ . Haentjens,  $Y^1$ . Dupuy,  $J^2$ . Jorge,  $F^2$ . Konczykowska,  $A^2$ . Beauvisage,  $I^3$ . Delleme,  $R^3$ . Martin,  $D^3$ . Bila,  $S^4$ . Frigui,  $K^4$ . Ngoho,  $S^4$ . Frigui,  $B^5$ . & Mardoyan, H<sup>6</sup>.

<sup>1</sup>Vectrawave, rue de la croix blanche, 78350, LES LOGES EN JOSAS.

<sup>2</sup> III-V LAB, route de nozay, 91460, MARCOUSSIS.

<sup>3</sup> Egide, Site Industriel du Sactar, 84500, BOLLENE.

<sup>4</sup> University XLIM, 123 rue Albert Thomas, 87060, LIMOGES. <sup>5</sup> CISTEME, Technopole ESTER, 12 rue Gémini, 87068, LIMOGES.

#### Abstract

High speed transmission systems using optical fiber are now focusing on 4-level PAM (Pulse Amplitude Modulation) format. This is requesting ultra-wideband electronic system in package, with a high phase linearity behavior in order to drive the electro-optical modulators. Moreover, new power DAC (Digital to Analog Converter) dies, are now available to generate up to 56 GBd, 4-level PAM signals, and providing 4V<sub>pp</sub> of differential output amplitude swing. High frequency studies have been pursued to provide system integration in a BGA (Ball Grid Array) package. The BGA package transitions optimization and the configuration of multi-lines carriers, becomes a key step in the design flow. In this paper, some steps of the design, manufacturing process of the SIP (System In Package) and its demonstration board are proposed. The choices of the package, the thermal management, the clock management function are studied according to the final environmental constraint of the SIP. The data lines phase skew are analyzed with the support of EM (Electro Magnetic) simulations to better understand the potential impact on the output eye. Finally, the BGA package transition, simulated and measured results are compared, from DC up to 40 GHz and the measured SIP output, 4 levels, 56GBps eye diagram is presented.

#### **Kev words**

BGA, Package, SIP, PAM-4, Optical Transmitter

#### I. Introduction

Today, Internet transmission is looking for secure link. High bit rate transmission system needs to meet performances, be cost effective and ensure up to 100 Gb/s on a single carrier. Multi-level format are getting more and more interesting and the main reason is that it helps to conserve a compact electrical signal bandwidth. The power DAC becomes a coder which generates the high speed multi-level format, feeding the EOM (Electro-Optical-Modulator) driver input by staying in the linear regime. During first experimentations on DAC system, it has been observed that it's very sensitive to high frequency mismatch, insertion losses and of course non-linear effect. That is the main reason why the HENIAC French project has focused on studying and developing packaging solutions for new very high speed DAC circuits realized in

an indium phosphide (InP) double heterojunction bipolar transistor (DHBT) technology and leveraging the Power-DAC concept [1]. This paper presents the microwave approach used to integrate a high speed telecommunication system in a small form factor, hermetic package. It describes research and development efforts to integrate Power-DAC functions into high speed packages. The work has been divided into three parts. Each part includes an SIP development. The first 'SIP\_A' is fully coaxially equipped and implements several chips to realize an overall 2-bit Power-DAC function [2, 3]. The second 'SIP B' and the third 'SIP C' include all RF inputs in BGA form, while RF outputs stay in coaxial connector form, in order to stay compatible with the standard EOM coaxial inputs. The second SIP includes two 2-bit-Mux-Power-DAC functions [4] and the third SIP includes two 3-bit-Mux-Power-DAC

<sup>&</sup>lt;sup>6</sup> Alcatel Lucent Bell Laboratories, route de villejust, 91620, NOZAY.

functions [5]. These SIP are intended to enable next generation 400-Gb/s and 1-Tb/s optical communications systems [6]. Discussion on SIP\_C characterization is not included here and will be published later when more developmental work is completed. For hermetic reasons, the package has been studied and developed by considering HTCC (High Temperature Co fired ceramics) techniques. Evaluation boards are developed using PCB (Printed Circuit Board).

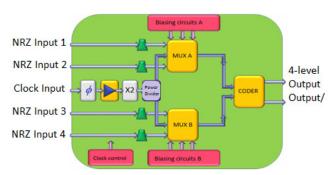

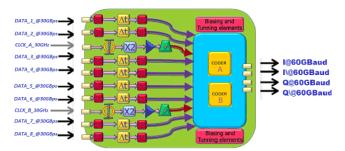

#### II. SIP A

This SIP\_A present four independent NRZ (Non Return to Zero), data access working up to 28GBps. These input accesses are internally pair multiplexed, using the 'MUX-A/B' multiplexer chip to provide two 56GBps NRZ data bit rate lines. Then these two NRZ 56GBps data lines are combined using the 'CODER' electronic coder to provide the 4 levels, 56GBps output data shape. The chip associations, obliges particular clock management function integration in order to drive each of the 2 multiplexers chips clock access with synchronization from 28GHz to 32GHz. Herein synoptic of the SIP\_A is described in the Fig.1.

Figure 1:SIP\_A Synoptic

Considering the complexity level of the development, it has been discussed to demonstrate the 'clock management' function capacity before integrated it in the package. Also, because of the synchronization need between the two multiplexer chips, it has been choose to introduce crossing between two high speed propagation supports. This crossing structure is described in the Fig.2. It has been decided to integrate, in the same package, the coding function and the clock management function. We choose to define the clock input frequency access at the bit rate half value. By this way, the phase shifter function is getting more feasible using GaAs MMIC in the 14GHz to 16GHz bandwidth than in the 28GHz to 32GHz bandwidth. Also, the impact of some clock residual signal propagation, in the used common substrate, or directly, in the package space, can be better reduce at higher wavelength. Considering phase shifter output amplitude variation, one side depending on the working frequency and the other side, depending on the phase control configuration. We decided to insert, an amplifier between the phase shifter and the frequency multiplier circuits. The amplifier is configured to work in compression regime as a limited function. By this way, the amplitude at the frequency multiplier input is less dependent on the phase state configuration. Finally, this is helping to reach low ripple on the integrated 'clock management' function frequency bandwidth from 28GHz to 32GHz.

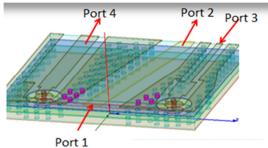

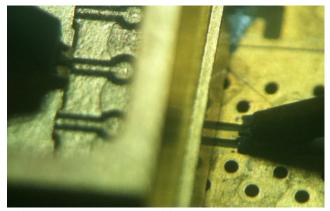

We found that, the integration of components coming from different nature (MMICs, OFN, connectors...) needs a tradeoff between technology compatibility and microwave performance. For this reason, we have chosen to use a common substrate to interconnect all devices in the SIP\_A. This substrate is compatible with SMD (Surface Mount Devices) techniques and bonding process, by this way, the chips output access is directly bonded to the transmission line which is, also, directly brazed to the SIP A output coaxial connector pin. We choose to use an eight layers PCBs substrate composed by three 'RO4350' (Rogers) top layers and five 'FR4' (Flame Retardant 4) DC routing down layers. This was done to ensure the performance of the crossing multilayer HF transition. This 3D simulation model structure is presented in the Fig.2 and this photography structure is presented in the Fig.3.

Figure 2: Multilayer HF transition in SIP\_A simulation model.

Figure 3: Multilayer HF transition in SIP\_A structure photography.

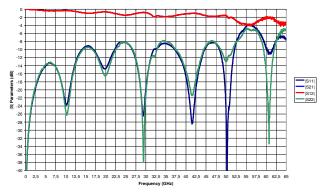

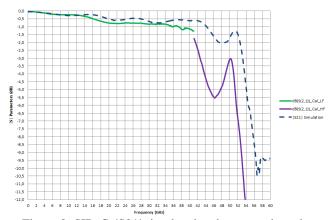

The Fig.4. presents the obtain |S43| simulated and measured results of the structure presented in Fig.2 and in Fig.3. The insertion losses are about 2dB at 50GHz and the input and output return losses stay under -8dB from DC to 50GHz. These results are sufficient for the targeted applications and provide encouraging results for future development on wide bandwidth multilayer transition.

Figure 4: On probes, |S| parameters measurement results of the structures presented in the Fig.2 and Fig.3.

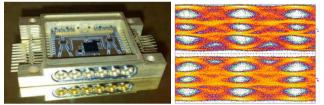

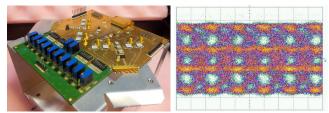

The Fig.5.a and Fig.5.b shows respectively, the SIP\_A photography and 56GBps measured output eye diagram.

Figure 5: 'a': SIP\_A photography and 'b': 56GBps Output Eye diagram, 500mV/div, 5ps/div.

# III.SIP B

The function demonstrated in the Fig.1 has been fully integrated in a single coder chip. This chip has been, dually integrated in the SIP\_B in order to emulate a 200GBps transmission system. This SIP\_B presents eight independents, BGA, data access working up to 28GBps NRZ and two independents, BGA, clock access working up to 28GHz. These data inputs access are combined 4 by 4 using two identical chips (CODER A/B, see Fig.6), to provide two pair of 4 levels, 56GBps output data shape. The BGA package has been studied in order to include a GLIPTOP heat sink located directly under the chips bottom. By this way, thermal dissipation is improved in comparison with a multilayer ceramic ground plane.

The consequent numbers of chips data inputs, requires a tradeoff for interface substrates. For the same reason mentioned at the SIP\_A level, we decided to conserve PCB substrates for the output transmission lines, but we add thin film interfaces substrates in order to ease the five high frequency input access routing per chips. The thin film substrates are made using Alumina in  $127\mu m$  of thickness. The minimum line width used is  $100\mu m$  and the minimum gap used is  $50\mu m$ . Grounded conductive vias are used to improve the shielding guide of each transmission lines. 3D-EM simulations have been pursued in order to obtain low insertion losses as 0.5dB up to 40GHz, and to limit the phase difference between each data lines to 10ps.

An evaluation board is used to report the BGA package of the SIP\_B. This board includes delay lines on each data inputs to ensure the required phase skew optimization in order to avoid the potential output eye diagram phase distortion. It's also includes clock management function in order to drive each coder clock independently. The clock management function has been fully achieved by the use of SMD device reported on the evaluation board. This allow the phase control of the 28GHz-32GHz clock signal, at the input of the SIP\_B, BGA package by tuning a trimmer on the evaluation board. The synoptic of the SIP\_B is described in the Fig.6.

Figure 6:SIP\_B Synoptic

Thanks to differential outputs available at the delay lines level. Using an embedded GPPO SMD connector, it has been very helpful to monitor the phase of each line during the measurement. The Fig.7.a and Fig.7.b shows respectively, the SIP\_B photography and 56GBps measured output eye diagram.

Figure 7.a: SIP\_B photography and figure 7.b: 56GBps Output Eye diagram, 300mV/div, 10ps/div.

# **IV. SIP-C: BGA Transition**

The SIP\_C BGA transition photography is presented on the Fig.8. The HTCC BGA package is empty and reported on a PCB test substrates by solder operation. Then the probes (ACP40), with a 400µm pitch are used to do the CAL\_LF measurements (green curves) using TRM (Transmission Reflective Match) technique. The probe connected to the VNA port 1 is placed inside the package. The probe connected to the VNA port 2 is placed outside the package, at the PCB level. For CAL\_HF measurements (purple curves), the same procedure has been followed to complete measurements from 41GHz to 60GHz.

Figure 8:SIP\_C, BGA transitions on probes measurement

The Fig.9 presents the obtain |S21| simulated and measured results of the structure presented in Fig.8. The insertion losses are decreasing continuously considering the frequency increase to 1.25dB at 41GHz. This measure results represents 0.03048dB/GHz.

Figure 9: SIP\_C, |S21| simulated and measured results

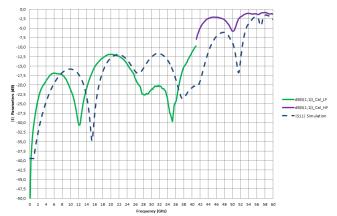

The Fig.10 presents the obtain |S11| simulated and measured results of the structure presented in Fig.8. The input return losses stay under -12dB from DC to 40GHz.

Figure 10: SIP\_C, |S11| simulated and measured results

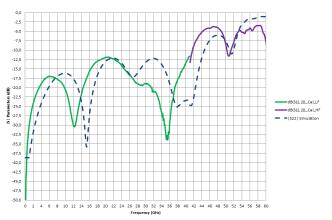

The Fig.11 presents the obtain |S22| simulated and measured results of the structure presented in Fig.8. The output return losses stay under -12dB from DC to 41GHz.

Figure 11: SIP\_C, |S22| simulated and measured results

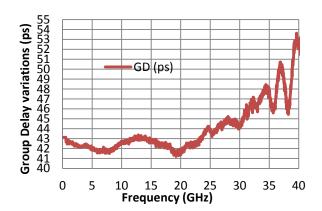

The Fig.12 presents the measured group delay variations of the structure presented in Fig.8. The group delay variations are about 2,5ps from DC to 25GHz. After, a positive 10ps deviation can be observed through 40GHz.

Figure 12: SIP\_C, GD21 measured results

# V. Conclusion

A new design of BGA transition for 'SIP\_C' has been studied, simulated and measured. The proposed structure is based on a HTCC technology. Good correlations have been demonstrated between the measurements and the obtained simulation results from DC, up to 40GHz.

The 'SIP\_B' study demonstrated the technical tradeoff by using thin film technology substrate for high number of chips input HF access and using a PCB substrate for linking a reasonable number of two output access.

The simulated and measured results of the 'SIP\_A' study demonstrated that using a common PCB substrate to link high speed function chips with a limited number of three HF accesses, in a same package help to combine advantages of SMD and bonding techniques over 56GBps. Also, high frequency, multilayer transitions in PCB can help crossing data transmission lines and clock lines with an operating bandwidth of 50GHz.

High speed multiple DAC functions integrated in BGA packages are new considerations, which greatly contributed for future high speed optical network improvement. We are currently working on SIP\_C demonstration and planning to deliver demonstration sets.

### Acknowledgment

This research and development work has been supported by the French National Research Agency (ANR), through HENIAC project under contract n° 11 INFR 006 01.

Particular acknowledgments are presented to our customer Alcatel Lucent Bell Labs France.

#### References

- [1] Konczykowska, A.; Dupuy, J.-Y.; Jorge, F.; Riet, M.; Moulu, J.; Nodjiadjim, V.; Berdaguer, P.; Godin, J.; , "42 GBd 3-bit power-DAC for optical communications with advanced modulation formats in InP DHBT," *Electronics Letters* , vol.47, no.6, pp.389-390, March 17 2011

- [2] Godin, J.; Nodjiadjim, V.; Riet, M.; Berdaguer, P.; Drisse, O.; Derouin, E.; Konczykowska, A.; Moulu, J.; Dupuy, J.-Y.; Jorge, F.; Gentner, J.-L.; Scavennec, A.; Johansen, T.; Krozer, V.; , "Submicron InP DHBT Technology for High-Speed High-Swing Mixed-Signal ICs," Compound Semiconductor Integrated Circuits Symposium, 2008. CSICS '08. IEEE , vol., no., pp.1-4, 12-15 Oct. 2008

- [3] Godin, J.; Konczykowska, A.; Dupuy, J.-Y.; Jorge, F.; Riet, M.; Moulu, J.; Nodjiadjim, V.; Berdaguer, P.; Blache, F.; Gnauck, A.; , "InP DHBT Very High Speed Power-DACs for Spectrally Efficient Optical Transmission Systems," Compound Semiconductor Integrated Circuit Symposium (CSICS), 2011 IEEE , vol., no., pp.1-4, 16-19 Oct. 2011

- [4] J. Godin, J.-Y. Dupuy, F. Jorge, F. Blache, M. Riet, V. Nodjiadjim, P. Berdaguer, B. Duval, A. Konczykowska, "InP DHBT Mux-

- Drivers for Very High Symbol Rate Optical Communications", in Proc. Compound Semiconductor Integrated Circuit Symposium (CSICS), 2014 IEEE , 19-22 Oct. 2014

- [5] Konczykowska A., Jorge F., Dupuy J.-Y., Riet M., Nodjiadjim V., Aubry H., Adamiecki A., "84-GBd (168-Gb/s) PAM-4 3.7-Vpp Power DAC in InP DHBT for short reach and long haul optical networks", accepted for publication in a forthcoming issue of Electronics Letters, IET, 2015.

- [6] Bertran-Pardo, O.; Renaudier, J.; Mardoyan, H.; Tran, P.; Rios-Muller, R.; Konczykowska, A; Dupuy, J.-Y.; Jorge, F.; Riet, M.; Duval, B.; Godin, J.; Randel, S.; Charlet, G.; Bigo, S., "Transmission of 50-GHz-spaced single-carrier channels at 516Gb/s over 600km," Optical Fiber Communication Conference and Exposition and the National Fiber Optic Engineers Conference (OFC/NFOEC), 2013, vol., no., pp.1,3, 17-21 March 2013