# Heat Sink Induced Thermo-Mechanical Joint Strain in QFN Devices

Gerard McVicker, Vijay Khanna, and Sri M. Sri-Jayantha IBM T.J. Watson Research Center 1101 Kitchawan Road Yorktown Heights, NY 10598 Ph: 914-945-3388; Fax: 914-945-4219

Email: gvicker@us.ibm.com

## Abstract

A Blade Server System (BSS) utilizes Voltage Regulator Modules (VRM), in the form of Quad Flat No-Lead (OFN) devices, to provide power distribution to various components on the system board. Depending on the power requirements of the circuit, these VRM's can be mounted as single devices or banked together. In addition, the power density of the VRM can be high enough to warrant heat dissipation through the use of a heat sink. Typically, during field conditions (FC) the BSS are powered on and off up to four times per day, with their ambient temperature cycling between 25°C and 80°C. This cyclical temperature gradient drives inelastic strain in the solder joints due to the coefficient of thermal expansion (CTE) mismatch between the QFN and the circuit card. In addition, the heat sink, coupled to the QFN and the circuit card, can induce additional inelastic solder joint strain, resulting in early solder joint fatigue failure. To understand the effect of the heat sink mounting, a FEM (Finite Element Model) of four QFN's mounted to a BSS circuit card was developed. The model was exercised to calculate the maximum strain energy in a critical joint, due to the cyclical straining, and the results were compared for a QFN with and without a heat sink. It was determined that the presence of the heat sink did contribute to higher strain energy and therefore could lead to earlier joint failure. While the presence of the heat sink is required, careful design of the mounting should be employed to provide lateral slip, essentially decoupling the heat sink from the OFN joint strain. Details of the modeling and results, along with DIC (Digital Image Correlation) measurements of heat sink lateral slip, are presented.

## **Key words**

Heat sink mount, solder strain, lead-free solder, FEM modeling, thermal cycling

## I. Introduction

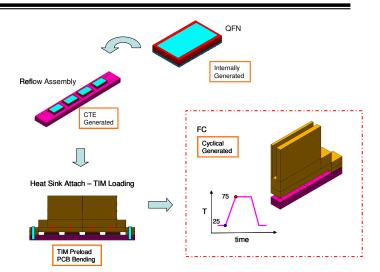

In modern electronic applications, the electronic board assemblies are required to pass industry reliability tests and customer specifications. At the core of these reliability specifications, are the solder interconnects (solder joints) that provide the mechanical and electrical interoperability. Reliability of the devices requires the joints to survive thermal assembly processing, shock events resulting from shipping and handling, high and low cyclical vibration, and field induced thermal cycling, all of which contribute to strain events that can individually or collectively lead to joint cracking and/or fatigue failure. Fig. 1 shows the typical thermal strain contributors incurred through the life of an electronic module. The FC mimics the thermal induced strain due to power on/of thermal cycling.

Figure 1. Process-induced strain contributors.

Recently, due to the ROHS (Restrictions on Hazardous Substances) regulations on the use of SnPb (Tin-Lead) alloys as interconnects, the electronics industry has had to seek alternatives made from less hazardous metals. The solder metallurgy of choice to replace SnPb are alloys of SnAgCu (Tin/Silver/Copper,) often referred to as SAC alloys. However, due to their lower ductility and higher stiffness, challenges in interconnect strain failures are being realized. Emerging as a low cost front runner for SAC is the alloy SAC305 which has a composition of 96.5% Sn, 3% Ag, and 0.5% Copper.

Another shift in modern electronic assemblies is the on board distribution of power levels driving various circuits. There is a growing use of QFN based VRM's to regulate this discrete on board power delivery. These QFN devices, which are of fingernail scale, utilize a solder joint geometry which is paddle shaped with a high planar to height aspect ratio. Unlike a typical barrel shaped solder connection, these joints experience higher strain during thermal cycling, which can lead to joint failure.

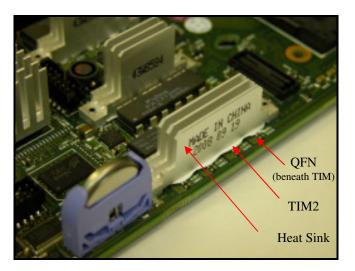

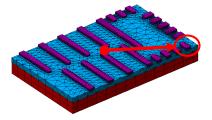

Figure 2. Heat Sink mounted over four QFN modules.

In addition, due to the QFN high heat load, heat sinks are often employed to dissipate the thermal energy. Fig. 2 shows an in-situ picture of four in-line QFN devices on a circuit board with a heat sink and thermal interface material. Unfortunately, certain methods employed to mount the heat sinks securely to the board assemblies can contribute to increased strain loading on the solder interconnects. An example of this mounting is a low cost in-line riveting process which rigidly constrains the heat sink to the PCB.

A rigidly attached heat sink can increase the amount of solder strain realized during thermal cycling causing early failure. This paper presents a FEM (Finite Element Model) exercise to understand the strain energy resulting from the heat sink method of assembly. The model uses a power on/off field condition (FC) to drive the thermal strain energy, resulting from the CTE mismatch of the various components. The FC used consisted of 4 cycles per day with 270 minutes dwell times at hot (75°C) and cold (25°C) temperatures with linear ramp times of 45 minutes.

## **II.** Material Properties

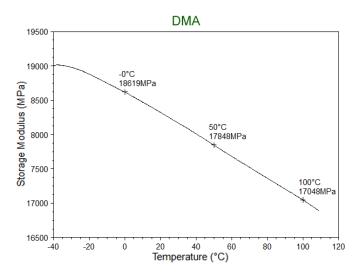

To model the thermal mechanics of the system, the elastic-plastic modulus and creep properties of the solder are required in addition to the elastic properties of the QFN and FR4 printed circuit board. In the case of the FR4 circuit board, a section representing the foot print of the heat sink was extracted and the effective storage modulus and CTE were measured using a DMA (dynamic mechanical analyzer) & TMA (thermo mechanical analyzer) respectively. Fig. 3 shows the results of the DMA modulus measurement.

Figure 3. PCB Modulus measurement

For the QFN, a detailed understanding of the assembly was acquired and materials properties were assigned. In one region of the QFN, effective material properties of the Cu-Fe lead frame and surrounding polymer encapsulation was derived, based on volumetric proportions. Also, the overall CTE of the QFN device was measured using a DIC tool and correlated to a discrete QFN FEM model. Model results were very comparable to the measured results and the discrete material definition was utilized in subsequent modeling exercises. The TIM2 material was a low cost material which allows lateral compliance, without contributing to joint strain. No other TIM's were considered.

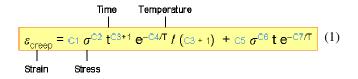

A Time Hardening Creep model for SAC305 was used to analyze the creep behavior of the solder interconnects. ANSYS<sup>TM</sup> FEA software incorporates the constituent model into the analysis using seven constants reported in Table I. Table I. Time Hardening, Creep Model. [1]

Time Hardening Creep Model

|              | $C_I$     | C2    | Cg+1   | C4      | C <sub>5</sub> | $C_{\delta}$ | C7        |

|--------------|-----------|-------|--------|---------|----------------|--------------|-----------|

| Sn3.8Ag0.7Cu | 1.134E-4  | 4.577 | 0.5136 | 4886.5  | 5.05E-7        | 11.521       | 2.26E+4   |

| Sn1.0Ag0.5Cu | 1.533E-5  | 1.542 | 0.3002 | 277.2   | 1.36E-6        | 14.176       | 1.55E+4   |

| Sn3.0Ag0.5Cu | 2.244 E-4 | 0.613 | 0.4722 | 531.221 | 2.32E-4        | 1.0268       | 1.5509E+4 |

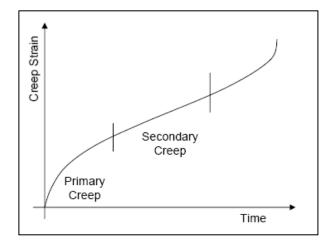

In previous modeling of SnPb solder creep the ANAND [2] viscoplastic model has been widely used, as well as other constitutive models. However these models may not capture the primary creep contribution shown in the curve in Fig. 4. In the ANAND model, the primary creep contribution was considered to be reached instantaneously and for this reason was not selected for this study. With the emergence of SAC alloys, it has been shown that primary creep is not negligible and should be included in the calculation [3]. The Time Hardening Creep model includes both the primary and secondary creep components [1], [3]. Equation (1) shows the constituent relationship between creep and the time and temperature components of stress.

Figure 4. Creep Curve

## III. Modeling

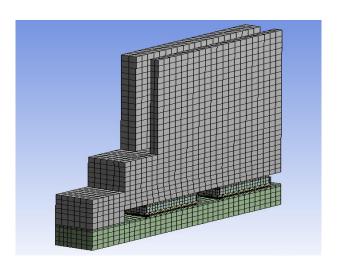

A full linear model of the four QFN's, heat sink, and board was developed and exercised from a stress free condition at

25°C to 0°C and then to 125°C, which is a typical ATC (Accelerated Thermal Cycle) used in reliability testing. Results were probed to determine regions of highest strain, and possible model reduction. Based on the linear model results, a quarter symmetry model was developed, regions of higher strain were refined with a higher element count, and the inelastic and creep material properties for SAC305 were introduced. The resulting mesh used for the non-linear analysis is shown in Fig. 5. The quarter symmetry model was first run, without creep properties, for one ATC cycle to evaluate the displacement in the system and the total strain realized in a critical joint. This critical joint, which we call the DNP (distance from neutral point) is illustrated in Fig. 6, which is a bottom view of the QFN. The model was exercised for two boundary conditions, one with the heat sink rigidly mounted which simulated the riveted assembly (no slip condition), and the other which simulates frictionless contact or lateral slip condition at the heat sink/PCB interface.

Figure 5. Mesh on Quarter Symmetry Model

Figure 6. Bottom view of QFN – DNP interconnect

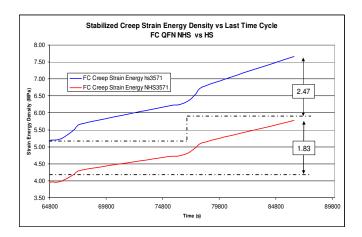

To evaluate the effects of creep on the interconnects, the full quarter symmetry model was run with the time hardening creep materials turned on. The model was cycled for four FC cycles with the heat sink rigidly attached and max creep strain energy density was recorded for the DNP interconnect for the last cycle. The creep strain energy density [4], [5] can be directly output from ANSYS and is recognized in the industry as a method to compare solder interconnect work done for various cyclical loading conditions. In this exercise the riveted heat sink condition is compared to the system without a heat sink, which is the ultimate condition for a heat sink mounted with lateral slip enabled at the heat sink/ PCB interface.

#### IV. Measurements

Measurements of the in-situ mounted system provided valuable insight into the thermal coupling of the riveted heat sink. Although it was assumed that a rigid connection was made by the rivets, DIC measurement revealed that there was some slip in the system. Even though slip is desirable to decouple thermal interconnect strain, protection against linear and rotational shock must be insured.

Fig. 7 is the measurement results of the riveted system at  $100^{\circ}$ C. The dashed lines indicate the rivet position in the PCB board with the solid short black and blue line above and below the dashed lines respectively indicate the position of rivets in the heat sink. The total in line displacement of 20um is what is expected by (1) wherein  $\Delta L$  (19um) is thermal expansion; L (43mm) is the distance between rivets;  $\Delta a$  (6ppm) is the CTE difference between PCB and heat sink, and  $\Delta T$  (75°C) is the temperature difference between a stress free state at 25°C and a measured temperature of  $100^{\circ}$ C.

$$\Delta L = L * \Delta a * \Delta T \tag{2}$$

## V. Results

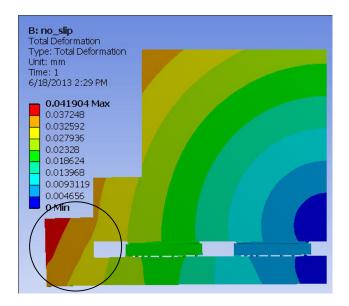

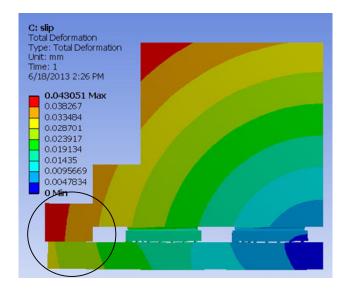

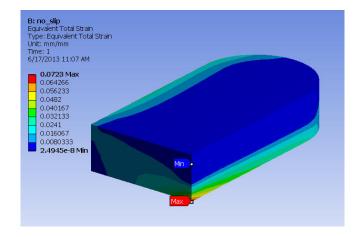

Figs. 8a and 8b show the deformation contour plots for the no slip and slip conditions (excluding creep) respectively for 100°C. We can see from the plot's circled area that the no slip condition drives a stronger coupling of the PCB, which is expected. However, it cannot be determined from these plots whether the coupling of the heat sink increases or reduces the strain in the solder interconnects.

Results for the total strain in the DNP joint present a clearer picture regarding heat sink coupling and subsequent strain increase. Maximum total strain for the no slip condition (Fig. 9) is 7.2% vs. 5.8% for the slip condition. Therefore

the presence of the heat increases the total strain in the DNP solder interconnect by approximately 25%.

Figure 7. DIC In-Line Slip measurement

When we include creep strain into the models and exercise them through four FC cycles we can extract the stabilized strain energy density (Work) for the last cycle and compare the results. As previously mentioned, we compared the rigidly mounted heat sink condition to no heat sink, which represents the idealized lateral slip condition. The graph in Fig. 10 is a plot of the delta work done, for the last cycle; in the DNP interconnect for both conditions. Comparing the results from the two cases, we see that the presence of the heat sink increases the work done by approximately 35% [=100\*(2.47-1.83)/1.83].

Figure 8a. No Slip – Total deformation

Figure 8b. Slip – Total deformation

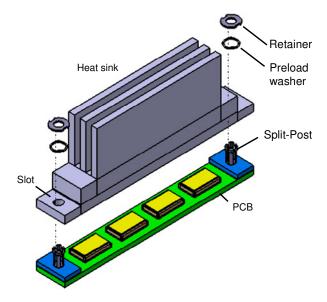

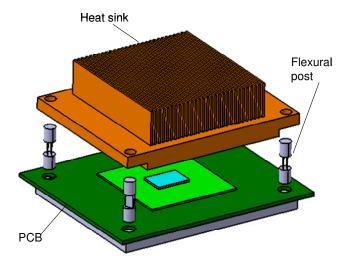

To mitigate the strain induced from the coupling of the heat sink, and thus improve cyclical life, it is essential to consider the heat sink mounting technique. One needs to consider heat dissipation, shock and vibration, when designing a heat sink that provides lateral slip to reduce strain coupling in the solder interconnects. Fig. 11 shows an in-line (two mounting points) that can satisfy these requirements.

Figure 9. No Slip - Total Strain

Figure 10. Field Condition Strain Energy Density

Figure 11. In-line heat sink lateral slip mounting concept.

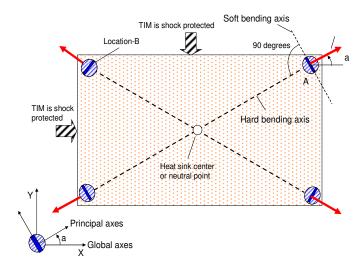

In this design methodology slip is allowed in the in line direction by virtue of the slot. A two or four leg split post, which can be fixed to the PCB, can be designed to eliminate radial clearance while providing the necessary stiffness to resist shock and vibration. The TIM can be functionally held between QFN and heat sink with the preload washer and retainer. The concept of providing lateral slip to heat sink mounting is not relegated to QFN type devices but can be extended to any high power device. For example Fig. 12 is a schematic which illustrates a method to provide compliance along the thermal expansion direction (i.e. diagonally) for a four point heat sink mounted device.

Figure. 12 Four point heat sink lateral slip schematic.

Thermally induced expansion is a radially driven coupling in a four point mounting system. As can be seen in Fig. 12, a soft axis is provided normal to the radial direction to provide for differences in expansion. This soft axis can be implemented in the form of a flexural design as shown in Fig. 13.

#### VI. Conclusion

High powered integrated modules are increasingly being used on PCB's used in electronic systems. These modules are typically surface mounted to the PCB using solder interconnects of various geometries. Critical to their life expectancy is the number of power on/off cycles the modules realize before failure. A common point of failure is the fatigue of the solder interconnects leading to cracking and eventual open circuits. Chip Package Interaction due to thermo-mechanical coupling, driven by CTE differences and thermal gradients, generates non recoverable inelastic strain in the solder interconnects leading to potential fatigue failure. Heat sinks that are necessary to dissipate the high

thermal energy, can lead to added inelastic strain in the solder interconnects. To reduce this added strain, a carefully designed heat sink mounting system providing thermomechanical decoupling should be considered. By providing lateral slip at the mounting points, while maintaining shock protection of the solder interconnect, a heat sink mounting can be designed to minimize interconnect fatigue life.

Figure. 13 Four point flexural concept.

# Acknowledgment

The authors would like to acknowledge the contributions of Jim Wilcox and Marie Cole, both of IBM Integrated Supply Chain for their support.

## Reference

- [1] K. Mysore, G. Subbarayan, V. Gupta, and R. Zhang, "Constitutive and Aging Behavior of Sn3.0Ag0.5Cu Solder Alloy," *IEEE Trans on Electronics Packaging Manufacturing*, Vol. 32, No. 4, October, 2009, pp. 221–232.

- [2] J. Pang, T. Low, B. Xiong and F. Che. "Design For Reliability (DFR) Methodology For Electronic Packaging Assemblies", Proc 6<sup>th</sup> Electronic Packaging Conf. Singapore, December, 2003, pp. 470-478.

- [3] D. Bhate, D. Chan, G. Subbarayan, Tz. Cheng Chiu, V. Gupta, and D. Edwards, "Constitutive and Aging Behavior of Sn3.8Ag0.7Cu andSn1.0Ag0.5 Alloys at Creep and Low Strain Rate Regimes," *IEEE Trans on Components and Packaging Technologies*, Vol. 31, No. 3,September, 2008, pp. 622- 633.

- [4] J. Pang and D. Chong "Flip Chipon Board Solder Joint Reliability Analysis Using 2-D and #-D FEA Models," *IEEE Trans on Advanced Packaging*, Vol. 24, No 4, November, 2001, pp. 499-506.

- [5] J. Lau and S. Pan, "Creep Behaviors of Flip Chip on Board With 96.5Sn-3.5Ag and 100In Lead-Free Solder Joints, "International Journal of Microcircuits and Electronic Packaging," Vol. 24, No. 1, First Quarter, 2001.

ANSYS<sup>TM</sup> is a trademark of ANSYS, Inc