# Automated Metrology Improves Productivity and Yields for Wafer Level Packaging in High Volume Manufacturing

Jin You Zao<sup>1</sup>, Bong Yin Yen<sup>1</sup>, Lim Beng Kuan<sup>1</sup>, John Thornell<sup>2</sup>, Darcy Hart<sup>2</sup>, David Marx<sup>2</sup>

<sup>1</sup>STATSChipPAC Singapore 5 Yishun Street 23, Singapore 768442

<sup>2</sup>Rudolph Technologies, Inc. 4900 West 78<sup>th</sup> Street Bloomington, MN 55435

Ph: +65-68241324 Email: youzao.jin@statschippac.com

Ph: +1-805-214-7052 Email: david.marx@rudolphtech.com

#### Abstract

Wafer Bumping In-line Process control of Wafer-Level Chip Scale Package (WLCSP) requires accurate measurement of bump features during processing. These bump features include critical dimension of Redistribution Layer (RDL), Under Bump Metal (UBM) and transparent polyimide thickness. For a 4-Mask Layer Cu plated WLCSP, accurate feature thickness measurement is required for both the Redistribution Layer (RDL) and Under Bump Metal (UBM) to ensure consistent delivery of good electrical performance and package reliability. This is especially important as WLCSP is moving towards finer feature size and pitch to meet increasing demand for smaller form factor.

This paper reports the development of an automated Critical Dimension (CD) measurement solution capable of measuring features at pre-defined locations on different topology both under sampling and full inspection mode on wafer. The solution is fully scalable to meet the requirement of high product-mix HVM environment, by highly adaptive to different features on different products for which measurement needs to be automated for effective process control.

#### **Key words**

Wafer Bumping, Critical Dimension (CD), Metrology, Redistribution Layer (RDL), Under Bump Metal (UBM), WLCSP, 3D Triangular Laser, Reflectometry, Visible Light Interferometry

#### I. Introduction

The demand for 4-Mask Layer Cu plated wafer level chip scale packaging (WLCSP) is increasing rapidly [1]-[2], and the current capability for in-line Cu height measurements is not suitable for high volume manufacturing (HVM). Thus, metrology constrains production capacity and limits volume ramp. Furthermore, the bottle neck created by a backlog of Cu step height measurements risks the timely detection of process drift and control. For a 4-Mask Layer Cu plated WLCSP, accurate Cu step height measurement is required for both the Redistribution Layer (RDL) and Under Bump

Metal (UBM) to ensure consistent delivery of good electrical performance and package reliability. This is especially important as WLCSP is moving towards finer feature size and pitch to meet increasing demand for smaller form factor.

The motivation behind the work presented here is to review current measurement methodology and derive an alternative measurement solution, with full automation capability, yet reliable and versatile enough for high mix production volumes. For quick-turn and high mix volume manufacturing, accurate and fast in-line monitoring is

crucial for timely process drift detection and control.

# II. WLCSP In-line Process Measurement Challenges

Contact-based Profilometers are commonly used in Wafer Bumping for measurement of metal features (RDL, UBM) thickness due to ease of usage as well as low cost of ownership. However, the method of measurement is largely semi-auto, and the identification of exact features and measurement locations is challenging. This becomes more acute under a high product-mix HVM environment, where measurement needs to be highly adaptive to different features on different products. As such, Contact-based Profilometers are limited to sampling measurements, and cannot perform 100% die inspection for process characterization.

It is thus desirable to have an automated feature measurement system capable of measuring features at precise locations on different topology both under sampling and full inspection mode on wafer.

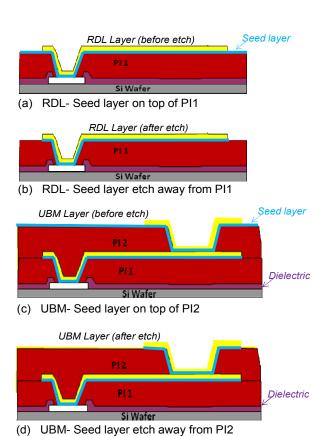

Specifically, feature measurement for Wafer Bumping comprises the following configurations (refer to Fig.-1):

- a) Cu RDL feature height measurement after Cu Electroplating, where the sputtered metal seed layer to enable Cu plating remains on the first layer polyimide surface

- b) Final Cu RDL feature thickness measurement on first layer polyimide surface (PI-1) after the Cu seed layer is etched away. Accurate Final Cu RDL thickness measurement would require a good gauging of the PI-1 thickness underneath, especially if the topology is not flat.

- c) Cu UBM feature height measurement after Cu Electroplating

- d) Final Cu UBM feature thickness measurement on second layer polyimide surface (PI-2)

The development for automated feature measurement proceeded in two phases: (Phase-1) Cu Step height highlight measurement on reflective metal surface, and (Phase-2) Cu thickness and polyimide thickness measurement on non-reflective surface.

Fig. 1: Wafer Bumping feature measurement configurations

### III. Phase-1: Auto Cu Height Measurement

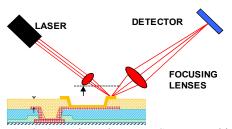

In this phase, the 3D Inspection (3DI) system used commonly for solder bump height (typically greater than 20um) measurement is explored for auto Cu feature height measurement. Typical 3DI system such as the Rudolph Wafer Scanner™ is equipped with the 3D Triangulation Laser Sensor (refer to Fig. 2). Triangulation Laser provides fast, precise measurements of bump height and coplanarity, where a laser is directed at the wafer surface at an angle of 45° and focused to a spot size of 8μm. Through a combination of laser-scanning and wafer movement, the beam scans the entire wafer surface. A lens collects the reflected/scattered laser light and focuses it on a position-sensitive detector.

Fig. 2: 3D Triangular Laser Sensor working illustration

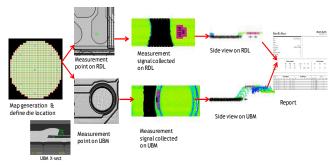

To enable Cu feature height (typically in the range of 2-20um) measurement, the Triangular Laser sensor is redesigned with a spot size of  $5\mu m$ , providing accuracy down to  $\pm 0.2 \mu m$ . The Laser scanning algorithm is also improved from an array to a stagger method to improve the repeatability of scanning signals. As Cu feature height measurement is influenced by the surrounding topology, the ability to select any datum of measurement will be critical. This is achieved through the integration of camera-based 2D inspection to the improved Triangular Laser Sensor System using the developed Datum selection program. An automated height measurement report can be conveniently generated for further analysis through the program (refer to Fig. 3).

**Fig. 3:** Selectable Datum for Cu feature Height measurement through Camera-Sensor integration

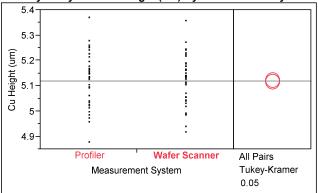

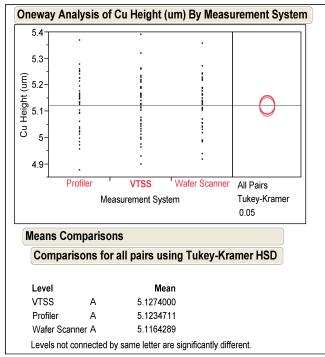

To verify the consistency of measurement performance, both the improvised 3D Triangulation Laser Sensor system and Contact Profilometer are used to measure feature Cu height on correlation device wafers. It is verified that the automated 3D Triangulation Laser Sensor system (represented by the Wafer Scanner<sup>TM</sup>) registers statistically similar Cu feature height mean compared to the manual Contact Profilometer (refer to Fig. 4) and at one-fifth of the measurement time taken by the latter. This illustrates Wafer Bumping facilities which already have existing pool of 3DI inspection tools such as the Wafer Scanner<sup>TM</sup> can be improvised to extend measurement application for Cu feature height without the need for excessive new investment.

# IV. Phase-2: Auto Cu/ PI thickness Measurement

While a strong signal can be derived using the 3D Triangular Laser signal for Cu feature height measurement after Electroplating (refer to Fig. 1, a & c), it is more difficult to establish a stable signal on Cu feature height measurement after reflective metal seed layer is etched away, and a reference datum needs to be taken on the remaining transparent polyimide surface (refer to Fig. 1, b

& c). Several conventional methods exist for non-contact measurement of step heights, such as various confocal sensors, triangulation sensors, and scanning white light interferometry. These sensors typically have difficulty differentiating between reflections from the top and bottom surfaces of a layer, that is, layer thickness. This limitation is from the depth of focus of the objective, which in turn depends on the numerical aperture (NA) of the objective. Thus, for all these techniques, sensor performance is highly dependent on objective lens.

#### Oneway Analysis of Cu Height (um) By Measurement System

**Fig. 4:** Oneway Analysis shows Cu Height measured done by improvised Wafer Scanner<sup>TM</sup> is comparable to Contact Profilometer on correlation device wafer

To overcome this technical constraint, it would be necessary to develop a metrology system that can measure concurrently the transparent layer thickness as well as the metal feature step height above the surface of the transparent layer. This can be achieved through the integration of reflectometry and visible light interferometry principles [3]. In this method, the direct reflection from the transparent layer provides direct thickness measurement of the transparent material, while the interferometry captures topography (distance from the sensor), allowing the system to measure the thickness of the opaque metals by scanning over the edge of the feature. This will be termed as the Visible Thickness and Shape Sensor (VT-SS) system.

Subsequent section of this paper provides further account of how such the VT-SS system can be adopted for feature height/thickness measurement on varying topology and opaque materials. For this purpose, the Rudolph Technologies NSX320 Metrology System configured with the VT-SS was evaluated.

## V. VT-SS system MSA Study

Measurement System Analysis (MSA) is to qualify a measurement system for use by quantifying its accuracy,

precision and stability. VLSI standard wafers with  $8\mu m$ ,  $24\mu m$ , and  $48\mu m$  step heights were used to assess Gauge Repeatability and Reproducibility (GR&R), Accuracy of the developed VT-SS system, as well as system correlation on two different NSX320 systems (tool matching) that are retrofitted with the VT-SS system.

#### A. GR&R

For the GR&R study, a total of ten parts on VLSI wafers (4 parts from 8um, 3 parts from 24um and 48um respectively) were measured three times each, including wafer loading and unloading.

Fig. 5 shows gauge R&R for VT-SS is 1.35% of tolerance and fully meeting AIAG standard of <10%.

**Fig. 5:** Measurement repeatability and reproducibility on ten different parts on VLSI wafers. The first four are from the  $8\mu m$  step height wafer, #5-#7 are from the  $24\mu m$  step height wafer, and #8-#10 are from the  $48\mu m$  step height wafer.

#### B. Accuracy

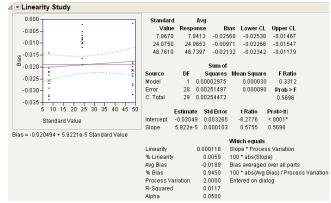

Step height measurement accuracy was evaluated by means of bias and linearity analysis using the VLSI step height wafers. For this study, one location on each standard wafer was measured ten times and compared to the VLSI specification for the wafer.

Based on the studies in Fig.6, measurement with VT-SS system shows an average bias of 0.95%, and linearity error of 0.0059%, meeting the AIAG standard of <5%.

Fig.6: Accuracy study on VT-SS with VLSI standard

#### C. Correlation of Multiple Systems

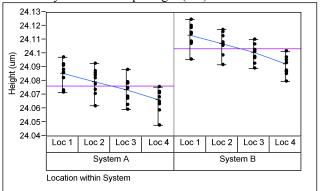

Having established VT-SS capability, the next evaluation is system correlation on multiple tools of the same configuration. The same VLSI wafers described above were measured on a second system with the same hardware configuration and software.

A summary of results are shown in Table I, and a detailed example of the  $24\mu m$  step height is shown in Fig. 7. For each wafer, the two systems produce similar results, with an offset that ranges from approximately 10nm to 30nm. Considering that the measurement uncertainty is on the order of 5nm (1- $\sigma$ ), the small system offset is within expectation.

**Table I:** Comparison of Measurements from Two Systems

|           |         | System A |           |             | System B |           |             |

|-----------|---------|----------|-----------|-------------|----------|-----------|-------------|

|           | Nominal | Average  | Ave Error | Max Std Dev | Average  | Ave Error | Max Std Dev |

| VLSI 8um  | 7.867   | 7.826    | -0.041    | 0.007       | 7.835    | -0.032    | 0.006       |

| VLSI 25um | 24.075  | 24.077   | 0.002     | 0.009       | 24.104   | 0.029     | 0.009       |

| VLSI 50um | 48.761  | 48.746   | -0.015    | 0.010       | 48.715   | -0.046    | 0.006       |

#### Variability Chart for Step Height (um)

Fig. 7: Comparison of  $24\mu m$  step height measurements from two different systems at the same four wafer locations. The measurement offset between the two systems is on the same order as the measurement repeatability.

### VI. VT-SS system application assessment

VT-SS system allows capturing of both the transparent polyimide thickness and opaque Cu feature height with a single scan from polyimide layer to Cu feature. From the part of the scan covering the polyimide, signals representing the direct measure of the polyimide thickness, the distance to the first surface of the polyimide, and the distance to a metal surface under the passivation stack are measured. The direct measure of the polyimide thickness is the measurement a standard spectroscopic reflectometer would produce. In that part of the scan where the sensor spot illuminates the Cu step height, the direct thickness peak and one of the distance peaks disappear. Only a distance peak to the surface of the Cu feature is present since the copper is opaque. The Cu step height above the first polyimide layer is then determined from the appropriate distance measures from each part of the scan. Thus, all the desired thickness and Cu thickness measurements are reported.

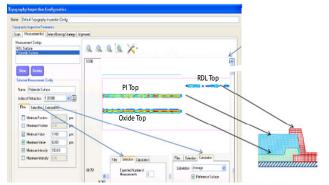

To aid interpretation of measured signal peaks, a visualization program is developed for automated generation of feature thickness. Fig.8 provides an illustration of the program interface for visualization of measured thickness. Raw data can be exported for further analysis.

Fig. 8: Program Interface for measured thickness visualization

#### A. VT-SS Cu RDL Layer thickness measurement

To assess VT-SS system's measurement performance on an actual device feature, it was used to measure Cu feature RDL thickness layer above the first polyimide (PI) layer (refer to Fig. 1, for a pictorial illustration) on a correlation device wafer. The measured RDL thickness is then cross verified with the actual measured Cu feature step height from Contact Profilometer and Wafer Scanner

Fig. 9 shows RDL thickness measured by VT-SS has no significant difference compared to Contact Profilometer and Wafer Scanner.

**Fig. 9:** RDL thickness as measured by VT-SS system correlates to Surface Profilometer and Wafer Scanner.

#### B. VT-SS Polyimide cum RDL layer Thickness

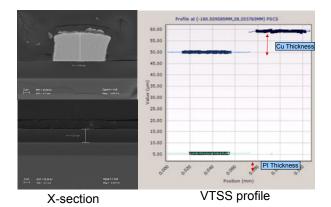

Further evaluation of the VT-SS system accuracy was through comparison with X-SEM measurements. X-SEM allows evaluation of both RDL step height and PI thickness (Fig. 1, b). As discussed above the measurement sensor has the unique capability to simultaneously measure step height, i.e. a distance measurement, and film thickness. Both types of measurements must be independently evaluated for accuracy.

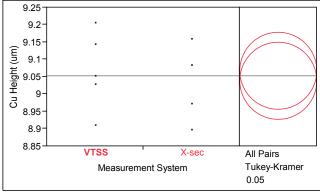

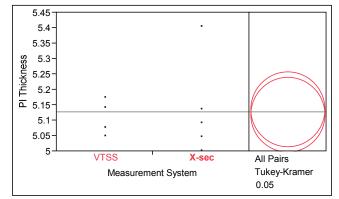

Fig. 10 shows the comparison of VT-SS measurements to X-SEM for RDL height and PI thickness measurements. For both types of measurements, the Tukey-Kramer analysis produced an alpha of 0.05, a positive result (Fig. 11 and Fig. 12).

**Fig. 10:** Side-by-side comparison of a X-SEM image and the VT-SS measurement results for Cu thickness and PI thickness.

**Fig. 11:** Tukey-Kramer analysis of Cu height measurement accuracy compared to X-SEM.

**Fig. 12:** Tukey-Kramer analysis of PI thickness measurement accuracy compared to X-SEM.

#### VII. Conclusion

This paper reports the development of VT-SS on a fully automated platform as a solution to Wafer Bumping in-line process measurement. This new metrology integrates both reflectometry and visible light interferometry principles. Based on MSA studies, VT-SS on a fully automated platform is a precise, accurate and fast metrology system. Engineering validations have shown VT-SS is highly capable in measuring critical dimensions such as RDL/UBM metal thickness, transparent polyimide/ passivation thickness, and feature sizes in one single step. It relieves the constraints of metrology tools for in-line process control, especially in a high mix, high volume production environment. This allows WLCSP production to move to new milestones of quality, yield, cycle time and productivity.

#### Acknowledgment

The authors would like to thank STATSChipPAC Singapore (SCS) Harry Kam for his sponsorship in this project, and other team members from SCS and Rudolph Technologies, Inc for supporting the development work.

#### References

- [1] Yole Développement, WLCSP Market & Industrial Trends: 2012, Jan2012

- [2] Robert F. Kunesh, "Wafer Level Chip-Scale Packaging: Evolving to Meet a Growing Application Space", Adv. Microelectronics, Jan/Feb 2013, Vol. No.1, pp14-16.

- [3] J. Schwider and Liang Zhou, "Dispersive Interferometric Profilometer," Opt. Lett., Vol. 19, p. 995, 1994.