# **Evaluation and Process Optimization of Heat-Curable Thermal Interface Materials for Advanced Packages**

Kevin Cox, Joanna Painter, Ghassan Abu-hamdeh, Steven Tonthat, Matt Borden, Jason Krantz

Tektronix Component Solutions Beaverton, Oregon, 97005 USA Ph: 503-627-5726

Email: kevin.cox@tektronix.com

#### **Abstract**

This research focused on evaluating 4 epoxy-based thermal interface materials for use between the ASIC and heat spreader in high-reliability flip-chip packages. The research methods included materials characterization, processing experiments and package builds. Experimental thermal conductivity measurements were performed using laser flash analysis on bulk and layered coupons to provide insight to interfacial thermal resistance. Layered samples incorporated two copper pads encapsulating the thermal interface material, thereby approximated a die-to-heat spreader interconnect. The best thermally performing material was incorporated into two different flip-chip package assemblies and exposed to solder reflow temperatures. The material was inspected for voids using confocal scanning acoustic microscopy. To achieve bondlines with low voiding, processing variables were studied including cure temperature ramp rate, cure pressure, and the inclusion of a pre-bake step before curing.

# **Key words**

Thermal interface material, voiding, flip-chip, laser flash analysis

#### I. Introduction

Since the arrival of flip-chip packaging technology, there has been a continuous push to reduce size, weight and power of these devices. While overall power consumption may be reduced, the power densities for individual chips increase as silicon interconnect densities increase. This is especially relevant today as the industry incorporates more chips in packages and adopts 2.5D and 3D package architectures. Providing adequate thermal solutions for these advanced architectures is becoming increasingly challenging.

High-reliability flip chip packages like those used in the MIL/AERO market require a thermal interface materials (TIM) that perform well both thermally (high thermal conductivity) and structurally (able to withstand stresses). Furthermore, the TIM needs to be fabricated with minimal voiding, survive 3x solder reflow conditions, and endure reliability testing including high-temperature high-humidity environments and ~1000 thermal cycles. The effectiveness of the TIM depends on its bondline thickness and contact area, its bulk thermal conductivity (TC), and the thermal resistance at the interfaces with other components. Interfacial resistance depends on the component mating surfaces and

phonon reflections arising from the mated component's material properties [1].

Many studies have been performed over the last 2 decades on processability (and voiding), thermal, and structural capabilities of TIMs. For example, the work in [2] describes the typical methods used to evaluate TIM in challenging environmental conditions and [3] discusses method to reduce voiding during processing. The influence of voiding on package thermal resistance was experimentally investigated in [4], and numerical evaluations were performed on variable void geometries in [5] – [7].

Recently, CSO has been approached by customers wanting to extend the use cases for their ASICs and/or existing CSO-designed packages. In some cases, this meant more harsh environmental conditions and in others, more chips in a single package. For both scenarios, there was an increased risk of exceeding critical thermal limits. Therefore, a drop-in, high-TC replacement for the legacy TIM was of great interest: to reduce peak temperatures while maintaining legacy package specifications (materials, dimensions, interfaces... etc.), processing methods and established component suppliers.

The work in this paper focused on evaluating four epoxybased TIMs for use in high-reliability flip-chip packages. The research methods included coupon fabrication, material thermal characterization with laser flash analysis, and package builds with evaluation of TIM voiding using confocal scanning acoustic microscopy (CSAM). Two packages were fabricated: one with a small (~4 mm) ASIC and the other with a large (~20 mm) ASIC. To achieve bondlines with low-voiding, processing variables were studied including cure temperature ramp rate, cure pressure and the inclusion of a pre-bake step before curing.

# II. Materials and Methods

#### A. Materials

Experimental characterizations were performed on four TIMs: two electrically conductive and two electrically resistive. TIM A (legacy) was an electrically insulative Alumina-filled epoxy with a TC of ~ 2 W/mK. It has been extensively used on the production line with many years of processing and reliability data. TIM B was an electrically insulative diamond-filled epoxy with a reported TC > 20 W/mK. TIM C and TIM D were both electrically conductive silvered-filled epoxies with reported TCs > 20 W/mK. All TIMs incorporated glass spheres with diameters ranging between 38 and 53 microns and concentrations ranging between 4 and 4.5% by weight. The objective was to evaluate TIM B, C and D as drop-in replacements for TIM A.

These TIMs had (supplier-published) bulk TCs ranging from 2 to greater than 20 W/mK. However, TC data reported from bulk materials testing does not always equate to package applications due to interfacial resistance and potential voids in the TIM [8]. Therefore, two types of coupons were fabricated for each TIM: one for bulk measurements, and another layered coupon designed to include interfacial thermal resistance. Further details are described later in this section.

#### B. Thermal Characterization Methods

The TC of each coupon was determined from experimental measurements of density ( $\rho$ ), specific heat ( $c_p$ ) and thermal diffusivity ( $\alpha$ ) using laser flash analysis as in:

$$k = \rho \cdot cp \cdot \alpha.$$

(1)

The specific heat was measured on each TIM bulk sample using modulated differential scanning calorimetry with TA Instruments Discovery DSC 25. Nitrogen was used as the purge gas, and a temperature profile between -15 and 40 C was used with a ramp rate of 5 C/min.

Thermal diffusivity was evaluated for each sample at 25 C using a custom laser flash apparatus [9]. A 10.6-micron wavelength CO2 laser was pulsed on the front side of each TIM sample. An HgCdTe infrared detector was used to measure the temperature of the back surface over time which allowed the half-rise time to be measured. A NIST graphite standard was used as a reference sample. The aperture of the

laser varied between 5- and 7-mm. Thermal diffusivity was then calculated using the measured thickness and half-rise time for each sample. Next, TC (k) was calculated using (1).

#### C. Material Test Coupon Fabrication

Two coupon samples were fabricated for each of the four TIMs: a bulk sample for measuring bulk TC and a layered sample to include the influence of interface resistance on the effective TC. The layered samples consisted of two electrolytic Ni/Au-plated Cu pads encapsulating a TIM bondline, thereby approximating a die-to-heat spreader thermal interconnect. The Cu pads were cleaned with acetone and a 20-minute plasma clean before epoxy dispense. TIM was manually deposited onto one Cu pad with a pneumatic dispenser and a second Cu pad was placed on top. The sandwich was then placed into a fixture to control pad parallelism and to set the bondline to ~80 microns. The coupon/fixture was ramped to the cure temperatures and profiles described on the respective TIM datasheets.

Bulk samples were created by covering the fixture surfaces with (anti-stick) UHMW tape to allow release of the cured epoxy coupons. A 15mm ID washer was used inside the fixture to set the coupon shape and thickness. Epoxy was dispensed inside the washer ID to create disc-shaped coupons.

The coupons fabricated using TIM A, C and D yielded low voiding in both bulk and layered samples and were acceptable for thermal characterization testing. However, the first trials of the diamond-filled TIM B coupons exhibited excessive voiding that were unacceptable for testing and required further process experimentation.

The processing experiments for TIM B were performed using a copper plate on one side of the TIM and a glass slide on the other to allow for easier visual inspection before and after cure. The glass slide dimensions were 21 x 21 mm (matching the ASIC dimensions described later). The following parameters were investigated: the temperature ramp rate (R), the pressure applied by the lidding fixture (P) during cure, and the influence of a pre-bake step before curing. The ramp rate was varied between 1 and 10 °C/min and the pressure between 5 and 12 psi. Experiments were performed for three different pre-bake scenarios. The 1st scenario did not include a pre-bake. The second scenario (Enclosed Pre-Bake) included a 2-hour pre-bake at 60 C, after which the sample was processed through the standard cure cycle. For these samples, the TIM was dispensed and compressed by the glass slide before pre-bake. In the third scenario (Open Pre-Bake), the TIM was dispensed and not compressed by the glass slide until after the pre-bake so that the TIM was exposed to the open-air environment. This was done to allow any outgassing a clear path to escape before being enclosed/locked in by the glass slide. Results from these TIM B coupon processing experiments are presented in section III.

### D. TIM in Package Evaluation

materials characterization, the TIM incorporated into CSO designed flip-chip packages. The focus of the experiment was to evaluate TIM voiding during cure and after flip-chip post processing (3x solder reflow). During cure, voids can be created in the TIM due to trapped air bubbles in the epoxy or dispense pattern, inadequate dispense volume, outgassing, or poor surface wetting to mating components. Furthermore, the heat spreader attach process on a package is different than what was done to create the TIM coupon test samples. For these packages, solder reflow temperature was 220 C. In addition to material degradations that may occur at these high temperatures, the 200 C change in temperature when cooling to room temperature places high stress on the TIM. If the stresses are large enough, the TIM could delaminate creating areas of non-contact and poor TC – similar to voids. Evaluation of the voids (and delamination) in the package was done (with CSAM) after curing and after reflow.

Experiments were performed on two flip-chip packages with organic substrates, copper heat spreaders and 750-micron thick ASICs. Package 1 die size was 3.6 x 4.1 mm and Package 2 die size was 21 x 21 mm. It was necessary to consider a large range in die size for the TIM evaluation since this research was focused on finding a drop-in TIM replacement for the legacy material. Two samples of package 1 (small die) and package 2 (large die) were fabricated with TIM C (the only acceptable drop-in TIM based on TC measurements as discussed later in this paper). Standard flip-chip lidding tools were used which applied 5-10 psi pressure and the packages were cured with 1-2 C/min ramp rate.

# III. Results and Discussion

This section first discusses the results from the TIM B glass slide experiments to reduce voiding in the test samples, then presents the TC measurements of all four TIMs with the laser flash method. Finally results and evaluations of TIM C in the flip-chip packages are presented.

# A. Glass Slide voiding experiment for TIM B

Results from the glass-slide voiding experiments are shown in Table I. The images in the table are centered around the square glass slide with a viewing perspective through the glass into the TIM and the copper plate on the other side. TIM fillets can also be seen surrounding the glass. In the images, voids are represented by the darker grey/black regions. As shown in the images, the worst performing processes yielded large channels of voids with little contact between the TIM and glass. As the processing methods improved, the channels turned into a large number of individual bubbles and then into a small number of small bubbles for the best case. A slow ramp rate and the Open Pre-Bake process yielded the lowest voiding. In the absence of the Open Pre-Bake step, lower pressures also appeared to yield less voiding.

Table I: Glass-Slide voiding experiment summary for TIM B. R represents temperature ramp rate in °C/min and P represents cure pressure in psi. Images were captured with ontical camera

| optical c | optical camera. |          |          |  |  |  |  |

|-----------|-----------------|----------|----------|--|--|--|--|

| R/P       | No              | Enclosed | Open     |  |  |  |  |

|           | Pre-Bake        | Pre-Bake | Pre-Bake |  |  |  |  |

| 1/5       | (C)             |          |          |  |  |  |  |

| 1/10      | NA              |          |          |  |  |  |  |

| 2/5       |                 |          | NA       |  |  |  |  |

| 2/12      |                 | NA       | NA       |  |  |  |  |

| 10/5      |                 | NA       | NA       |  |  |  |  |

| 10/12     |                 | NA       | NA       |  |  |  |  |

The Open Pre-Bake process was important to allow the vaporization of volatiles in the resin to escape from the material instead of getting trapped by the glass slide and turning into a void. Having achieved a low void percentage for each of the TIMs, the coupons were then fabricated for TC measurements.

# B. Materials Characterization

The results from the experimental TC tests are presented in Table II alongside the (approximate) advertised TC values from supplier datasheets.

Table II: TIM Thermal Conductivities

| TIM | Electrical | Filler  | Thermal Conductivity (W/mK) |      |         |

|-----|------------|---------|-----------------------------|------|---------|

|     |            |         | Data Sheet                  | Bulk | Layered |

| A   | Insulating | Alumina | ~2                          | 1.7  | 3.1     |

| В   | Insulating | Diamond | >20                         | 0.6  | 0.8     |

| C   | Conductive | Silver  | >20                         | 21   | 12.5    |

| D   | Conductive | Silver  | >20                         | 4    | 4.8     |

Considering the bulk coupon TC measurements; TIM A and C yielded values in line with the reported data sheet values. TIM D produced significantly lower than expected

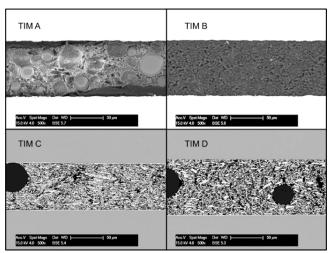

(data sheet) TC, while TIM B yielded very poor results. Evaluation of the coupon cross-sections provided insight into these results; the cross-sections for the layered coupons are presented in Fig. 1.

Figure 1: Cross sections of layered samples at 500x magnification

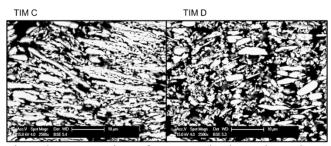

TIM C and D both had silver fillers with advertised TCs > 20 W/mK but produced very different results: TIM C was significantly higher. Closer investigation of the cross-section of these 2 materials in Fig. 2 showed a higher concentration of silver particles in TIM C. However, the concentration of filler particles is not the only factor driving the TC; the connectivity between the particles also has a major influence. At a certain concentration of silver particles, termed the percolation threshold, there were enough particles to create a continuous high conductivity path through the TIM [10]. As shown in Fig. 2, in addition to the higher concentration of particles, there was significantly more contact between particles – leading to the substantially higher TC of TIM C compared to TIM D.

Figure 2: Cross sections of TIM C and D layered samples at 2500x magnification

The poor performance of TIM B was also partly explained by the percolation. While the concentration of filler may have been acceptable, the particles (being diamond) were extremely hard with sharp edges and had little to no contact with each other and therefore, no thermal path. Furthermore, while diamond material has excellent thermal conductivity within the material, transferring heat into has its own challenges [11]. What resulted from the TC testing on TIM B was the result of little to no heat transferring between the epoxy and diamond fillers in addition to little to no heat transferring between particles.

The percolation threshold was different between bulk and layered samples because additional contact interfaces were needed to transfer heat between the silver particles and Cu pads. This explains why a decrease in TC was found for the TIM C layered sample. While this material achieved adequate percolation between silver particles, that was not the case at the Cu pad interface. All other layered samples however yielded higher TCs than their respective bulk samples. This could be explained by the following. The compression load applied during cure of layered samples was higher than that for the bulk samples. In addition, the bulk samples were thicker, leading to higher possibility for gaps between filler particles and lower TC. TIMs B and D likely did not achieve the percolation threshold in either coupon configuration, but the higher cure load and thinner bond line had a small positive effect on the TC. It was likely that TIM A did not achieve the percolation threshold in the bulk sample but did in the layered sample leading to an almost 2fold increase in its TC even after accounting for the Cu pad interfaces. Based on the TC evaluations, only TIM C was continued into and package builds for further evaluation as a replacement for TIM A.

#### C. Package Evaluation

Based on the experimental TC measurements, TIM C was clearly the best option as a drop-in replacement for TIM A and was therefore the only material included in package evaluations. Table III presents CSAM images of two samples of Package 1 (small die) and Package 2 (large die) before and after 3x reflow. Voids are represented by the darker grey regions. The void percentage for Package 1 was quite acceptable. However, the voids did appear to increase in size after 3x reflow. The void percentages for package 2 were much larger, covering up to 25% of the die area. Again, the void sizes grew after 3x reflow. Another interesting feature apparent in both Package 2 samples was the ring-shaped void near the die perimeter. This was likely due to package and component warpages that were much higher than in Package 1 due to the larger dimensions. This further complicates understanding the ideal pressure application during cure for large packages. The pressure must be high enough to spread the resin and create a thin bondline (for optimal TC) but be low enough to avoid flattening the package - which once the pressure is removed would induce high stresses on the TIM bondline and promote voids or delamination.

To reduce the voiding found with TIM C, an additional 2-sample glass slide experiment was conducted with the inclusion of an Open Pre-Bake step like what was done to improve TIM B coupons. The glass slide had the same dimensions as the Package 2 die (21 x 21 mm).

Table III: TIM C voiding in Package 1 and 2 before and after 3x Reflow. Images shown were captured with CSAM.

The glass slide method reduced the warpage issue (ring-shaped void) found in the Package 2 experiment, since the glass slide and heat spreader components were individually much flatter than Package 2. The Open Pre-Bake was for 20 minutes at 60 C, after which curing began at the 1-2 C/min ramp rate. Following cure, the samples were imaged with CSAM and then sent through 3x reflow. The results are presented in Table IV which shows that the open pre-bake, slow ramp and low-pressure cure yielded very low voiding for the TIM C glass slide experiment – as was the case for TIM B. Additionally, due to the low number and small size of voids, 3x reflow had minimal influence on the TIM. This method will be implemented to the Package 1 and 2 builds in the near future for further evaluation.

Table IV: TIM C voiding in Glass slied experiment with Open Pre-bake before and after 3x Reflow. Images shown were captured with CSAM.

|                | iurea with CSAM. |                 |

|----------------|------------------|-----------------|

| Glass<br>Slide | After Cure       | After 3x Reflow |

| 1              |                  |                 |

| 2              | •                | 7               |

# **IV. Conclusion**

Four epoxy-based TIMs were evaluated for thermal conductivity using the laser flash analysis method. The results were highly dependent on the type of test coupon (bulk or layered), the interfacial resistance, the filler particle material, and the filler particle distribution percentage and interconnectivity. CSAMs captured voids in the cured TIM which could be reduced by decreasing the cure ramp rate, adding a pre-bake step to expose the TIM to evaporate volatiles, and in some cases, modifying the cure pressure. The highest performing TIM was incorporated into two flipchip package designs (one with a small die and one with a large die) and exposed to package processing and solder reflow environments. Package warpage and pressure loads applied during TIM cure led to voiding challenges for the large-dimension package. Further work is being performed to reduce voiding and improve the reliability of this material.

Delivering best-in-class package designs and products requires detailed materials characterization and processing, package simulations, and physical product evaluations. Results from this work have been used in package and system-level thermo-mechanical simulation optimizations while ongoing experimental evaluations are focused on environmental survivability targets.

#### References

- [1] Hasselman et al., "Interfacial thermal resistance and temperature dependence of three adhesives for electronic packaging," *IEEE Transactions on Components and Packaging Technologies*, Vol. 23, No. 4, pp 633-63, 2000.

- [2] P. Kohli, M. Sobczak, J. Bowin, M. Matthews, "Advanced thermal interface materials for enhanced flip chip BGA," 51<sup>st</sup> Electronic Components and Technology Conference, Orlando, FL, 2001.

- [3] R. Zhang, V. Gupta, "Void control in die attach joint," *Solid State Technology*, Vol 61, No. 4, June 2018, pp. 20-23.

- [4] A. Gowda, D. Esler, S. Tonapi, K. Nagarkar, K. Srihari, "Voids in thermal interface material layers and their effect on thermal performance," 9th Electronics Packaging Technology Conference, Singapore, 2004

- [5] R. Kandasamy, A. Muhumdar, "Interface thermal characteristics of flip chip packages – A numerical study," *Appl. Therm. Eng.*, vol. 29, no. 5-6, pp 822-829, 2009.

- [6] B. Ramos-Alvarado, D. Brown, X. Chen, G. Feng, G. Peterson, "On the assessment of voids in the thermal interface material on the thermal performance of a silicon chip package," *Microelectronics Reliability*, Vol. 53, No. 12, pp 1987-1995, 2013.

- [7] K. Cox et al., "Characterization of heat-curable thermal interface materials and influence on package thermal performance (Accepted for publication)," ASME International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems, San Jose, CA, 2024.

- [8] T. Fullem, D. Rae, A. Sharma, J. Wolcott, E. Cotts, "Thermal characterization of thermal interface material bondlines, 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orland, FL, 2008.

- [9] ASTM Standard Test Method for Thermal diffusivity by the flash method, ASTM E1461-13(2022).

- [10] J. Harris, E. Rubel, R. Olivar, G. Carrasco, "Comparison of Bulk and Insitu Ag Epoxy Die Attach Thermal Performance," MEPTEC Thermal Conference, 2019.

- [11] E. Swartz, R. Pohl, "Thermal boundary resistance," Rev. Mod. Phys., vol 61, pp. 605-668, 1989.