# Chemistry and process considerations for the removal of residues for hybrid bonding

Phillip Tyler, Ian Cochran, Jonathan Fijal, and John Taddei

Veeco Instruments

Thomas Workman, Dominik Suwito, Guilian Gao, Gabe Guevara, Gill Fountain, Cyprian Uzoh, Jeremy Theil, and Laura Mirkarimi

Xperi Corporation

# Self Introduction

---

- Phillip Tyler

- Veeco Instruments

- Manager, Process Development Engineering

- 13+ years in wafer process development

- Georgia Tech's Institute for Electronics and Nanotechnology

- Harris Corporation (now L3Harris Technologies)

- Axion Biosystems

- Collaborators

- Thomas Workman and Laura Mirkarimi at Xperi

# Agenda

---

- Introduction

- Process Flows

- Experimental Setup

- Metrology

- Cleaning Equipment

- Results

- Initial Cleaning Investigation

- Blanket silicon test wafers

- Diced silicon test wafers

- Bonding test vehicle

- Bond Yield

- Electrical Yield

- Conclusions

# Introduction

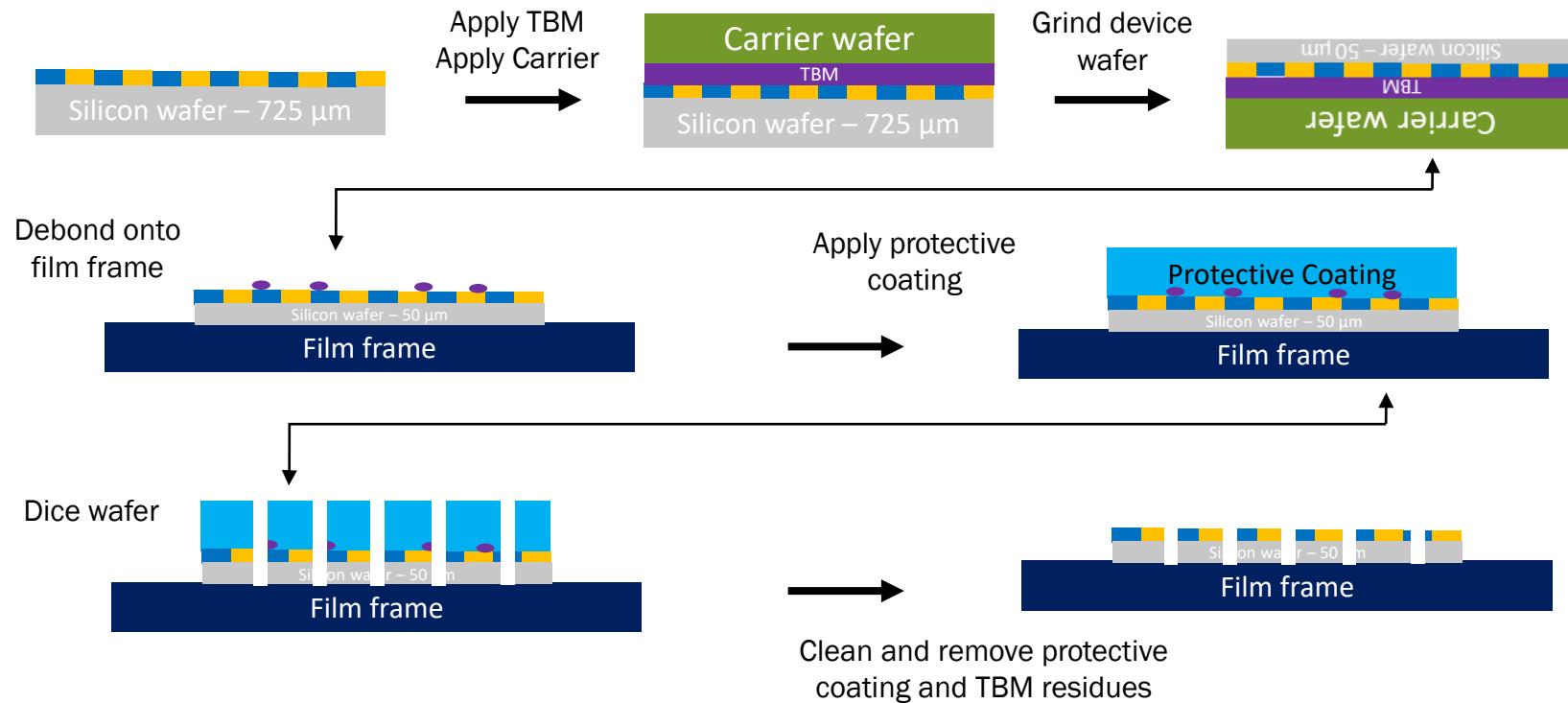

- Wafer dicing process generates a significant amount of debris that can be challenging to remove during or after processing

- Protective dicing coatings are used to protect the surface from this debris and is subsequently removed with solvents

- Temporary bonding material (TBM) residues can also be cleaned in this same step to reduce total process flow time

- This process flow is especially important in molecular die-to-die bonding

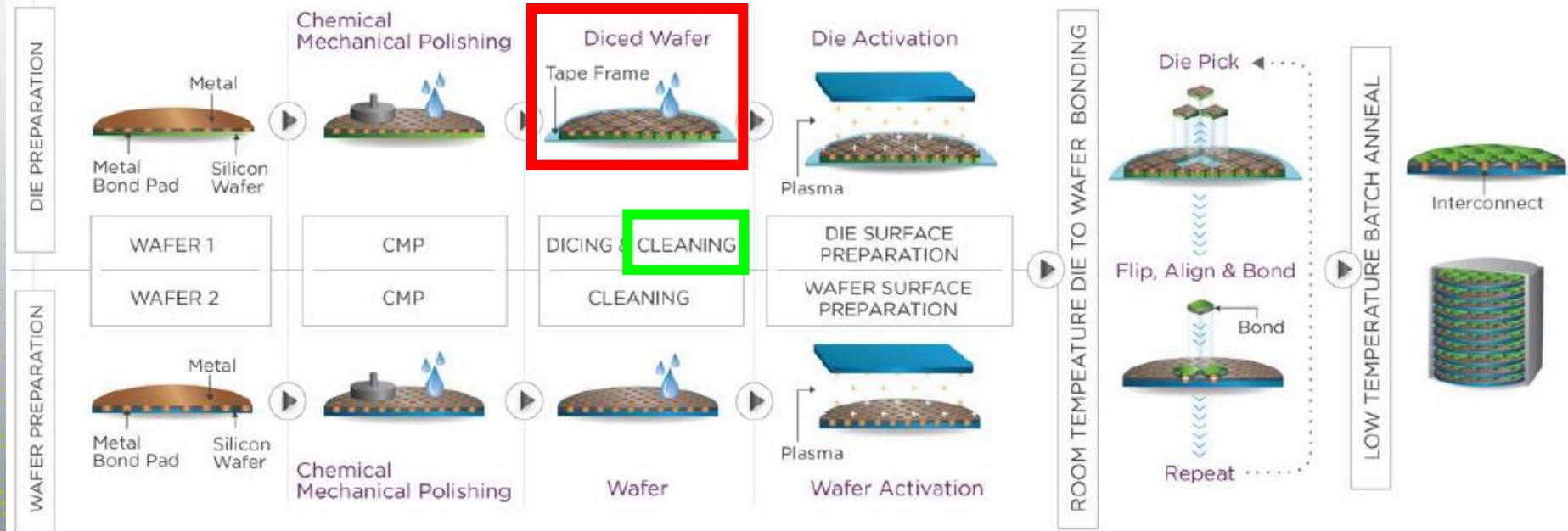

# Process Flow - Overview

- This investigation will focus on the cleaning of temporary bonding material (TBM) residues and protective dicing coatings (red box).

# Process Flow - Expanded

# Experimental setup and metrology

- KLA Tencor Candela CS20

- Surface defect Inspection

- Four bins of interest

- 0.32-1.0  $\mu\text{m}$

- 1-5  $\mu\text{m}$

- 5-28  $\mu\text{m}$

- >28  $\mu\text{m}$

- Only capable of scanning full thickness silicon wafers

- Besi Datacon 8800 CHAMEO bonder

- Bond's daisy chain test die to substrate

- Alignment accuracy of +/- 3  $\mu\text{m}$  at 3 $\sigma$

- ISO 3 (Class 1) Clean Kit installed

- Sonoscan Gen7 C-SAM

- C-Mode Acoustic microscope

- Die to substrate void inspection

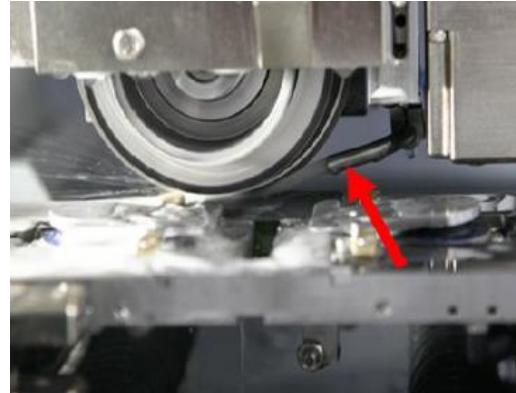

# Cleaning Equipment

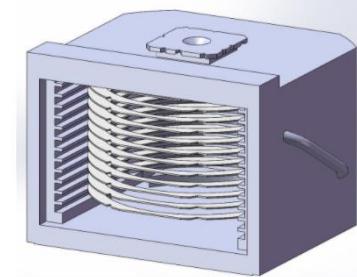

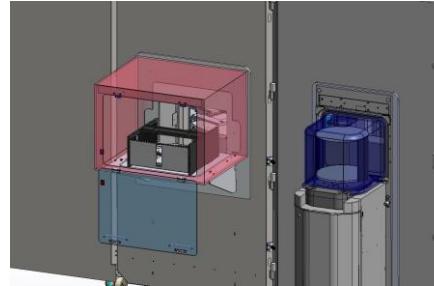

- Veeco WaferStorm® 3300 Series Platform

- Used to remove protective dicing coating and TBM residues

- Features

- Film frame processing capable

- Specialized hardware (chucks, end effectors, etc.) designed specifically for film frames

- Dry in/dry out processing

- Filtered and recirculated chemistry lower cost of ownership

- Immersion of film frames is also available

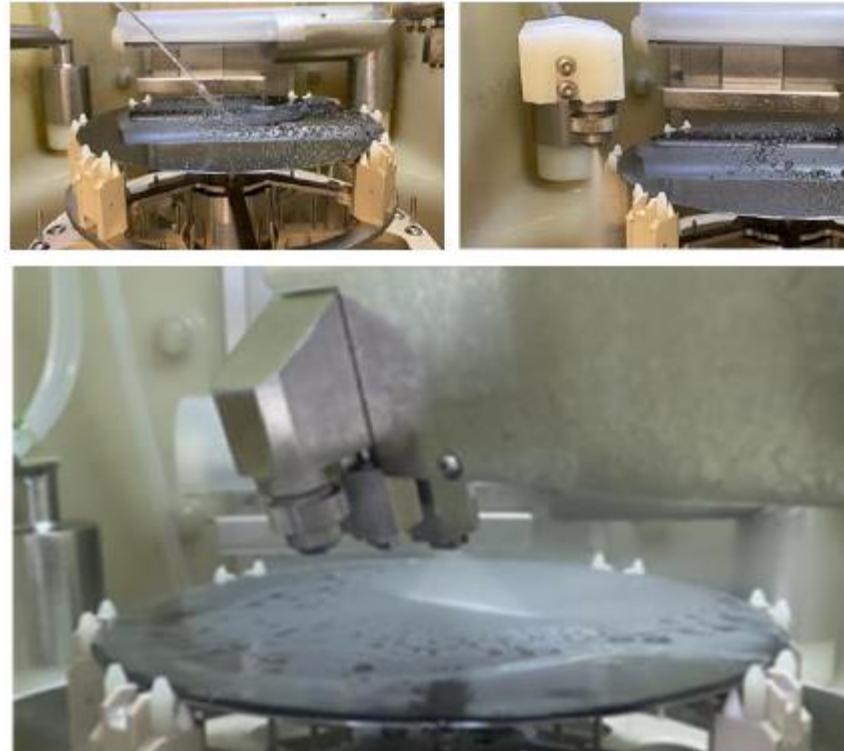

# Results - Initial Cleaning Investigation

- Test silicon wafers subjected to a simulated temporary bonding/debonding process and protective photoresist was applied

- Four different cleaning techniques investigated

- Wall mounted chemical dispense

- High velocity spray (HVS) chemical dispense

- High pressure chemical (HPC) fan spray

- HPC fan spray with wall mounted chemical dispense

# Results - Initial Cleaning Investigation

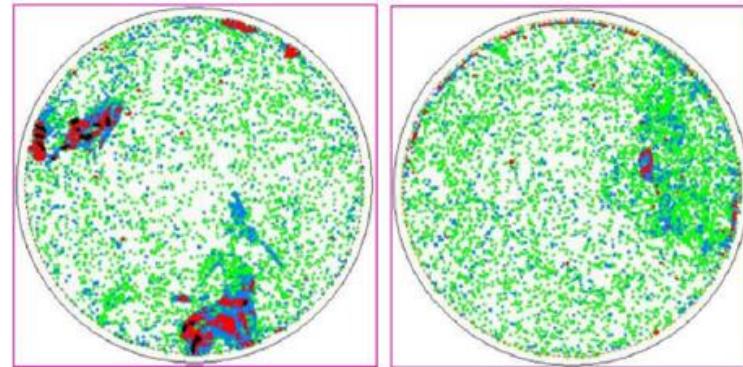

- Preliminary investigation to see which cleaning techniques had biggest impact

- Wafers scanned on KLA CS20 with below bins

- 0.32-1.0  $\mu\text{m}$

- 1-5  $\mu\text{m}$

- 5-28  $\mu\text{m}$

- >28  $\mu\text{m}$

- Cleaning efficiencies of >95% are possible with further optimization

- Highest efficiency achieved with HPC Fan Spray + Wall Dispense

- Focus shifted towards bonding and electrical yield

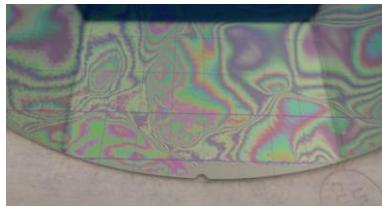

Sample defect maps before cleaning

| Technique                     | Cleaning Efficiency |

|-------------------------------|---------------------|

| Wall Dispense                 | -11%                |

| HVS                           | 27%                 |

| HPC Fan Spray                 | 77%                 |

| HPC Fan Spray + Wall Dispense | 86%                 |

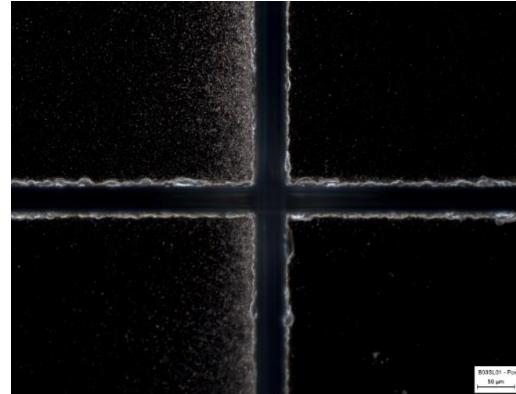

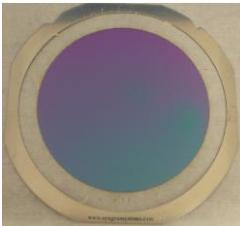

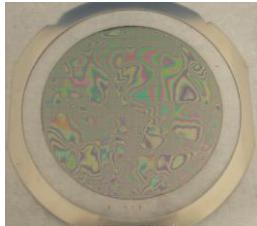

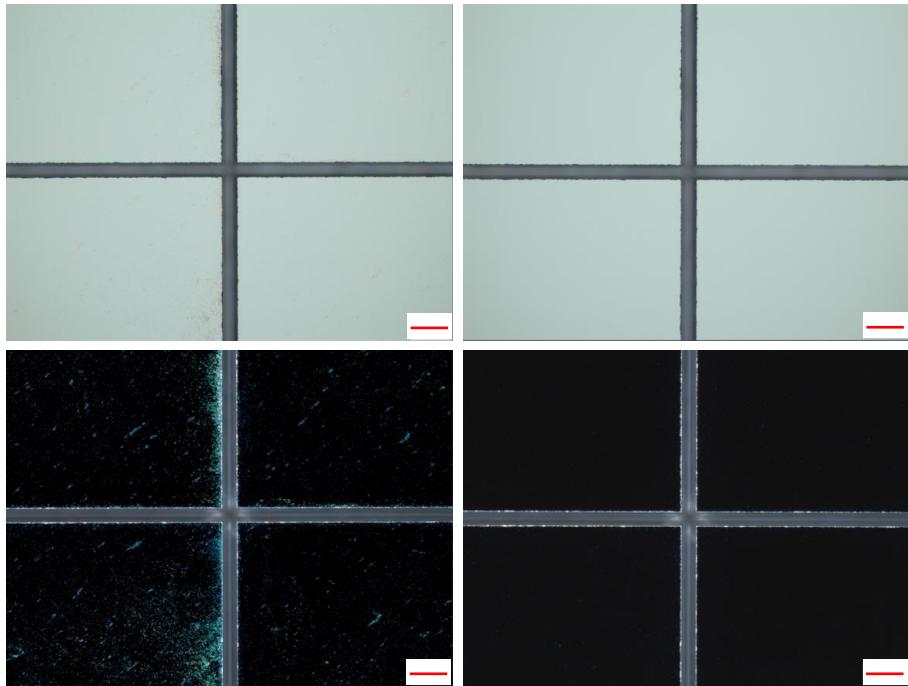

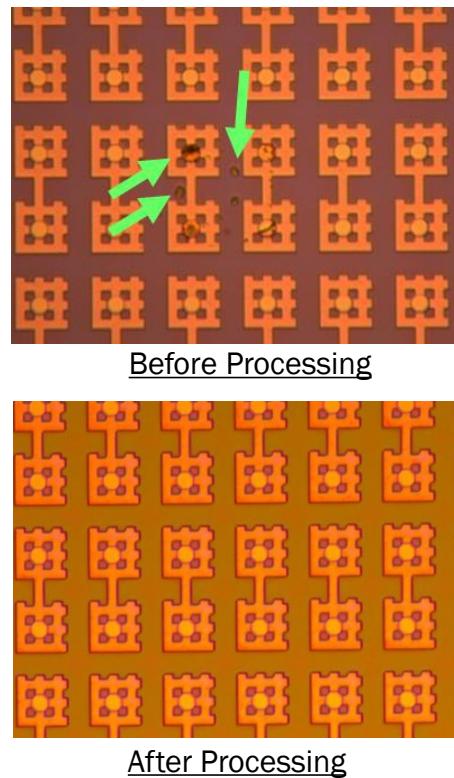

# Results – Diced Silicon Test Wafer

Before Processing

After Processing

Before Processing

After Processing

Mag: 10X, Scale bar: 100µm

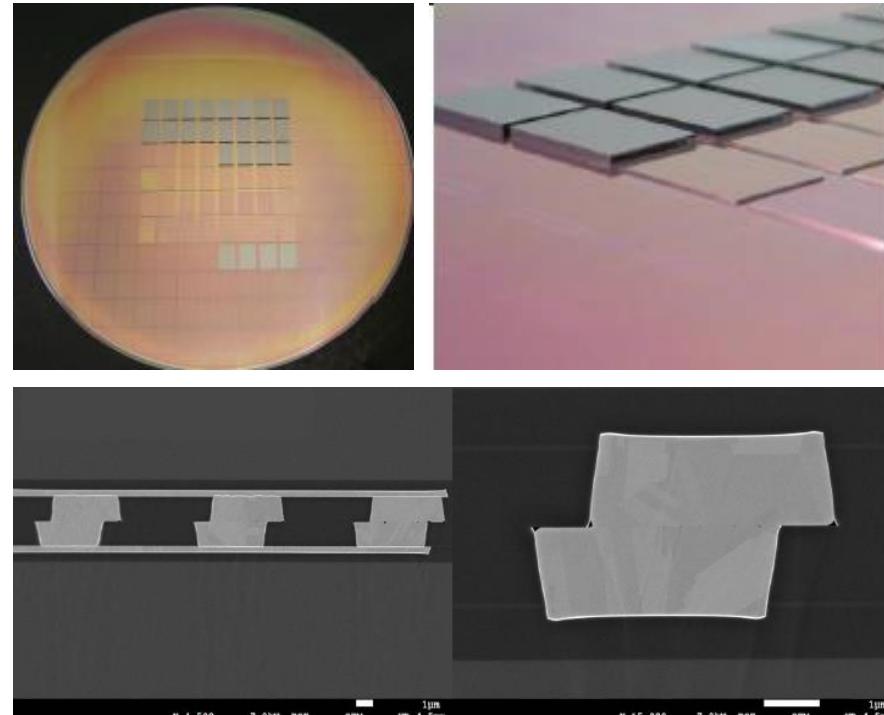

# Results – Bonding Test Vehicle

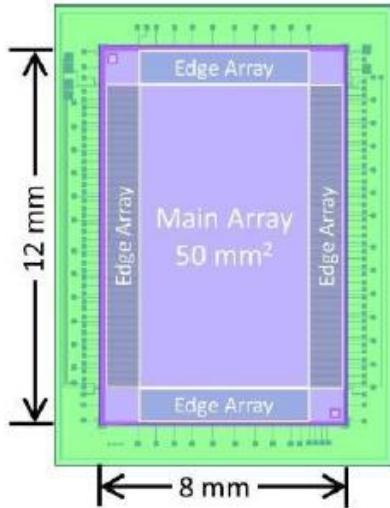

- Daisy chain design used for bonding die to substrate

- Allowed electrical yield evaluation with flying probe and bonding yield evaluation with CSAM

- Design description

- 2 layers – RDL and bonding pads

- Pads: 10  $\mu\text{m}$

- Pitch: 40 $\mu\text{m}$

- 31,356 electrical connections in main array

- 3400 connections in edge arrays

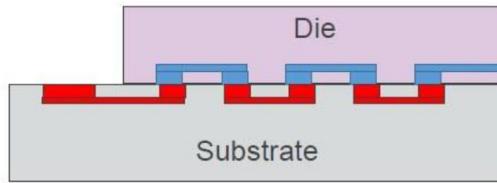

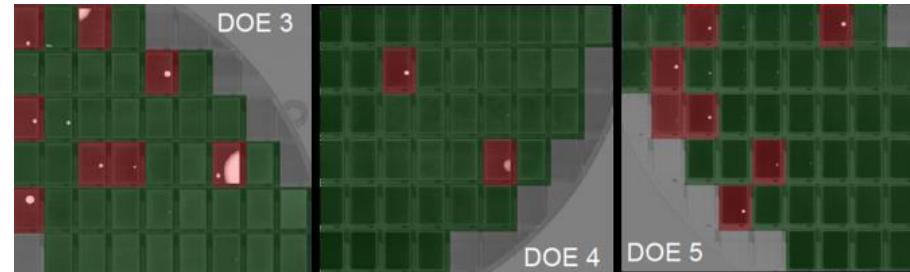

# Results – Bonding Yield

- Chemical needs to remove both photoresist and temporary bonding residues

- Chemical Composition

- Surfactant concentration

- Active resist remover concentration

- Considerations

- Film frame material

- Tape composition

- Wafer compositions (metals, dielectrics, etc.)

- 42 daisy chain die were bonded to the substrate for each clean condition

- C-SAM images show minimal voids

- Void free yield indicates the two chemicals investigated are comparable

| DOE | Chemical | Void Free Yield |

|-----|----------|-----------------|

| 3   | A        | 93%             |

| 4b  | B        | 91%             |

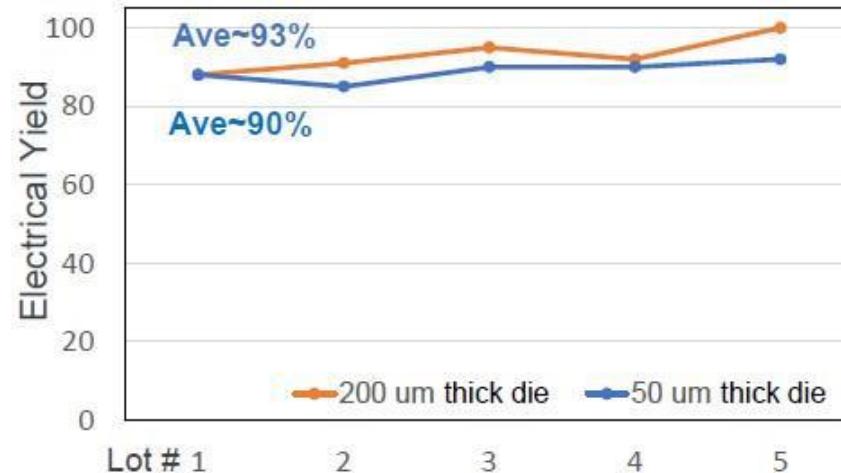

# Results – Electrical Yield

| DOE | HPC Fan Spray Pressure | Rotational speed | Electrical Yield |

|-----|------------------------|------------------|------------------|

| 3   | High                   | High             | 81%              |

| 4   | Low                    | Low              | 95%              |

| 5   | Low                    | High             | 83%              |

- DOE with HPC Fan Spray pressure and rotational speed

- Fan Spray range (300-3000 psi)

- Rotational speed range (50-1500 rpm)

- 42 daisy chain die were bonded to the substrate for each clean condition

- Bonding yield data overlayed with electrical yield data

- Clear correlation between bond yield and electrical yield

# Conclusions and Next Steps

- Complete protective dicing coating and temporary bonding material residue removal demonstrated on 200  $\mu\text{m}$  and 50  $\mu\text{m}$  thick die

- HPC Fan Spray + Wall cleaning techniques demonstrated highest cleaning efficiency in preliminary studies

- Early process results applied to bonding test vehicles produced high yields

- Bond free yield – 93%

- Electrical yield – 95%

- These initial cleaning results on a Veeco WaferStorm® are promising for use in manufacturing optimization.

Workman, et. al, "Cu interconnect scaling with hybrid bonding for 2.5 and 3D integration", IMAPS Device Packaging Conference, Scottsdale, AZ, March 2020

MAKING A **MATERIAL** DIFFERENCE