## Leveraging Glass Properties for Advanced Packaging

A.B. Shorey, Y.J. Lu and G.A. Smith

Corning, Incorporated

One Riverfront Plaza

Corning, NY USA 14831

Ph: (607)974-9007

Email: shoreyab@corning.com

---

### Abstract

Glass provides many opportunities for advanced packaging. The most obvious advantage is given by the material properties. As an insulator, glass has low electrical loss, particularly at high frequencies. The relatively high stiffness and ability to adjust the coefficient of thermal expansion gives advantages to manage warp in glass core substrates and bonded stacks for both through glass vias (TGV) and carrier applications. Glass also gives advantages for developing cost effective solutions. Glass forming processes allow the potential to form both in panel format as well as at thicknesses as low as 100 um, giving opportunities to optimize or eliminate current manufacturing methods.

As the industry adopts glass solutions, significant advancements have been made in downstream processes such as glass handling and via/surface metallization. Of particular interest is the ability to leverage tool sets and processes for panel fabrication to enable cost structures desired by the industry. By utilizing the stiffness and adjustable CTE of glass substrates, as well as continuously reducing via size that can be made in a panel format, opportunities to manufacture glass TGV substrates in a panel format increase. We will provide an update on advancements in these areas as well as handling techniques to achieve desired process flows. We will also provide the latest demonstrations of electrical, thermal and mechanical reliability.

### Key words

Glass; Through Glass Via (TGV); Interposer; Packaging

---

### I. Introduction

New initiatives in semiconductor packaging have created needs for new materials solutions. There has been substantial effort to extend interposer technology for 3D-IC stacking. Multiple solutions are being developed to address some of these needs including traditional interposers utilizing various materials as well as Fan-Out Wafer Level Packaging (FO-WLP), which has become a popular consideration in attempt to achieve lower cost.[1] Furthermore, the proliferation of mobile devices and aspirations such as the Internet of Things (IoT), leads to increasingly difficult requirements in RF communications. These include such requirements as the introduction of more frequency bands, smaller/thinner package size and need to conserve power to increase battery life as new functionality is

introduced. Glass has proven to be an excellent solution to these challenges. [2]

Glass has many properties that support the initiatives described above. These include high resistivity and low electrical loss, low or adjustable dielectric constant, and adjustable coefficient of thermal expansion (CTE). There has been much work in recent years as researchers demonstrate leveraging glass properties to achieve these objectives [3]-[6].

In order to leverage glass for many RF and interposer applications, it is often necessary to have precision vias for electrical interconnect and other functional purpose. The ability to put precision holes in glass and downstream metallization to create these vias continues to mature towards volume manufacture. Work in recent years has also

demonstrated the reliability of these structures in glass [7]- [9].

Over the past several years at Corning Incorporated, there have been significant advances in the ability to provide high quality vias in glass substrates of various formats. Examples are shown in Fig.1. The process employed provides the opportunity to leverage both through and blind vias in both wafer and panel format. The glass substrates with holes have been shown to give strength on par with bare glass, and filled vias have been shown to have excellent mechanical and electrical reliability after thermal cycle tests [9]-[11]. The approximate current best practice capabilities are summarized in Table 1 below. These represent guidance for the current TGV process, but in many cases the capabilities can be extended.

1a: Through Glass Vias

1b: Blind Glass Vias

**Fig. 1:** Examples of both through glass vias (TGV) and blind glass via (BGV).

**Table 1** TGV specification

| Attribute           | Current Capability* |

|---------------------|---------------------|

| Outer Diameter (OD) | 25 – 100 um         |

| Minimum Pitch       | ~2x OD              |

| Type                | Through and Blind   |

| Wafer Size          | Up to 300 mm        |

| Panel Size          | Up to 515 x 515 mm  |

| Thickness (mm)      | 0.1 – 0.7           |

\*Approximate.

In addition to enhanced technical performance, packaging solutions must also be cost effective. Glass forming processes such as Corning's fusion forming process, gives the ability to form high quality substrates in large formats ( $> 1$  m in size). The process can be scaled to deliver ultra-slim flexible glass to thicknesses down to  $\sim 100$   $\mu$ m. Providing large substrates in wafer or panel format at 100  $\mu$ m thickness gives significant opportunities to reduce manufacturing costs. The advantages given by Corning's fusion forming process for supplying substrates for electronics applications, has been previously reported [7], [8].

## II. Glass Material Properties

### A. Adjusting the CTE for Carrier and Interposer Applications

Glass material properties are determined by the specific constituents, making it possible to tailor glass composition to achieve a targeted CTE; thus enabling management of stack warp. Previously, we have shown examples of the material properties of two fusion formed glass types, in which it is possible to achieve very different CTE values while maintaining similar mechanical properties [7].

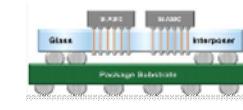

One of the important challenges in 3DIC stacking is reliability due to CTE mis-match and glass provides an excellent opportunity to manage warp of 3D-IC stacks but optimizing CTE. [6] Figure 2 gives an illustration of the challenge of stacking substrates with multiple CTE in an interposer application. Figure 2a schematically shows Si chips mounted on a Si interposer, which is then mounted on an organic substrate. The CTE mismatch causes failures when the substrates go through temperature cycles. However, if instead of a Si interposer, a glass interposer with CTE in between glass and organic is used, this warp can be better managed and increased reliability realized as demonstrated in work at Georgia Tech's Packaging Research Center (PRC) and illustrated Fig. 2b. [6]

2a: CTE mis-match creates reliability challenges.

2b: Utilizing the ability to adjust the CTE of glass helps to manage warp and improve reliability.

**Fig. 2:** Illustration of CTE mismatch in 3DIC stacking.

Another interesting example is to consider carrier applications. One of the driving forces to introduce glass carriers was that one could obtain glass with a very close CTE match to Si for thinning Si interposers for example. The transparency of glass allows features such as visual bond inspection and laser de-bonding that improves throughput.[13]-[14] As this approach matures into high volume manufacturing, the ability to adjust the CTE of the glass carrier has become increasingly important. Consider for example the FO-WLP process. A reconstituted wafer is formed by encapsulating Si

chips in high CTE molding compound. This structure will have a CTE much greater than Si in most cases and will depend on the materials and details of the layout of the package (size, thickness etc.). The CTE mismatch from the carrier and the fanout structure will result in excessive warp and make lithography steps extremely challenging. By utilizing glass carriers, the CTE can be optimized to minimize warp of the stack during FO-WLP processing resulting in higher quality fanout packages. Glass with CTE in the range of  $\sim 3.9$  ppm/ $^{\circ}$ C is available [15] and other CTEs are also possible depending on requirements.

### B. Electrical Performance

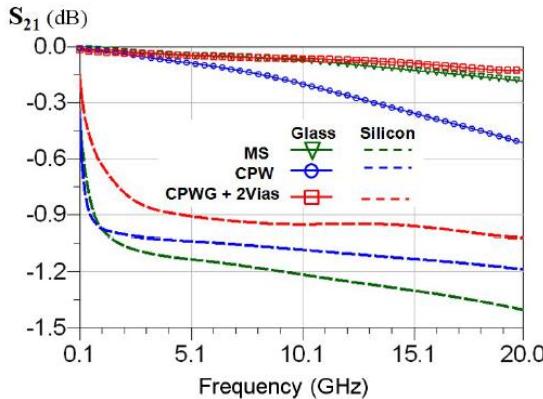

As new, higher frequencies used in RF applications are released, the electrical properties of the substrates become increasing important. As a semiconducting material, silicon tends to have increased loss at increased frequencies. Work done in collaboration with the Industrial Technology Research Institute (ITRI) in Taiwan illustrates this well. [16] In this work co-planar waveguides (CPW), micro-strip lines (MS) and co-planar waveguides with 2 vias were constructed on glass and silicon substrates, and impedance matched to  $\sim 50$  ohm. The structures were then tested up to 20 GHz and insertion loss was characterized. The results are shown in Fig. 2. Since glass is an insulator, there is much less loss as frequency is increased beyond a few 100's of MHz. Given the importance of minimizing power loss at these higher frequencies coupled with the need to continue to reduce package size, glass provides valuable material for all applications working in the GHz range.

**Fig. 3** – The insertion loss ( $S_{21}$ ) from transmission lines on glass and silicon substrates showing much

less loss in glass at higher frequencies.

### III. Form Factor

Another valuable aspect of leveraging glass as a semiconductor substrate is that the forming processes lend themselves to providing large form factors.[7], [8] This is important as the IoT will require billions and even trillions of devices and sensors. Being able to utilize economies of scale given by panel processing is very important.

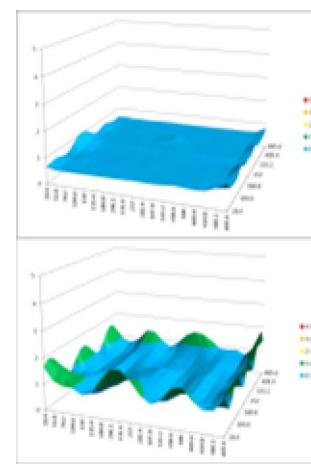

Recent work has shown significant progress in the ability to process glass panels  $> 500$  mm in size [17]. An important outcome of this work demonstrated one advantage of using glass in this application. Specifically, that the increased stiffness and thermal stability relative to current solutions results in improved flatness (See Fig. 4).

In Fig. 4a, the profile of a 508mm  $\times$  508mm panel size glass substrate with two layers build-up after pre-cure processes is shown. Figure 4b shows the profile of organic substrate after same processes. There was  $\sim 3x$  better warpage performance for the glass based substrate. This has important implications in that the improved flatness of the glass based substrate enables finer lines and spacing for redistribution layers relative to organic substrates. This allows high performance devices to be fabricated in a panel format, which provides substantial opportunity for both cost effective and high quality solutions.

**Fig. 4:** (a) Warpage measurement result of glass substrate after two layers build-up (b) Warpage measurement result of organic substrate after build-up

In addition to scaling glass substrate size, it is possible scale the process to deliver ultra-slim flexible glass to thicknesses down to  $\sim 100$   $\mu$ m (see

Fig. 5). Providing large substrates in wafer or panel format at 100  $\mu\text{m}$  thickness gives significant opportunities to reduce manufacturing costs because there is likely to be no need for grinding and polishing operations.

**Fig. 5.** Manufacture of high quality ultra-slim flexible Willow™ glass provides substantial opportunities to deliver substrates for TGV that do not require post processing.

#### IV. Thin Glass Handling

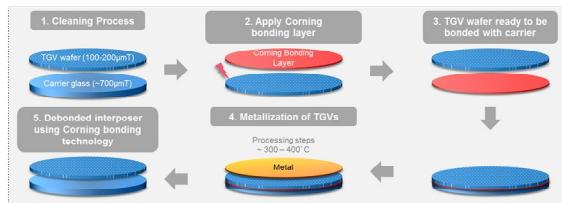

One challenge is handling of ultra-thin glass in standard wafer or panel processing operations, however, solutions are being developed. Corning's Advanced Lift-off Technology (ALoT) is a carrier based solution that is designed to be compatible with high temperatures ( $> 450 \text{ }^\circ\text{C}$ ) without outgas, as well as maintaining compatibility with important process chemistries such as cleaning (SC1, SC2, etc.) and metallization. The process is shown schematically in Fig. 6.

**Fig. 6.** Schematic showing an approach for handling thin glass through metallization.

The approach is to apply a surface treatment on a glass carrier wafer to prevent permanent bond at high temperatures, while maintaining enough adhesion strength to enable via and surface metallization. The thin metallized glass TGV wafer will then be mechanically de-bonded and processed further. This approach is relevant for panels as well as wafers.

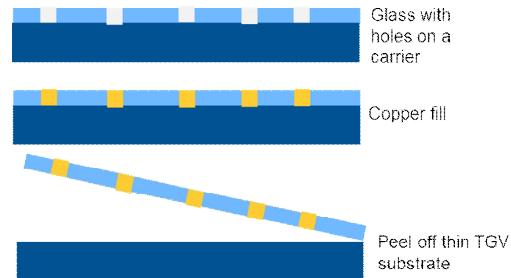

Work recently at RTI International in Research Triangle, NC has been done to demonstrate feasibility of utilizing the ALoT structure to perform metallization of the vias. 100  $\mu\text{m}$  thick glass with ~30 $\mu\text{m}$  diameter through vias was provided on a carrier. RTI then applied the seed layer and via fill

using a process consistent with the method used to fill blind vias.[9] However, instead of backgrinding to expose the bottom of the vias, with ALoT the thin glass is peeled off mechanically.

**Fig. 7:** Cartoon of leveraging ALoT technology to metallize through vias in 100  $\mu\text{m}$  thick glass.

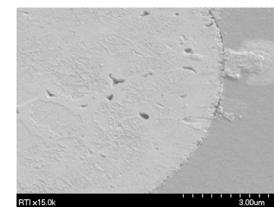

**Fig. 8:** SEM image of bottom of metallized via after de-bond (no polishing).

Figure 8 shows the result of an initial test to demonstrate feasibility of this approach. The vias were filled at RTI, mechanically de-bonded and an SEM image was collected to evaluate the ability to achieve good planarity without polishing. As shown in Fig. 8, there is work to be done to achieve perfect bond and planarity, but the result shows the feasibility of using this approach to effectively fill TGV in thin glass.

#### V. Conclusion

Glass has a number of properties that make it an exciting material for various packaging applications. The electrical performance of glass gives reduced electrical loss relative to silicon. This becomes even more important at high frequencies, which is the path likely to be taken for next generation mobile technology. The important implication would be the ability to increase smart phone functionality while maintaining battery life.

Adjusting material properties like CTE generates tremendous incentive for using glass as a TGV substrate for 2.5D and 3D applications in multiple

forms. Furthermore, the ability to form glass in thin, large sheets of high quality enables a number of opportunities to achieve cost effectiveness. Handling technologies that provide means to effective process ultra-thin glass are being demonstrated.

Well-formed through and blind via formation has been demonstrated and existing metallization technology can be leveraged to generate very good Cu filling performance in glass in both wafer and panel formats. Reliable performance of Cu-filled vias in glass has been demonstrated. These developments make glass an exciting material for next generation packaging applications.

## Acknowledgment

The authors would like to extend sincere thanks to their development partners at RTI International, Industrial Technology Research Institute (ITRI) and Georgia Tech's Packaging Research Center (PRC).

## References

- [1] S.W. Yoon, P. Tang, r. Emigh, Y. Lin, P.C. Marimuthu and R. Pendse, "Fanout Flipchip eWLB (embedded Wafer Level Ball Grid Array) Technology as 2.5D Packaging Solution", Electronic Components and Technology Conference (ECTC); (2013).

- [2] C.H. Yun, S. Kuramochi, A.B. Shorey, "Through Glass Via (TGV) Technology for RF Applications", *to be published in this volume.*

- [3] Kim, J., Shenoy, R., Lai, K-Y., Kim, J., "High-Q 3D RF Solenoid Inductors in Glass", Radio Frequency Integrated Circuits Symposium, *IEEE* 2014.

- [4] Shenoy, R., Lai, K-Y., and Gusev, E., "2.5D Advanced System-in-Package: Processes, Materials and Integration Aspects", *ECS Transactions*, **61** (3) 183-190 (2014).

- [5] Lai, WC et al., "300 mm Size Ultra-thin Glass Interposer Technology and High-Q Embedded Helical Inductor (EHI) for Mobile Application", International Electronic Devices Meeting (IEDM),(2013).

- [6] Qin, X., Kumbhat, N., Sundaram, V., and Tummala, R., "Highly-Reliable Silicon and Glass Interposers-to-Printed Wiring Board SMT Interconnections: Modeling, Design, Fabrication and Reliability", Electronics Components and Testing (ECTC), IEEE 62nd (2012).

- [7] Shorey, A; Pollard, S.; Streltsov, A.; Piech, G.; Wagner, R., Electronic Components and Technology Conference (ECTC), IEEE 62<sup>nd</sup> (2012).

- [8] Keech, J.; Piech, G.; Pollard, S.; Shorey, A., "Development and Demonstration of 3D-IC Glass Interposers", Electronic Components and Technology Conference (ECTC), IEEE 63rd (2013).

- [9] M. Lueck, A. Huffman, A. Shorey, "Through Glass Via (TGV) and Aspects of Reliability", Electronic Components and Technology Conference (ECTC), IEEE 65<sup>th</sup> (2015).

- [10] S. Hunegnaw, L. Brandt, H. Fu, Z. Liu, T. Magawa., "Adhesive Enabling Technology for Directly Plating Copper onto Glass/Ceramic Substrates", Electronic Components and Technology Conference (ECTC), IEEE 64<sup>th</sup> (2014).

- [11] Demir et al., "First Demonstration of Reliable Copper-plated 30 um Diameter Through-Package-Vias in Ultra-thin Bare Glass Interposers", Electronic Components and Technology Conference (ECTC), IEEE 64<sup>th</sup> (2014).

- [12] A. Shorey, S. Chaparala, S. Pollard, G. Piech and J. Keech, "Glass Interposer: Fabrication, Characterization and Modeling", IMAPS Device Packaging Conference (2014).

- [13] B.Dronen, A. Shorey, B.K. Wang, L. Tsai, "Production Proven, High Precision Temporary Bond/De-Bond Process", IMAPS Device Packaging Conference, (2014).

- [14] R. Chanchani, "An Overview – Temporary Wafer Bonding/DeBonding for 2.5D and 3D Technologies" IMAPS Device Packaging Conference (2012).

- [15] www.corning.com/semiglass

- [16] Chien et al., "Performance and Process Comparison between Glass and Si Interposer for 3D-IC Integration", IMAPS 2013.

- [17] YH Chen et al., "Low Cost Glass Interposer Development", 47<sup>th</sup> International Symposium on Microelectronics, San Diego, CA (2014).